LTC6952 Datasheet

Ultralow Jitter, 4.5GHz PLL with 11 Outputs and JESD204B / JESD204C Support

Ultralow Jitter, 4.5GHz PLL with 11 Outputs and JESD204B / JESD204C Support

| Part No. | In Stock | Price | Packaging | SPQ | Marking | MSL | Pins | Temp Range | Package Description |

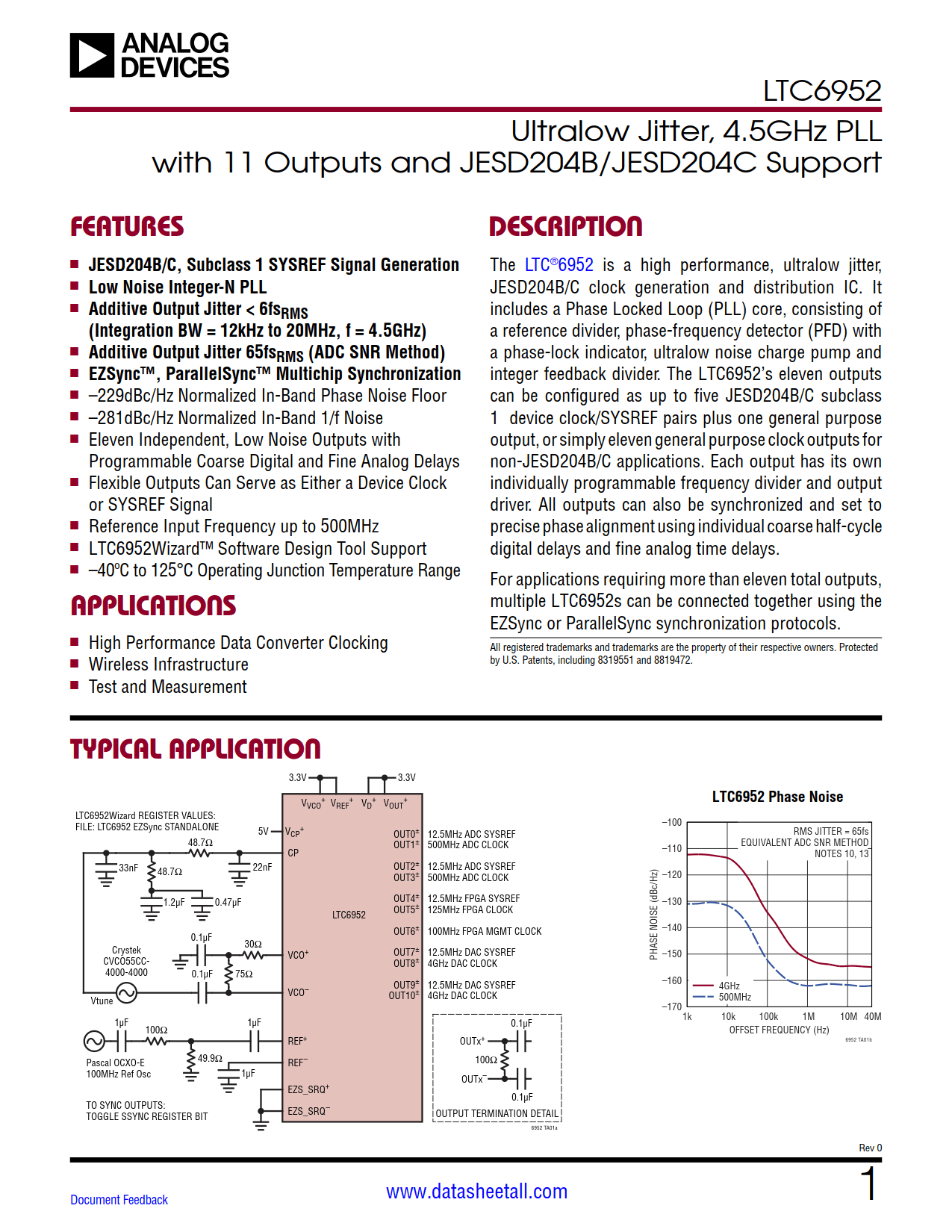

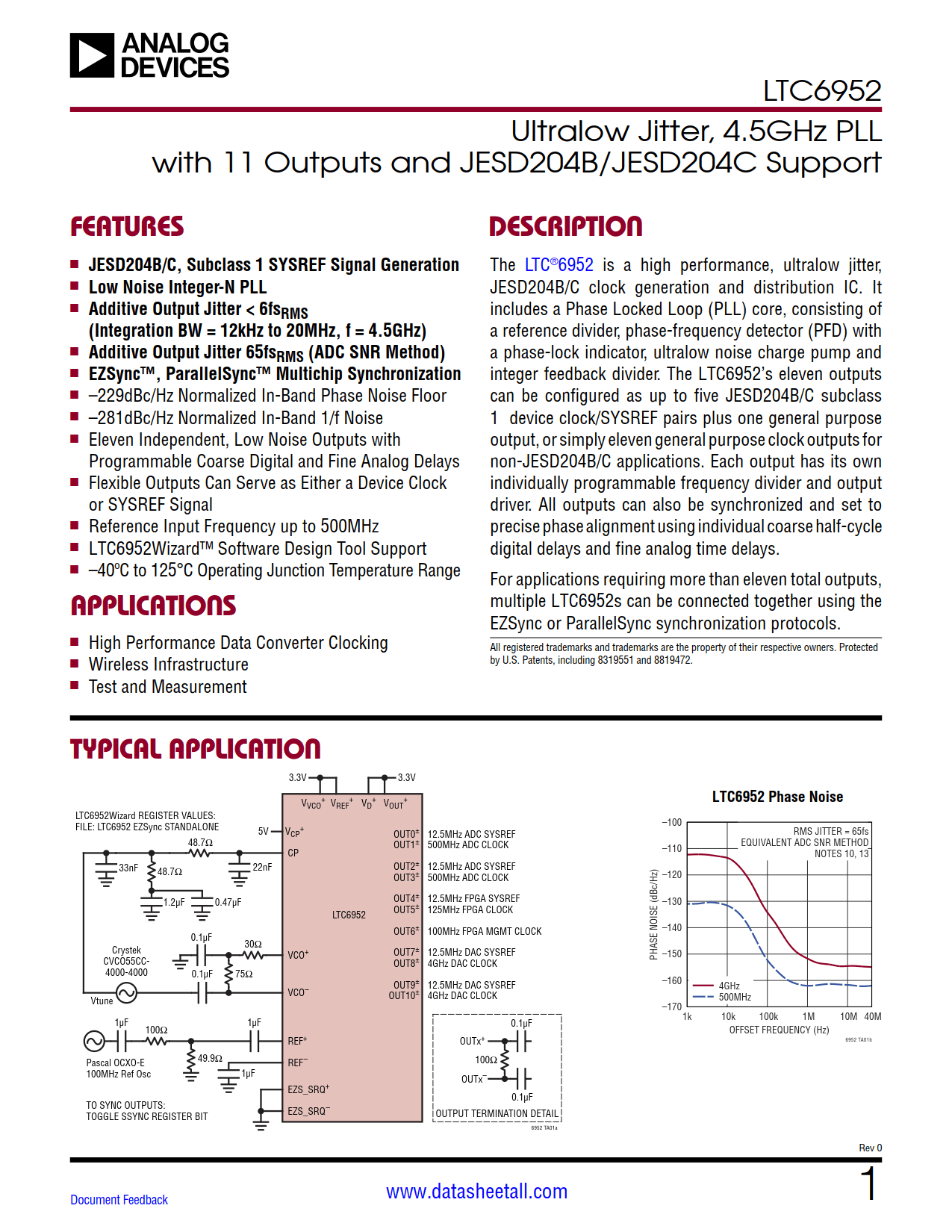

The LTC6952 is a high performance, ultralow jitter, JESD204B/C clock generation and distribution IC. It includes a Phase Locked Loop (PLL) core, consisting of a reference divider, phase-frequency detector (PFD) with a phase-lock indicator, ultralow noise charge pump and integer feedback divider. The LTC6952’s eleven outputs can be configured as up to five JESD204B/C subclass 1 device clock/SYSREF pairs plus one general purpose output, or simply eleven general purpose clock outputs for non-JESD204B/C applications. Each output has its own individually programmable frequency divider and output driver. All outputs can also be synchronized and set to precise phase alignment using individual coarse half-cycle digital delays and fine analog time delays.

For applications requiring more than eleven total outputs, multiple LTC6952s can be connected together using the EZSync or ParallelSync synchronization protocols.