ADSP-21061L Datasheet

SHARC, 44MHz, 150 MFLOPS, 3.3v, floating point

SHARC, 44MHz, 150 MFLOPS, 3.3v, floating point

| Part No. | In Stock | Price | Packaging | SPQ | Marking | MSL | Pins | Temp Range | Package Description |

| ADSP-21061LKB-160 | 0 | $0 | Tray | 60 | ADSP-21061LKB-160 | 3 | 127 | 0°C ~ 85°C | 225-Ball PBGA |

| ADSP-21061LKBZ-160 | 0 | $0 | Tray | 60 | ADSP-21061LKBZ-160 | 3 | 127 | 0°C ~ 85°C | 225-Ball PBGA |

| ADSP-21061LKS-176 | 0 | $0 | Tray | 24 | ADSP-21061LKS-176 | 3 | 127 | 0°C ~ 85°C | 240-MQFP-EP (32x32) |

| ADSP-21061LKSZ-160 | 0 | $0 | Tray | 24 | ADSP-21061LKSZ-160 | 3 | 127 | 0°C ~ 85°C | 240-Lead MQFP |

| ADSP-21061LKSZ-176 | 0 | $0 | Tray | 24 | ADSP-21061LKSZ-176 | 3 | 127 | 0°C ~ 85°C | 240-Lead MQFP |

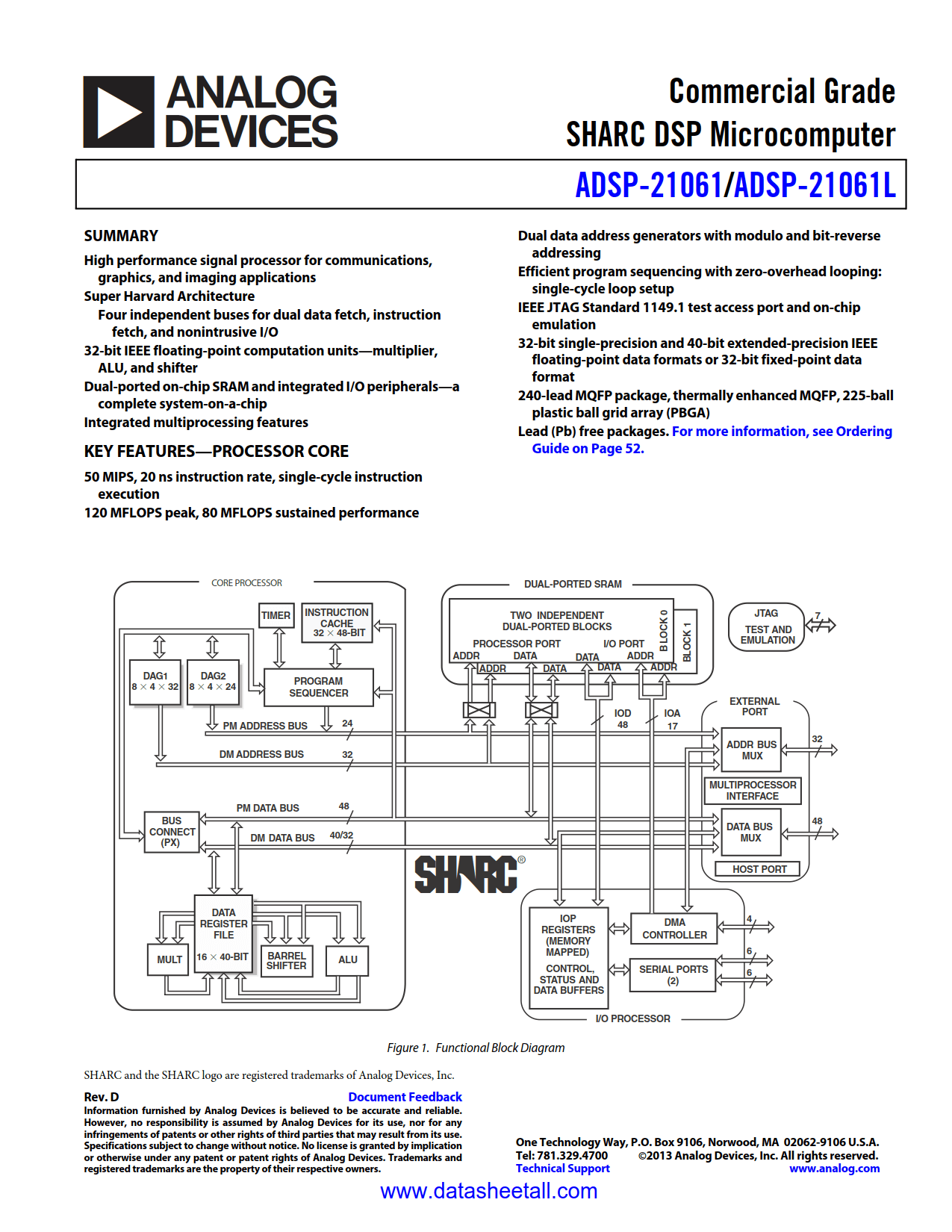

The ADSP-21061L is the newest member of the powerful SHARC® family of floating point processors. The SHARC® are signal processing microcomputers that offer new capabilities and levels of integration and performance. The ADSP-21061L is the low power (3.3 volt) version of the ADSP-21061. The ADSP-21061L is a 32-bit processor optimized for high performance DSP applications. The ADSP-21061L combines the ADSP-21000 DSP core with a dual-ported on-chip SRAM and an I/O processor with a dedicated I/O bus to form a complete system-in-a-chip.

Fabricated in a high-speed, low-power CMOS process, the ADSP-21061L has a 25 ns instruction cycle time operating at 40 MIPS. With its on-chip instruction cache, the processor can execute every instruction in a single cycle.

The ADSP-21061L SHARC combines a high-performance floating-point DSP core with integrated, on-chip system features, including a 1 Mbit SRAM memory, host processor interface, DMA controller, serial ports and parallel bus connectivity for glueless DSP multiprocessing.