AD9161 Datasheet

11-Bit, 12 GSPS, RF Digital-to-Analog Converters

11-Bit, 12 GSPS, RF Digital-to-Analog Converters

| Part No. | In Stock | Price | Packaging | SPQ | Marking | MSL | Pins | Temp Range | Package Description |

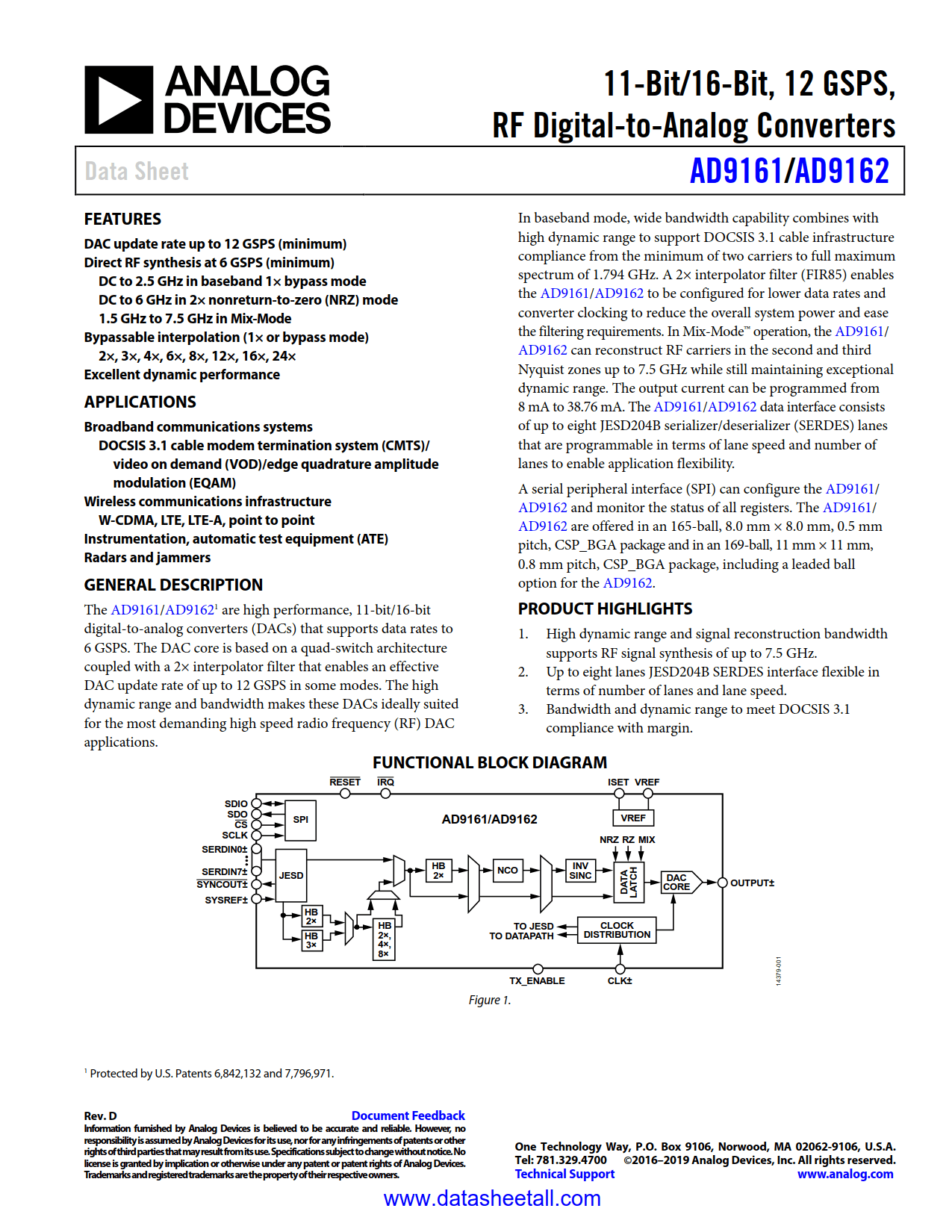

The AD9161 is a high performance, 11-bit digital-to-analog converter (DAC) that supports data rates to 6 GSPS. The DAC core is based on a quad-switch architecture coupled with a 2× interpolator filter that enables an effective DAC update rate of up to 12 GSPS in some modes. The high dynamic range and bandwidth makes these DACs ideally suited for the most demanding high speed radio frequency (RF) DAC applications.

In baseband mode, wide bandwidth capability combines with high dynamic range to support DOCSIS 3.1 cable infrastructure compliance from the minimum of two carriers to full maximum spectrum of 1.794 GHz. A 2× interpolator filter (FIR85) enables the AD9161 to be configured for lower data rates and converter clocking to reduce the overall system power and ease the filtering requirements. In Mix-Mode™ operation, the AD9161 can reconstruct RF carriers in the second and third Nyquist zones up to 7.5 GHz while still maintaining exceptional dynamic range. The output current can be programmed from 8 mA to 38.76 mA. The AD9161 data interface consists of up to eight JESD204B serializer/deserializer (SERDES) lanes that are programmable in terms of lane speed and number of lanes to enable application flexibility.

A serial peripheral interface (SPI) can configure the AD9161 and monitor the status of all registers. The AD9161 are offered in an 165-ball, 8.0 mm × 8.0 mm, 0.5 mm pitch, CSP_BGA package and in an 169-ball, 11 mm × 11 mm, 0.8 mm pitch, CSP_BGA package, including a leaded ball option for the AD9162.