# **High-Density Downstream Cable QAM Modulator**

### **General Description**

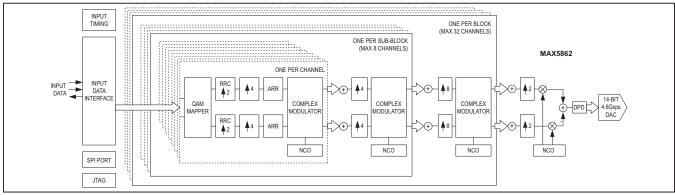

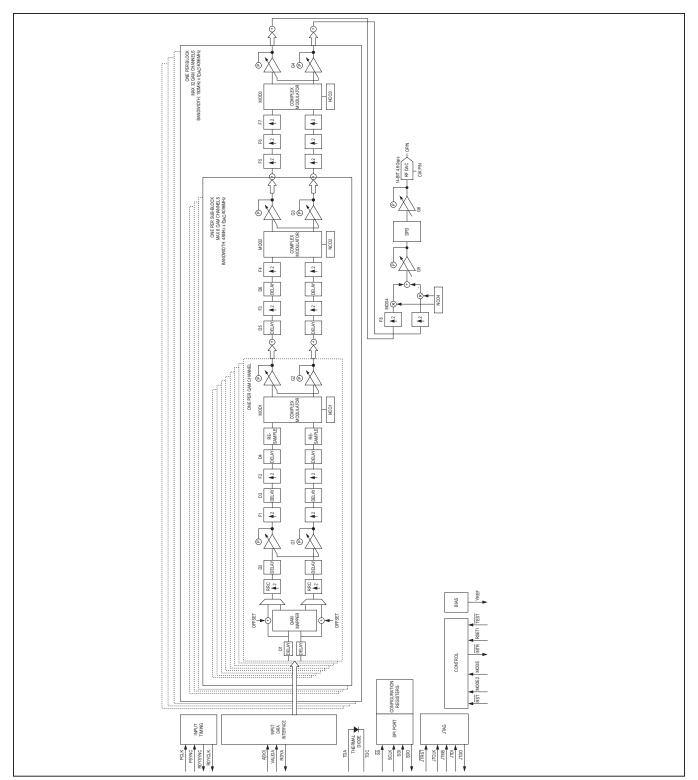

The MAX5862 is an integrated, high-density, downstream cable QAM modulator, digital upconverter (DUC) and RF digital-to-analog converter (RF-DAC). The device performs QAM mapping, pulse shaping and digital RF upconversion of forward-error-correction (FEC) encoded data with full agility and drives a single RF-port using a 14-bit 4.6Gsps DAC. The device digitally synthesizes RF signals with up to 32 DOCSIS-compliant 6MHz QAM or 8MHz QAM channels. The device has fixed QAM capacity and provides high-density QAM modulation with very low power dissipation (4.2W at 32 QAMs) in a compact 12mm x 17mm footprint.

The device accepts FEC-encoded CMOS data (symbols) on a single 10-bit input port that accepts up to 32 time-interleaved digital data streams. Each channel features an individually configurable QAM mapper, RRC filter, and arbitrary rate resampler (ARR). The device performs pulse shaping, resampling, interpolation and quadrature modulation of input data, supporting all data rates defined in DOCSIS 3.0 and DVB-C. A cascade of interpolation filters, complex modulators, and channel combiners allow modulation of the signal to any frequency from 47MHz to 1006MHz. Integrated direct digital frequency synthesizers allow positioning of the QAM channels with a resolution of 125Hz. The interpolation filters and resamplers provide linear phase and excellent gain flatness. Output data from the last modulator is fed to a digitalpredistortion (DPD) block that can be used to correct distortion in the device's integrated RF-DAC and output amplifiers external to the device.

#### **Benefits and Features**

- Integrated Downstream Cable QAM Modulator

- High-Density: 8, 16, 24, or 32 QAM Channels

- 14-Bit 4.6Gsps RF-DAC

- DOCSIS 3.0 DRFI Compliant

- Highly Flexible and Configurable

- · RRC Filters Support ITU-T J.83 Annex A, B, and C

- 1MHz to 8MHz Channel Bandwidth

- Full Carrier Agility within Each of Four 192MHz Blocks

Block Agility within 950MHz Output Bandwidth

- Reconfigurable Without Service Interruption

- Input Symbol Rate: 1Msym/s to 7.14Msym/s Independently Set for Each Channel

- Integrated QAM Mapper (16/32/64/128/256-QAM)

Supports All ITU-T J.83-Defined Constellations

- CMOS Input Port Supports Up to 1024-QAM

- Additional Features Ease RF Design

- · Programmable Digital Predistortion

- High DAC Output Power 9dBm (CW) Eliminates Pre-amp

- Low Power, Compact Solution

- 4.2W at 32 (6MHz) QAMs, f<sub>S</sub> = 4.6Gsps

- 12mm x 17mm, 280-Ball FCBGA

### **Applications**

- Edge QAM, CMTS, CCAP, IP-QAM

- Remote PHY, Coax Media Converters

- Multi-Dweller Unit Mini-Headends

Ordering Information appears at end of data sheet.

# **Simplified Block Diagram**

For related parts and recommended products to use with this part, refer to www.maximintegrated.com/MAX5862.related.

# **TABLE OF CONTENTS**

| General Description                             | 1    |

|-------------------------------------------------|------|

| Benefits and Features                           | 1    |

| Applications                                    | 1    |

| Simplified Block Diagram                        | 1    |

| Absolute Maximum Ratings                        | 9    |

| Package Thermal Characteristics                 | 9    |

| DC Electrical Characteristics                   | 9    |

| AC Electrical Characteristics                   | 12   |

| Typical Operating Characteristics               | . 17 |

| Ball Configuration                              | . 25 |

| Ball Description                                | . 25 |

| Signal Description                              | . 28 |

| Detailed Description                            | . 30 |

| Operational Overview                            | 30   |

| Reference System                                | 32   |

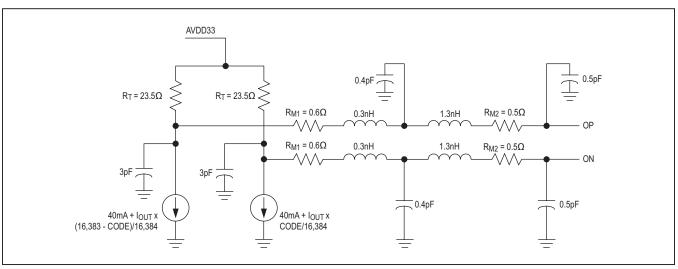

| Analog Output                                   | 32   |

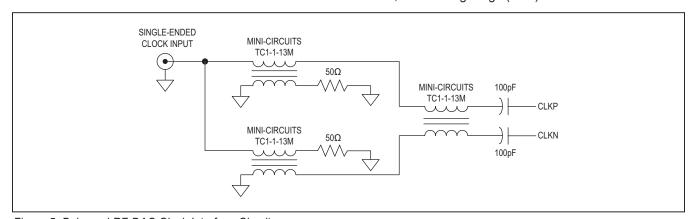

| Clock Inputs                                    | 33   |

| Clock Duty Cycle                                | 33   |

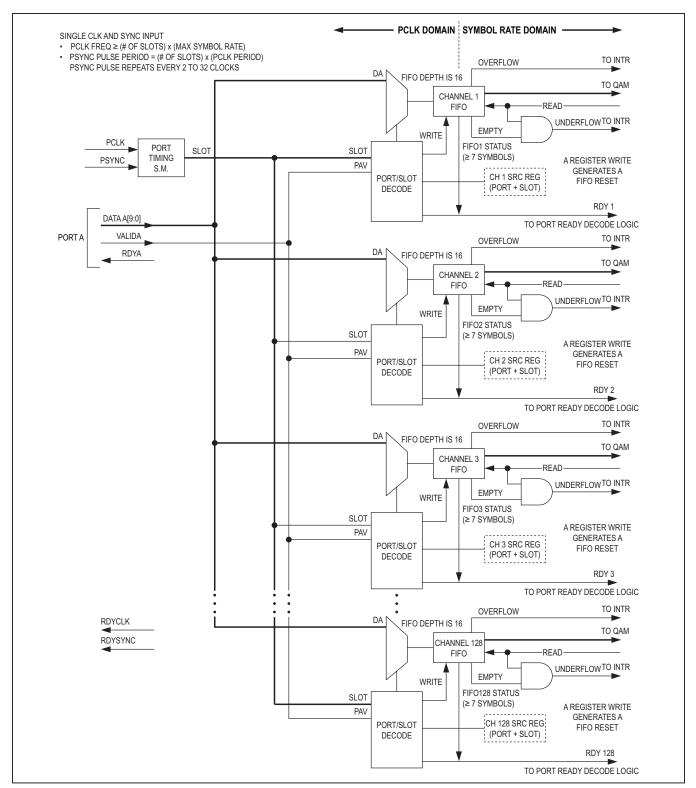

| Input Symbol Interface                          | 34   |

| Symbol Interface Description                    | 34   |

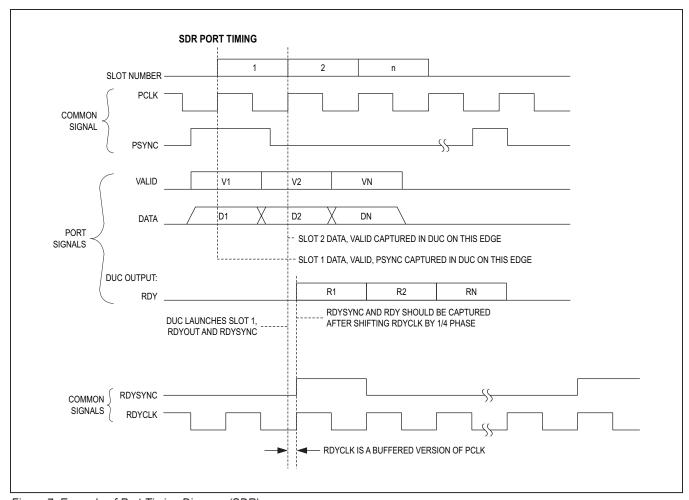

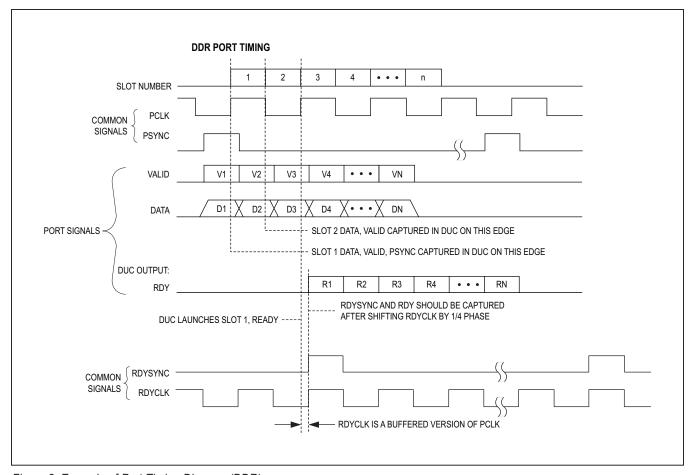

| Port Input Timing                               | 34   |

| Handshaking                                     | 36   |

| Port Clock                                      | 36   |

| Single Data Rate (SDR)                          | 36   |

| Double Data Rate (DDR)                          | 38   |

| Channel FIFO Operation                          | 39   |

| Modulator and Upconverter Core                  | 39   |

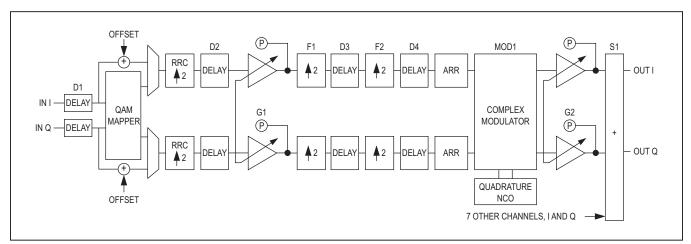

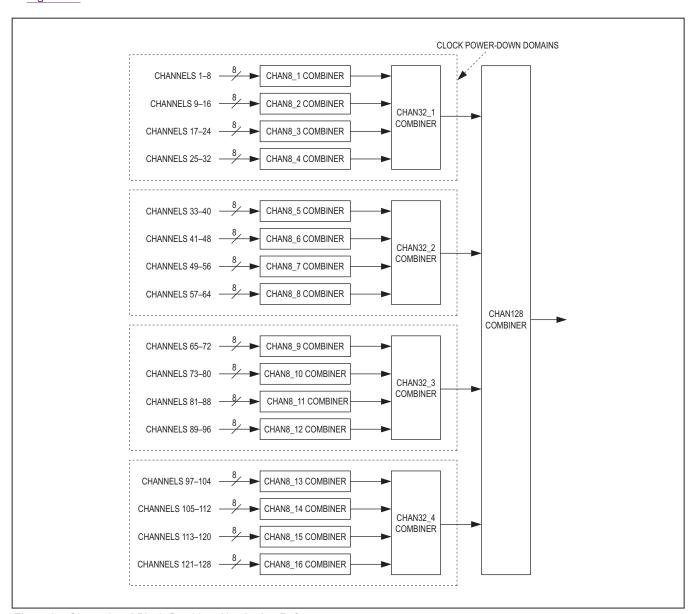

| DSP Path Block Diagram                          | 39   |

| Octal Channel Combiner (48MHz Block)            | 40   |

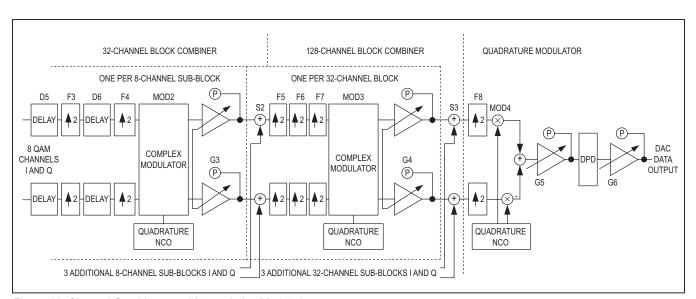

| Block Combiners and Digital Upconversion        | 41   |

| QAM Mapper                                      | 41   |

| RRC Filter                                      | 41   |

| Rate Resampler                                  | 43   |

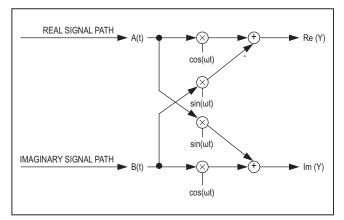

| Modulators                                      | 43   |

| Power Adjustment and Power Probes               | 43   |

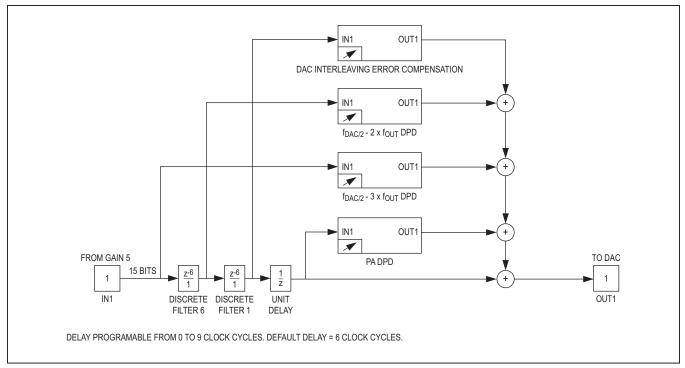

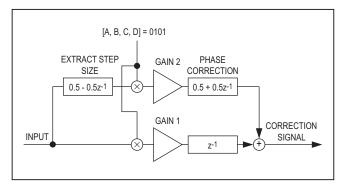

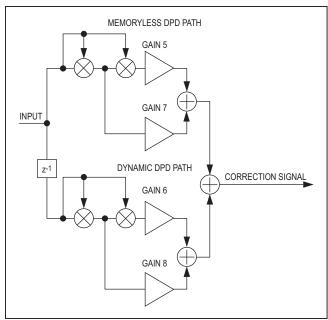

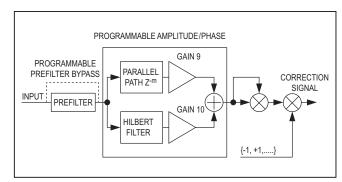

| DPD Function                                    | 44   |

| DPDCFG Register Bit Explanation (Address 0x081) | 46   |

| Synthogizable Bandwidth vs. Clock Bate          | 16   |

| IABLE OF CONTENTS (continued)                                       |    |

|---------------------------------------------------------------------|----|

| SPI Interface                                                       | 46 |

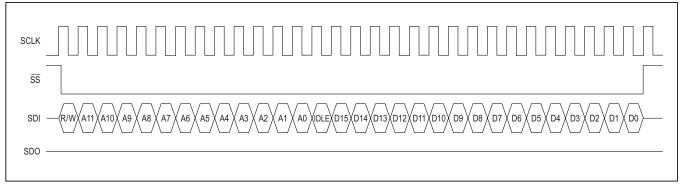

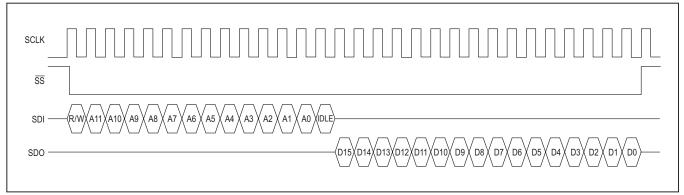

| SPI Command Format                                                  |    |

| Write Command                                                       |    |

| Read Command                                                        |    |

| Global Reset                                                        |    |

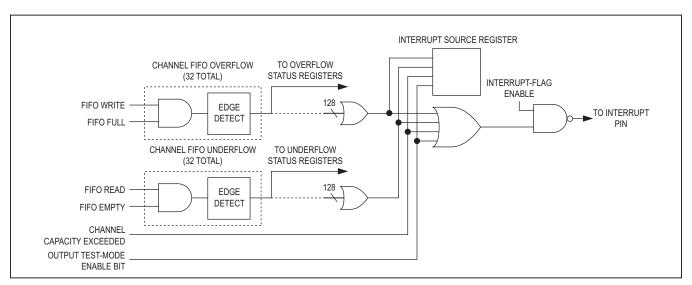

| Interrupts                                                          |    |

| FIFO Overflow                                                       |    |

| FIFO Underflow                                                      |    |

| Channel Capacity                                                    |    |

| Power Monitor Timer                                                 |    |

| Interrupt Tree                                                      |    |

| Applications Information                                            | 49 |

| Grounding, Bypassing, Power Supply, and Board-Layout Considerations | 49 |

| LC Resonator for DATACLK                                            | 49 |

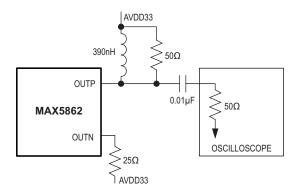

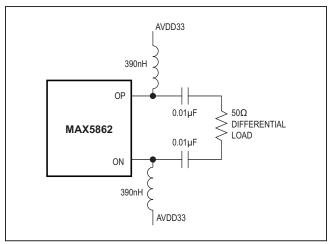

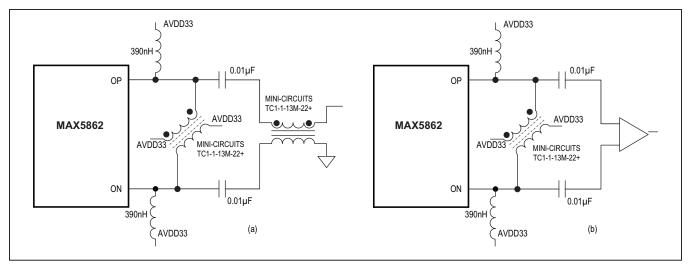

| Output Coupling                                                     | 49 |

| Configuration                                                       | 49 |

| Channel Center Frequency                                            | 50 |

| Optimizing Channel Power                                            | 50 |

| Channel Modifications                                               | 51 |

| Spectral Considerations                                             | 51 |

| DOCSIS 3.0 Spurious Emissions Requirements                          | 51 |

| DAC Sample Rate Selection                                           | 52 |

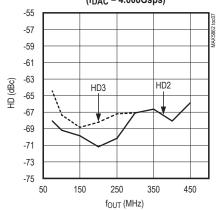

| Harmonic Distortion                                                 | 52 |

| Harmonics of Images Around the Clock Frequency                      | 52 |

| Latency                                                             | 52 |

| User Configurable Delays                                            | 53 |

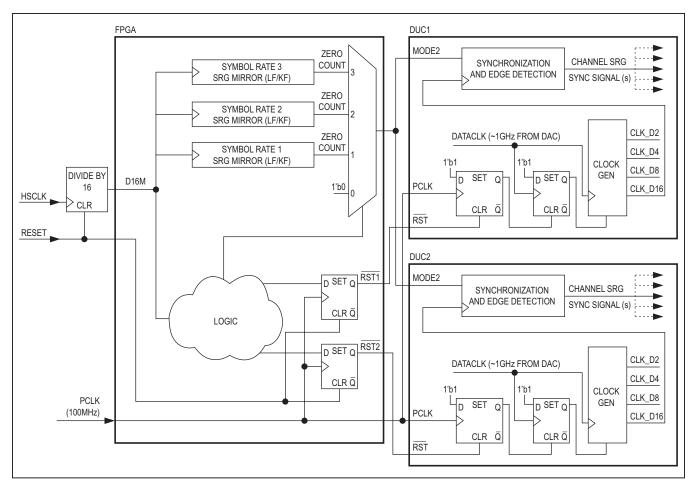

| Symbol Timing Alignment (Synchronization)                           | 53 |

| Aligning Multiple Channels Within a Single MAX5862                  | 53 |

| Aligning Channels Across Multiple MAX5862 Devices                   | 53 |

| Power Reduction                                                     |    |

| Lowest Standby Power                                                | 55 |

| Channel Muting                                                      | 55 |

| Block Shutdown of 32-Channel Combiners                              | 55 |

| Individual DPD Branch Shutdown                                      | 55 |

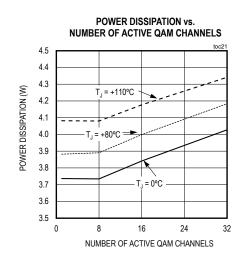

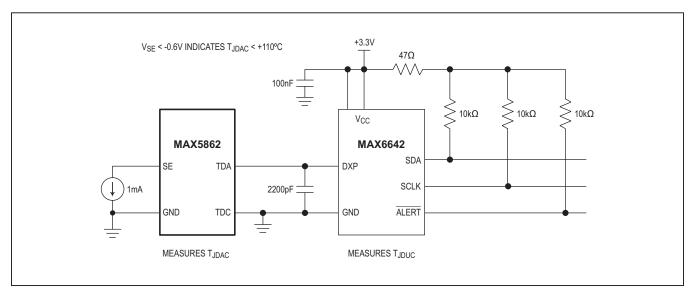

| Thermal Management                                                  |    |

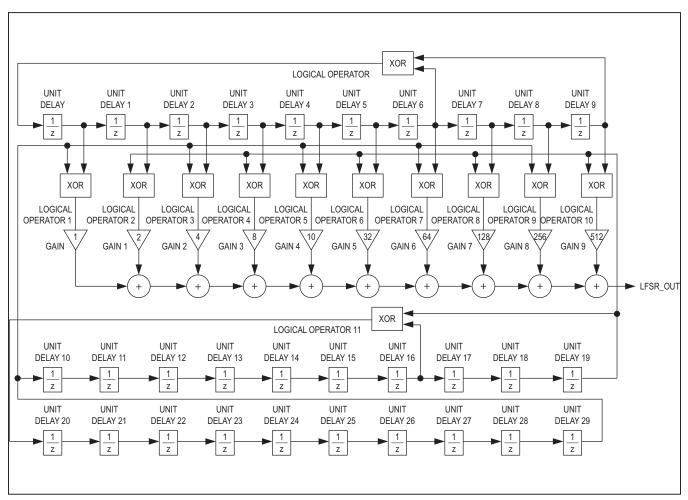

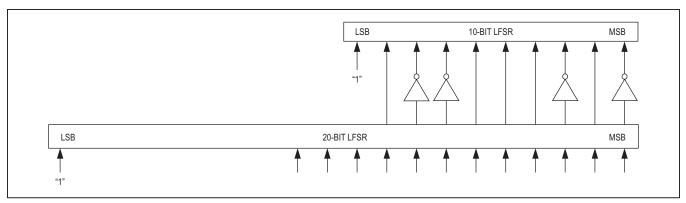

| PRBS Operation                                                      | 56 |

| LFSR Operation                                                      | 56 |

| Creating the LFSR Seeds                                             |    |

| TABLE OF CONTENTS (contin                       | nued) |

|-------------------------------------------------|-------|

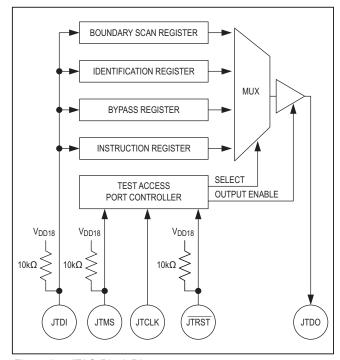

| JTAG                                            |       |

| JTAG Description                                |       |

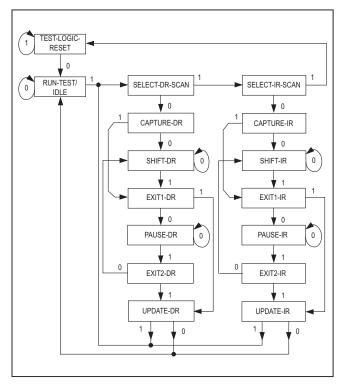

| JTAG TAP Controller State Machine Description   | 58    |

| JTAG Instruction Register And Instructions      | 59    |

| JTAG Test Registers                             | 60    |

| References                                      | 60    |

| GLOBAL REGISTERS                                |       |

| DEMULTIPLEXED REGISTERS                         | 63    |

| CHAN32 REGISTERS                                |       |

| CHAN128 REGISTERS                               | 91    |

| DPD REGISTERS                                   |       |

| CHAN8 PWR REGISTERS                             |       |

| PRBS REGISTERS                                  |       |

| EFUSE REGISTERS                                 |       |

| DLL REGISTERS                                   |       |

| Static Performance Parameter Definitions        | 109   |

| Offset Error                                    |       |

| Gain Error                                      |       |

| Dynamic Performance Parameter Definitions       |       |

| Noise Spectral Density                          |       |

| Two-/Four-Tone Intermodulation Distortion (IMD) |       |

| Adjacent Channel Power (ACP)                    |       |

| Ordering Information                            | 110   |

| Package Information                             | 110   |

| Revision History                                |       |

# LIST OF FIGURES Figure 1. Block Diagram..... Figure 7. Example of Port Timing Diagram (SDR)..... Figure 9. Octal Channel Combiner ..... Figure 12. DPD - Top Level Block Diagram..... Figure 19. Interrupt Tree Diagram ..... Figure 23. LFSR Block Diagram ..... Figure 26. JTAG TAP Controller State Machine .....

| LIST OF TABLES                                                  |    |

|-----------------------------------------------------------------|----|

| Table 1. Pin Function (DLLOFF, DELAY)                           | 30 |

| Table 2. Internal QAM Mapper Options                            | 42 |

| Table 3. QAM Mapper Symbol Levels                               | 42 |

| Table 4. Resampling Ratio Recommendations                       | 43 |

| Table 5. DPD Parameters Range and Resolution                    | 45 |

| Table 6. NCO Output Frequency Table                             | 51 |

| Table 7. Gain Registers                                         | 51 |

| Table 8. Gain Settings for Modulation and QAM Mapping Selection | 51 |

| Table 9. JTAG Instruction Codes                                 | 59 |

| Table 10. JTAG ID Code                                          | 60 |

| Table 11. JTAG Register (0x000)                                 | 62 |

| Table 12. GBL_CFG0 Register (0x001)                             | 62 |

| Table 13. EXT_SYNC Register (0x002)                             | 63 |

| Table 14. CFG Register (0x500)                                  | 64 |

| Table 15. INTERRUPT_CTRL Register (0x581)                       | 64 |

| Table 16. INT_FIFO_SUM Register (0x582)                         | 65 |

| Table 17. OFLOW_AL Register (0x583)                             | 66 |

| Table 18. OFLOW_AH Register (0x584)                             | 67 |

| Table 19. OFLOW_BL Register (0x585)                             | 68 |

| Table 20. OFLOW_BH Register (0x586)                             | 69 |

| Table 21. OFLOW_CL Register (0x587)                             | 70 |

| Table 22. OFLOW_CH Register (0x588)                             | 71 |

| Table 23. OFLOW_DL Register (0x589)                             | 72 |

| Table 24. OFLOW_DH Register (0x58A)                             | 73 |

| Table 25. UFLOW_AL Register (0x58B)                             |    |

| Table 26. UFLOW_AH Register (0x58C)                             | 75 |

| Table 27. UFLOW_BL Register (0x58D)                             | 76 |

| Table 28. UFLOW_BH Register (0x58E)                             | 77 |

| Table 29. UFLOW_CL Register (0x58F)                             | 78 |

| Table 30. UFLOW_CH Register (0x590)                             | 79 |

| Table 31. UFLOW_DL Register (0x591)                             | 80 |

| Table 32. UFLOW_DH Register (0x592)                             | 81 |

| Table 33. CHAN_IN_CFG Registers                                 | 81 |

| Table 34. COMB8 Registers                                       | 82 |

| Table 35. NCO2LSB Registers                                     | 82 |

| Table 36. G3_IPWR Registers                                     | 82 |

| Table 37. G3_QPWR Registers                                     | 83 |

| Table 38. KF_LF_MSB_1 Registers                                 | 83 |

| LIST OF TABLES (continued)            |      |

|---------------------------------------|------|

| Table 39. KF_LF_MSB_2 Registers       | . 84 |

| Table 40. KF_LF_MSB_3 Registers       | . 85 |

| Table 41. SYMIF Registers             | 86   |

| Table 42. KFA Registers               | . 87 |

| Table 43. KFLF Registers              | . 87 |

| Table 44. LFA Registers               | . 87 |

| Table 45. NCOA Registers              | . 88 |

| Table 46. NCOB Registers              | . 88 |

| Table 47. RRC Registers               | . 88 |

| Table 48. CHAN32 Registers            | 89   |

| Table 49. NCO3A Registers             | . 89 |

| Table 50. NCO3B Registers             | 90   |

| Table 51. G4_IPWR Registers           | 90   |

| Table 52. G4_QPWR Registers           | 90   |

| Table 53. HS_CFG Register (0x040)     | . 91 |

| Table 54. GAIN5 Register (0x041)      | . 91 |

| Table 55. NCO4A Register (0x042)      | 91   |

| Table 56. NCO4B Register (0x043)      | 92   |

| Table 57. G5_PWR Register (0x044)     | 92   |

| Table 58. GAIN6 Register (0x050)      | 92   |

| Table 59. GAIN6_PWR Register (0x051)  | . 93 |

| Table 60. PWRMON_CFG Register (0x046) | 93   |

| Table 61. PWRMON_1 Register (0x047)   | 93   |

| Table 62. PWRMON_2 Register (0x048)   | 94   |

| Table 63. PWRMON_3 Register (0x049)   | 94   |

| Table 64. XOR_CFG Register (0x04A)    | 94   |

| Table 65. SYNC_CFG Register (0x04B)   | 95   |

| Table 66. TEST_PORTA Register (0x04C) | 95   |

| Table 67. TEST_PORTB Register (0x04D) | 95   |

| Table 68. TEST_PORTC Register (0x04E) | 96   |

| Table 69. TEST_PORTD Register (0x04F) | 96   |

| Table 70. DPDCFG Register (0x081)     | . 97 |

| Table 71. DPD_2 Register (0x082)      | . 97 |

| Table 72. DPD_3 Register (0x083)      | . 98 |

| Table 73. DPD_4 Register (0x084)      | . 98 |

| Table 74. DPD_5 Register (0x085)      | . 98 |

| Table 75. DPD_6 Register (0x086)      | . 99 |

| Table 76. DPD 7 Register (0x087)      | . 99 |

| LIST OF TABLES (continued)              |     |

|-----------------------------------------|-----|

| Fable 77. DPD_8 Register (0x088)        | 99  |

| Гable 78. DPD_9 Register (0x089)        | 100 |

| Гable 79. DPD_10 Register (0x08A)       | 100 |

| Гable 80. DPD_11 Register (0x08B)       | 100 |

| Гable 81. DPD_12 Register (0x08C)       | 101 |

| Гable 82. DPD_13 Register (0x08D)       | 101 |

| Гable 83. DPD_14 Register (0x08E)       | 101 |

| Table 84. RRC_I_PWR Registers           | 102 |

| Fable 85. RRC_Q_PWR Registers           | 102 |

| Fable 86. MOD1_I_PWR Registers          | 102 |

| Fable 87. MOD_1_Q_PWR Registers         | 103 |

| Fable 88. PRBS Registers                | 103 |

| Fable 89. MASTER_KEY_1 Register (0x010) | 104 |

| Fable 90. MASTER_KEY_2 Register (0x011) | 104 |

| Fable 91. MASTER_KEY_3 Register (0x012) | 104 |

| Fable 92. MASTER_KEY_4 Register (0x013) | 104 |

| Fable 93. FACTORY_CAP Register (0x014)  | 105 |

| Fable 94. KEY_STATUS Register (0xA98)   | 105 |

| Γable 95. UPGRADE_CAP Register (0x015)  | 106 |

| Fable 96. DLLCTRL Register (0xA80)      | 107 |

| Table 97. DLLTRIM Register (0xA88)      | 108 |

| Table 98. DLL Register (0xA89)          | 108 |

| Гable 99. ОЕМ_TEST Register (0x003)     | 109 |

# **Absolute Maximum Ratings**

| AVDD33 to GND, DACREF                                                      | 0.3V to +3.6V               |

|----------------------------------------------------------------------------|-----------------------------|

| AVDD18, AVCLK to GND, DACREF                                               | 0.3V to +2.05V              |

| V <sub>DD10</sub> to GND                                                   | 0.3V to +1.2V               |

| AVCLK, V <sub>DD18</sub> , V <sub>DD18L</sub> , V <sub>DDDLL</sub> to GND. |                             |

| CMOS Outputs/Inputs to GND0.3                                              |                             |

| REFIO, FSADJ, to GND, DACREF0.3V                                           | to $(V_{AVDD33} + 0.3V)$    |

| OUTP, OUTN to GND, DACREF0.3V                                              | to $(V_{AVDD33} + 1.0V)$    |

| SE, DLLOFF, DELAY,                                                         |                             |

| REFRES to GND, DACREF0.3V                                                  | to $(V_{AVDD33} + 0.3V)$    |

| CLKP, CLKN to GND, DACREF0.3\                                              | $V$ to $(V_{AVCLK} + 0.3V)$ |

| LOCK, PERR to GND, DACREF0.3V                                              | to $(V_{AVDD18} + 0.3V)$    |

| CMOS (except LOCK, PERR) Output Short-Circuit Current 16mA  |

|-------------------------------------------------------------|

| TDA, TDC Short-Circuit Current8mA                           |

| LOCK, PERR Continuous Current8mA                            |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)*      |

| FCBGA (derate 91.2mW/°C above +70°C)5018mW                  |

| Operating Ambient Temperature Range0°C to +85°C             |

| Operating Junction Temperature Range (Note 1) 0°C to +110°C |

| Junction Temperature+150°C                                  |

| Storage Temperature65°C to +150°C                           |

| Soldering Temperature (reflow)+260°C                        |

|                                                             |

<sup>\*</sup>Use a heatsink for higher power dissipation.

Note 1: Temperature measured using the thermal diode. See the Thermal Management section.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Thermal Characteristics (Note 2)**

FCBGA

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) .....10.96°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ).........0.71°C/W

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

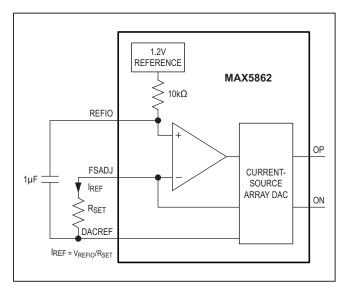

### **DC Electrical Characteristics**

$(V_{AVDD33} = 3.3V, V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V, V_{DD10} = 1.0V, R_{SET} = 2k\Omega$  (between FSADJ and DACREF),  $V_{REFIO}$  = external 1.25V,  $V_{DLLOFF}$  = 0V,  $V_{DL$

| PARAMETER                     | SYMBOL           | CONDITIONS                                                                                             | MIN  | TYP | MAX  | UNITS |  |

|-------------------------------|------------------|--------------------------------------------------------------------------------------------------------|------|-----|------|-------|--|

| CMOS LOGIC INPUTS (Except SE) |                  |                                                                                                        |      |     |      |       |  |

| High-Level Input Voltage      | V <sub>IH</sub>  |                                                                                                        | 1.17 |     |      | V     |  |

| Low-Level Input Voltage       | V <sub>IL</sub>  |                                                                                                        |      |     | 0.63 | V     |  |

| Input Leakage Current         | l                | All CMOS pins except JTDI, JTRST and JTMS, V <sub>IN</sub> = 0V to V <sub>DD18</sub>                   | -10  | ±1  | +10  |       |  |

| input Leakage Guirent         | IIN              | CMOS pins JTDI, $\overline{\text{JTRST}}$ and JTMS (Note 6); $V_{\text{IN}}$ = 0V to $V_{\text{DD18}}$ |      |     | 100  | - μA  |  |

| Input Capacitance             | C <sub>IN</sub>  |                                                                                                        |      | 5   |      | pF    |  |

| CMOS LOGIC OUTPUTS (Excep     | t LOCK, PE       | RR)                                                                                                    |      |     |      |       |  |

| High-Level Output Voltage     | V <sub>OH</sub>  | I <sub>OH</sub> = -100μA                                                                               | 1.35 |     |      | V     |  |

| Low-Level Output Voltage      | V <sub>OL</sub>  | I <sub>OL</sub> = 100μA                                                                                |      |     | 0.45 | V     |  |

| High-Impedance Output Current | loz              | 0V < V <sub>OUT</sub> < V <sub>DD18</sub>                                                              | -10  |     | +10  | μA    |  |

| Output Short-Circuit Current  | los              |                                                                                                        |      | 16  |      | mA    |  |

| Output Capacitance            | C <sub>OUT</sub> |                                                                                                        |      | 5   |      | pF    |  |

$(V_{AVDD33} = 3.3V,\ V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V,\ V_{DD10} = 1.0V,\ R_{SET} = 2k\Omega\ (between\ FSADJ\ and\ DACREF),\ V_{REFIO} = external\ 1.25V,\ V_{DLLOFF} = 0V,\ V_{DELAY} = 0V,\ f_{CLK} = 2304MHz,\ DPD\ off,\ R_{REFRES} = 500\Omega,\ tested\ at\ T_A = +25^{\circ}C\ and\ T_J = +110^{\circ}C\ to\ an\ accuracy\ of\ \pm15^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_J = 65^{\circ}C\ \pm15^{\circ}C.$ ) (Note 5)

| PARAMETER                           | SYMBOL              | CONDITIONS               | MIN                                      | TYP  | MAX                                      | UNITS |

|-------------------------------------|---------------------|--------------------------|------------------------------------------|------|------------------------------------------|-------|

| CMOS LOGIC OUTPUTS (LOCK            | , PERR)             |                          |                                          |      |                                          |       |

| High-Level Output Voltage           | V <sub>OH</sub>     | I <sub>OH</sub> = -200μA | V <sub>AVDD18</sub><br>- 0.2             |      |                                          | V     |

| Low-Level Output Voltage            | V <sub>OL</sub>     | I <sub>OL</sub> = 200μA  |                                          |      | 0.2                                      | V     |

| Output Capacitance                  | C <sub>OUT</sub>    |                          |                                          | 5    |                                          | pF    |

| CMOS LOGIC INPUTS (SE)              | •                   |                          |                                          |      | ,                                        |       |

| High-Level Input Voltage            | V <sub>IH</sub>     |                          | 0.7 x<br>V <sub>AVDD18</sub>             |      |                                          | V     |

| Low-Level Input Voltage             | V <sub>IL</sub>     |                          |                                          |      | 0.3 x<br>V <sub>AVDD18</sub>             | V     |

| Input Leakage Current               | I <sub>IN</sub>     |                          | -10                                      |      | 10                                       | μΑ    |

| Input Capacitance                   | C <sub>IN</sub>     |                          |                                          | 5    |                                          | pF    |

| 1.8V 4-LEVEL LOGIC INPUTS (E        | LLOFF, DEL          | AY)                      |                                          |      |                                          |       |

| Input 4-Level Logic Open            | V <sub>OC4</sub>    |                          | 23/32 x<br>V <sub>AVDD18</sub><br>+ 60mV |      | 29/32 x<br>V <sub>AVDD18</sub><br>- 60mV | V     |

| Input 4-Level Logic Res             | V <sub>RC4</sub>    |                          | 7/32 x<br>V <sub>AVDD18</sub><br>+ 60mV  |      | 23/32 x<br>V <sub>AVDD18</sub><br>- 60mV | V     |

| Input 4-Level Logic High            | V <sub>IH4</sub>    |                          | 29/32 x<br>V <sub>AVDD18</sub><br>+ 60mV |      | V <sub>AVDD18</sub>                      | V     |

| Input 4-Level Logic Low             | V <sub>IL4</sub>    |                          | 0                                        |      | 7/32 x<br>V <sub>AVDD18</sub><br>- 60mV  | V     |

| Input Pullup Current                | I <sub>PU4</sub>    |                          | 8                                        | 11.3 | 15                                       | μΑ    |

| Input Pulldown Current              | I <sub>PD4</sub>    |                          | 32                                       |      | 64                                       | μΑ    |

| POWER SUPPLY                        | ,                   |                          |                                          |      | ,                                        |       |

| Analog Supply Voltage Range         | V <sub>AVDD33</sub> |                          | 3.1                                      | 3.3  | 3.5                                      | V     |

| Clock Supply Voltage Range          | V <sub>AVCLK</sub>  |                          | 1.7                                      | 1.8  | 1.9                                      | V     |

| Analog 1.8V Supply Voltage<br>Range | V <sub>AVDD18</sub> |                          | 1.7                                      | 1.8  | 1.9                                      | V     |

| CMOS I/O Supply Voltage<br>Range    | V <sub>DD18</sub>   |                          | 1.7                                      | 1.8  | 1.9                                      | V     |

| LVDS I/O Supply Voltage Range       | V <sub>DD18L</sub>  |                          | 1.7                                      | 1.8  | 1.9                                      | V     |

| Bias Supply Voltage Range           | V <sub>DDDLL</sub>  |                          | 1.7                                      | 1.8  | 1.9                                      | V     |

| Core Supply Voltage Range           | V <sub>DD10</sub>   |                          | 0.95                                     | 1.0  | 1.1                                      | V     |

$(V_{AVDD33} = 3.3V,\ V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V,\ V_{DD10} = 1.0V,\ R_{SET} = 2k\Omega\ (between\ FSADJ\ and\ DACREF),\ V_{REFIO} = external\ 1.25V,\ V_{DLLOFF} = 0V,\ V_{DELAY} = 0V,\ f_{CLK} = 2304MHz,\ DPD\ off,\ R_{REFRES} = 500\Omega,\ tested\ at\ T_A = +25^{\circ}C\ and\ T_J = +110^{\circ}C\ to\ an\ accuracy\ of\ \pm15^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_J = 65^{\circ}C\ \pm15^{\circ}C.$ ) (Note 5)

| PARAMETER                                   | SYMBOL               | CONDITIONS                                                                                                    | MIN | TYP  | MAX  | UNITS  |

|---------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------|-----|------|------|--------|

| Analog Supply Current                       | I <sub>AVDD33</sub>  | Current is measured using internal PRBS generators as the source; configured for 32 channels, 256-QAM Annex B |     | 330  | 360  | mA     |

| Clock Supply Current                        | I <sub>AVCLK</sub>   | Current is measured using internal PRBS generators as the source; configured for 32 channels, 256-QAM Annex B |     | 450  | 500  | mA     |

| Analog 1.8V Supply Current                  | I <sub>AVDD18</sub>  | Current is measured using internal PRBS generators as the source; configured for 32 channels, 256-QAM Annex B |     | 245  | 290  | mA     |

| 1.8V Supply Current, V <sub>DD18</sub>      | I <sub>VDD18</sub>   |                                                                                                               |     | 25   |      | mA     |

| 1.8V Supply Current, V <sub>DD18L</sub>     | I <sub>VDD18L</sub>  | Current is measured using internal PRBS generators as the source; configured for 32 channels, 256-QAM Annex B |     | 321  | 350  | mA     |

| Bias Supply Current, V <sub>DDDLL</sub>     | I <sub>VDDDLL</sub>  | Current is measured using internal PRBS generators as the source; configured for 32 channels, 256-QAM Annex B |     | 32   | 37   | mA     |

| 1.0V Supply Current (Active)                | I <sub>VDD10</sub>   | Current is measured using internal PRBS generators as the source; configured for 32 channels, 256-QAM Annex B |     | 1190 | 2900 | mA     |

| 1.0V Supply Current (Standby)               | I <sub>VDD10SB</sub> | RST = 0, SCLK = 0, PCLK = 0                                                                                   |     |      | 2350 | mA     |

| 1.0V Supply Current (Static)                | I <sub>VDD10ST</sub> | RST = 0, CLKN/P = 0, SCLK = 0,<br>PCLK = 0                                                                    |     |      | 2350 | mA     |

| Power Dissipation                           | P <sub>DISS</sub>    | Power is measured using internal PRBS generators as the source; configured for 32 channels. 256-QAM (Note 7)  |     | 4.2  | 6.25 | W      |

| REFERENCE                                   |                      |                                                                                                               |     |      |      |        |

| Internal Reference Voltage<br>Range         | V <sub>REFIO</sub>   |                                                                                                               | 1.1 | 1.2  | 1.3  | V      |

| Reference Input Voltage<br>Compliance Range | V <sub>REFIOR</sub>  |                                                                                                               | 0.5 |      | 1.8  | V      |

| Reference Input Resistance                  | R <sub>REFIO</sub>   |                                                                                                               |     | 10   |      | kΩ     |

| Reference Voltage Drift                     | TCO <sub>REF</sub>   |                                                                                                               |     | 50   |      | ppm/°C |

### **AC Electrical Characteristics**

$(V_{AVDD33} = 3.3V,\ V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V,\ V_{DD10} = 1.0V,\ R_{SET} = 2k\Omega\ (between\ FSADJ\ and\ DACREF),\ V_{REFIO} = external\ 1.25V,\ V_{DLLOFF} = 0V,\ V_{DELAY} = 0V,\ f_{CLK} = 2304MHz,\ DPD\ off,\ R_{REFRES} = 500\Omega,\ tested\ at\ T_A = +25^{\circ}C$  and  $T_J = +110^{\circ}C$  to an accuracy of  $\pm 15^{\circ}C$ , unless otherwise noted. Typical values are at  $T_J = 65^{\circ}C\ \pm 15^{\circ}C$ .) (Note 5)

| PARAMETER                      | SYMBOL               | CONDITIONS                                                                               | MIN | TYP                   | MAX | UNITS |

|--------------------------------|----------------------|------------------------------------------------------------------------------------------|-----|-----------------------|-----|-------|

| DAC CLOCK INPUTS (CLKP, C      | LKN)                 |                                                                                          |     |                       |     | 1     |

| Minimum Clock Input Power      | P <sub>CLK,MIN</sub> | (Note 8)                                                                                 |     | 6                     |     | dBm   |

| Maximum Clock Input Power      | P <sub>CLK,MAX</sub> | Power measured into DAC clock input with 100Ω external differential termination resistor |     | 12                    |     | dBm   |

| Common-Mode Voltage            | V <sub>COMCLK</sub>  | Input is self biased                                                                     |     | V <sub>AVCLK</sub> /3 |     | V     |

| Input Resistance               | R <sub>CLK</sub>     | Differential                                                                             |     | 100                   |     | Ω     |

| Input Capacitance              | C <sub>CLK</sub>     |                                                                                          |     | 2                     |     | pF    |

| CMOS PORT CLOCK INPUT (F       | PCLK)                |                                                                                          |     |                       |     |       |

| Clock Frequency                | f <sub>PCLK</sub>    | 1/t <sub>TP</sub> (Note 9)                                                               |     |                       | 128 | MHz   |

| Input Capacitance              |                      |                                                                                          |     | 3                     |     | pF    |

| Minimum Clock Duty Cycle       |                      |                                                                                          |     | 45                    |     | %     |

| Maximum Clock Duty Cycle       |                      |                                                                                          |     | 55                    |     | %     |

| CMOS DATA INPUTS (Note 10)     | )                    |                                                                                          |     |                       |     |       |

| Data to Port Clock Setup Time  |                      |                                                                                          | 1   |                       |     | ns    |

| Data to Port Clock Hold Time   |                      |                                                                                          | 1   |                       |     | ns    |

| Input Capacitance              |                      |                                                                                          |     | 3                     |     | pF    |

| CMOS DATA OUTPUTS (Note        | 10)                  |                                                                                          |     |                       |     |       |

| Output Rise Time               |                      | 10% to 90% of V <sub>DD18</sub> , 10pF load                                              |     | 2                     |     | ns    |

| Output Fall Time               |                      | 10% to 90% of V <sub>DD18</sub> , 10pF load                                              |     | 2                     |     | ns    |

| RDYCLK to RDYA Data Valid Time |                      |                                                                                          | 0   |                       | 1.5 | ns    |

| Output Capacitance             |                      |                                                                                          |     | 3                     |     | pF    |

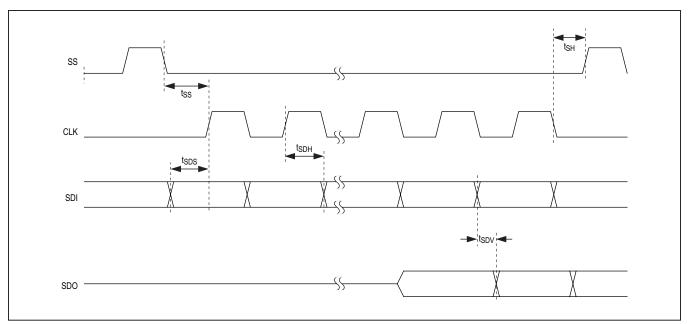

| SERIAL PORT INTERFACE TIM      | ING (SCLK,           | SDI,SDO, <del>SS</del> )                                                                 | '   |                       |     |       |

| SCLK Write Frequency           | fsclw                |                                                                                          |     |                       | 66  | MHz   |

| SCLK Read Frequency            | fSCLR                |                                                                                          |     |                       | 66  | MHz   |

| SS Setup time                  | t <sub>SS</sub>      | (Note 10)                                                                                | 1.5 |                       |     | ns    |

| Input Hold Time                | t <sub>SDH</sub>     | (Note 10)                                                                                | 1.1 |                       |     | ns    |

| Input Setup Time               | t <sub>SDS</sub>     | (Note 10)                                                                                | 2.2 |                       |     | ns    |

| Data Valid Duration            | t <sub>SDV</sub>     | (Note 10)                                                                                |     |                       | 7.8 | ns    |

| JTAG INTERFACE TIMING (JT      | DI, JTDO, JT         | CLK, JTMS, JTRST) (Notes 6 and 11)                                                       |     |                       |     |       |

| ITCLK Clock Frequency          |                      | Bypass mode                                                                              |     |                       | 50  | MHz   |

| JTCLK Clock Frequency          |                      | Boundary scan mode                                                                       |     |                       | 25  | IVI⊓∠ |

$(V_{AVDD33} = 3.3V,\ V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V,\ V_{DD10} = 1.0V,\ R_{SET} = 2k\Omega\ (between\ FSADJ\ and\ DACREF),\ V_{REFIO} = external\ 1.25V,\ V_{DLLOFF} = 0V,\ V_{DELAY} = 0V,\ f_{CLK} = 2304MHz,\ DPD\ off,\ R_{REFRES} = 500\Omega,\ tested\ at\ T_A = +25^{\circ}C\ and\ T_J = +110^{\circ}C\ to\ an\ accuracy\ of\ \pm15^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $T_J = 65^{\circ}C\ \pm15^{\circ}C.$ ) (Note 5)

| PARAMETER                                                                                         | SYMBOL           | CONDITIONS                                               |                                                                                                        | MIN  | TYP     | MAX  | UNITS |  |  |

|---------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|---------|------|-------|--|--|

| JTCLK Clock High/Low Time                                                                         |                  | (Notes 10 and 12)                                        |                                                                                                        | 5    |         |      | ns    |  |  |

| JTCLK to JTDI Setup Time                                                                          |                  | (Note 10)                                                |                                                                                                        | 0    |         |      | ns    |  |  |

| JTCLK to JTDI Hold Time                                                                           |                  | (Note 10)                                                |                                                                                                        | 2.5  |         |      | ns    |  |  |

| JTCLK to JTDO Delay                                                                               |                  | (Note 10)                                                |                                                                                                        | 4.1  |         |      | ns    |  |  |

| JTCK to JTDO High-Z Delay                                                                         |                  | (Note 10)                                                |                                                                                                        | 10   |         |      | ns    |  |  |

| JTRST Width Low Time                                                                              |                  |                                                          |                                                                                                        |      | 100     |      | ns    |  |  |

| DAC STATIC PERFORMANCE                                                                            |                  |                                                          |                                                                                                        |      |         |      |       |  |  |

| Resolution                                                                                        |                  |                                                          |                                                                                                        |      | 14      |      | Bits  |  |  |

| Full-Scale Output Current<br>Range                                                                | I <sub>OUT</sub> | (Note 13)                                                |                                                                                                        | 10   |         | 80   | mA    |  |  |

| Output-Power Gain Error                                                                           | GE               | Differential, into 500 f <sub>OUT</sub> = 103.5MHz       | ) load,                                                                                                | -0.7 |         | 0.7  | dB    |  |  |

| Output Dower Drift                                                                                |                  | Internal reference                                       |                                                                                                        |      | -0.003  |      | 4D/°C |  |  |

| Output Power Drift                                                                                |                  | External reference                                       |                                                                                                        |      | -0.0025 |      | dB/°C |  |  |

| Full-Scale Output Power                                                                           | P <sub>OUT</sub> | Differential, into 500 f <sub>OUT</sub> = 103.5MHz       | Σ load,                                                                                                |      | 8.6     |      | dBm   |  |  |

| Output Resistance                                                                                 | R <sub>OUT</sub> | Differential                                             |                                                                                                        |      | 50      |      | Ω     |  |  |

| DAC DYNAMIC PERFORMANC                                                                            |                  |                                                          |                                                                                                        |      |         |      | 1     |  |  |

| Clock Rate                                                                                        | fCLK             |                                                          |                                                                                                        |      |         | 2304 | MHz   |  |  |

| Output Update Rate                                                                                | f <sub>DAC</sub> |                                                          |                                                                                                        |      |         | 4608 | Msps  |  |  |

|                                                                                                   |                  |                                                          | Adjacent channel<br>(750kHz from<br>channel block<br>edge to 6MHz<br>from channel block<br>edge)       |      | -71     | -64  |       |  |  |

| Out-of-Band Noise and<br>Spurious, Eight 6MHz QAM<br>Carriers, Average Total Power =<br>-18.7dBFS |                  | f <sub>OUT</sub> = 400MHz<br>f <sub>DAC</sub> = 4608Msps | Next-adjacent<br>channel (6MHz<br>from channel block<br>edge to 12MHz<br>from channel block<br>edge)   |      | -73     | -66  | dBc   |  |  |

|                                                                                                   |                  |                                                          | Third-adjacent<br>channel (12MHz<br>from channel block<br>edge to 18MHz<br>from channel block<br>edge) |      | -73     | -66  |       |  |  |

|                                                                                                   |                  |                                                          | Noise in any other channel (Note 16)                                                                   |      | -73     |      |       |  |  |

$(V_{AVDD33} = 3.3V,\ V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V,\ V_{DD10} = 1.0V,\ R_{SET} = 2k\Omega\ (between\ FSADJ\ and\ DACREF),\ V_{REFIO} = external\ 1.25V,\ V_{DLLOFF} = 0V,\ V_{DELAY} = 0V,\ f_{CLK} = 2304MHz,\ DPD\ off,\ R_{REFRES} = 500\Omega,\ tested\ at\ T_A = +25^{\circ}C$  and  $T_J = +110^{\circ}C$  to an accuracy of  $\pm 15^{\circ}C$ , unless otherwise noted. Typical values are at  $T_J = 65^{\circ}C\ \pm 15^{\circ}C$ .) (Note 5)

| PARAMETER                                         | SYMBOL                                               | COND                                                      | ITIONS                                                                                                 | MIN | TYP                                                                                              | MAX | UNITS |  |  |

|---------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------|-----|-------|--|--|

|                                                   |                                                      |                                                           |                                                                                                        |     | Adjacent channel<br>(750kHz from<br>channel block<br>edge to 6MHz<br>from channel block<br>edge) |     | -67   |  |  |

|                                                   |                                                      | f <sub>OUT</sub> = 860MHz<br>f <sub>DAC</sub> = 4608Msps  | Next-adjacent<br>channel (6MHz<br>from channel block<br>edge to 12MHz<br>from channel block<br>edge)   |     | -66                                                                                              |     | dBc   |  |  |

|                                                   |                                                      |                                                           | Third-adjacent<br>channel (12MHz<br>from channel block<br>edge to 18MHz<br>from channel block<br>edge) |     | -66                                                                                              |     |       |  |  |

| Out-of-Band Noise and<br>Spurious, Eight 6MHz QAM |                                                      |                                                           | Noise in any other channel (Note 16)                                                                   |     | -65                                                                                              |     |       |  |  |

| Carriers, Average Total Power = -18.7dBFS         | f <sub>OUT</sub> = 1000M<br>f <sub>DAC</sub> = 4608M |                                                           | Adjacent channel<br>(750kHz from<br>channel block<br>edge to 6MHz<br>from channel block<br>edge)       |     | -67                                                                                              |     |       |  |  |

|                                                   |                                                      | f <sub>OUT</sub> = 1000MHz<br>f <sub>DAC</sub> = 4608Msps | Next-adjacent<br>channel (6MHz<br>from channel block<br>edge to 12MHz<br>from channel block<br>edge)   |     | -67                                                                                              |     | dBc   |  |  |

|                                                   |                                                      |                                                           | Third-adjacent<br>channel (12MHz<br>from channel block<br>edge to 18MHz<br>from channel block<br>edge) |     | -67                                                                                              |     |       |  |  |

|                                                   |                                                      |                                                           | Noise in any other channel (Note 16)                                                                   |     | -66                                                                                              |     |       |  |  |

$(V_{AVDD33} = 3.3V, V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDD1L} = 1.8V, V_{DD10} = 1.0V, R_{SET} = 2k\Omega \text{ (between FSADJ and DACREF)}, V_{REFIO} = \text{external } 1.25V, V_{DLLOFF} = 0V, V_{DELAY} = 0V, f_{CLK} = 2304MHz, DPD \text{ off, } R_{REFRES} = 500\Omega, \text{ tested at } T_A = +25^{\circ}\text{C} \text{ and } T_J = +110^{\circ}\text{C} \text{ to an accuracy of } \pm15^{\circ}\text{C}, \text{ unless otherwise noted.}$

| PARAMETER                                                                                      | SYMBOL           | CONE                                                                                       | OITIONS                                                                             | MIN  | TYP  | MAX  | UNITS                   |  |

|------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------|------|------|-------------------------|--|

| Harmonic Distortion, Block<br>of Four 6MHz QAM Carriers,<br>Average Total Power =<br>-15.7dBFS |                  | f <sub>OUT</sub> = 300MHz<br>f <sub>DAC</sub> = 4608Msps                                   | In each of eight<br>6MHz channels<br>coinciding with<br>2nd harmonic<br>components  |      | -72  | -64  | - dBc                   |  |

|                                                                                                |                  |                                                                                            | In each of twelve<br>6MHz channels<br>coinciding with<br>3rd harmonic<br>components |      | -72  | -65  |                         |  |

| Gain Flatness                                                                                  | GF               | Over any single 6M                                                                         | Hz channel                                                                          |      | 0.05 |      | dB                      |  |

| Gaill Flatiless                                                                                | Gi               | Within 45MHz to 10                                                                         | 03MHz band                                                                          |      | 1.6  |      | ub l                    |  |

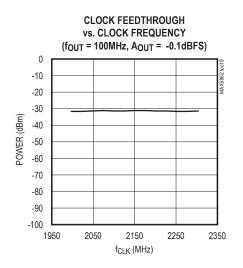

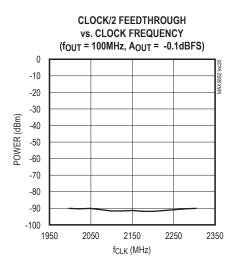

| Clock Spurs                                                                                    |                  | f <sub>DAC</sub> /4 spur, f <sub>DAC</sub> = 4608Msps, 8 QAM carriers                      |                                                                                     |      | -80  |      | dBm                     |  |

|                                                                                                |                  | f <sub>DAC</sub> /8 spur, f <sub>DAC</sub> = carriers                                      | 4608Msps, 8 QAM                                                                     |      | -100 |      | ubin                    |  |

| f <sub>DAC</sub> /2 - f <sub>OUT</sub> Image                                                   |                  | f <sub>DAC</sub> = 4608Msps, 8<br>covering the band fr<br>1000MHz                          |                                                                                     | -40  |      | dBc  |                         |  |

| f <sub>DAC</sub> /2 - 2f <sub>OUT</sub> Spurious                                               |                  | f <sub>DAC</sub> = 4608Msps, 8 QAM carriers<br>covering the band from 952MHz to<br>1000MHz |                                                                                     |      | -64  |      | dBc                     |  |

| TIMING CHARACTERISTICS                                                                         |                  |                                                                                            |                                                                                     |      |      |      |                         |  |

| DAC DLL Frequency Range                                                                        | f <sub>DLL</sub> | f <sub>DLL</sub> = f <sub>CLK</sub> /2                                                     | DELAY = High                                                                        | 1075 |      | 1152 | <br>  MHz               |  |

| DAO DEET requeries range                                                                       | 'DLL             | DLLOFF = Low                                                                               | DELAY = Open                                                                        | 950  |      | 1075 | 1711 12                 |  |

| Parity Error Pulse Width                                                                       | t <sub>ERR</sub> | Pulse width of PERR when a parity error is detected                                        |                                                                                     |      | 48   |      | Data<br>Clock<br>Cycles |  |

| ANALOG OUTPUT                                                                                  |                  |                                                                                            |                                                                                     |      |      | -    |                         |  |

| Output Bandwidth                                                                               | BW               | (Note 15)                                                                                  |                                                                                     |      | 2.0  |      | GHz                     |  |

- Note 5: All specifications are 100% tested at T<sub>A</sub> = +25°C and T<sub>J</sub> = +110°C with an accuracy of ±15°C. Specifications at T<sub>A</sub> < +25°C are guaranteed by design and characterization.

- Note 6: JTAG control signals JTDI, JTRST, and JTMS each have a ~50kΩ pullup resistor.

- Note 7: Power does not include the V<sub>DD18</sub> supply.

- Note 8: Transformer-coupled clock input.

- Note 9: PCLK is a continuous clock and must not be gapped.

- Note 10: Guaranteed by design and characterization.

- Note 11: All CMOS signals are bidirectional in JTAG mode except for LOCK, SE, PERR, MODE, MODE2, TEST, and JTAG control pins (JTCLK, JTMS, JTRST, JTDI, JTDO).

- Note 12: Clock can be stopped high or low.

- **Note 13:** Nominal full-scale current  $I_{OUT}$  = 128 x  $I_{REF}$ .

$(V_{AVDD33} = 3.3V, \ V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V, \ V_{DD10} = 1.0V, \ R_{SET} = 2k\Omega \ (between FSADJ and DACREF), \ V_{REFIO} = external 1.25V, \ V_{DLLOFF} = 0V, \ V_{DELAY} = 0V, \ f_{CLK} = 2304MHz, \ DPD \ off, \ R_{REFRES} = 500\Omega, \ tested \ at \ T_A = +25°C \ and \ T_J = +110°C \ to \ an \ accuracy \ of \pm 15°C, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_J = 65°C \ \pm 15°C.) \ (Note 5)$

Note 14: Measured single-ended into a double terminated  $50\Omega$  load.

Note 15: Excludes impulse-response dependent rolloff inherent in the DAC.

Note 16: Excludes clock, clock images, f<sub>DAC</sub>/2 - f<sub>OUT</sub>, and f<sub>DAC</sub>/2 - 2f<sub>OUT</sub> spurs, which are specified separately.

Note 17: CLK input = +9dBm, AC-coupled sine wave.

## **Typical Operating Characteristics**

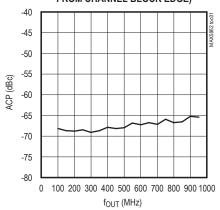

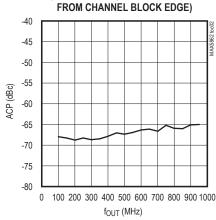

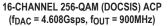

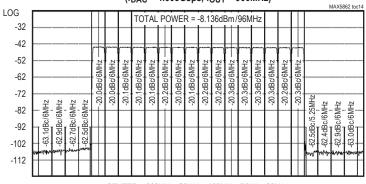

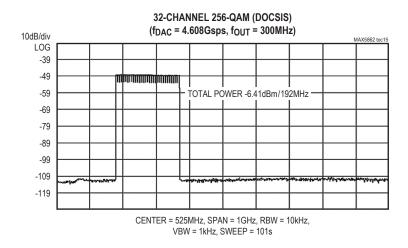

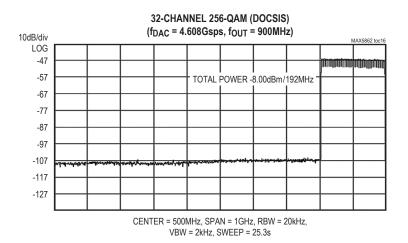

$(V_{AVDD33} = 3.3V, V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DD18L} = 1.8V, V_{DD10} = 1.0V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{CLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega$ , transformer-coupled differential output, DPD off, tests at  $T_{J} = +60^{\circ}C$ , unless otherwise noted.)

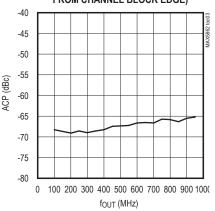

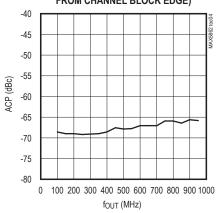

8-CHANNEL 256-QAM ACP vs. OUTPUT FREQUENCY (fDAC = 4.608Gsps, 750kHz TO 6MHz FROM CHANNEL BLOCK EDGE)

8-CHANNEL 256-QAM ACP vs. OUTPUT FREQUENCY (f<sub>DAC</sub> = 4.608Gsps, 6MHz TO 12MHz FROM CHANNEL BLOCK FIGE)

8-CHANNEL 256-QAM ACP vs. OUTPUT FREQUENCY (fDAC = 4.608Gsps, 12MHz TO 18MHz FROM CHANNEL BLOCK EDGE)

8-CHANNEL 256-QAM ACP vs. OUTPUT FREQUENCY (fDAC = 4.608Gsps, 18MHz TO 24MHz FROM CHANNEL BLOCK EDGE)

$(V_{AVDD33} = 3.3V, V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V, V_{DD10} = 1.0V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{CLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega, transformer-coupled differential output, DPD off, tests at T_J = +60°C, unless otherwise noted.)$

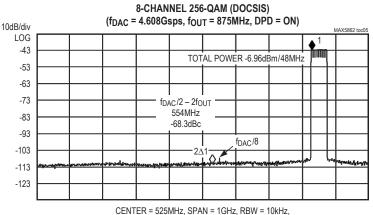

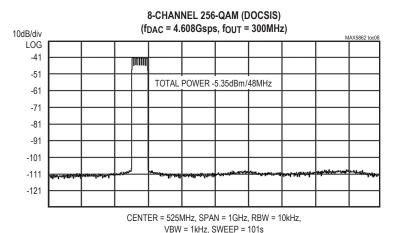

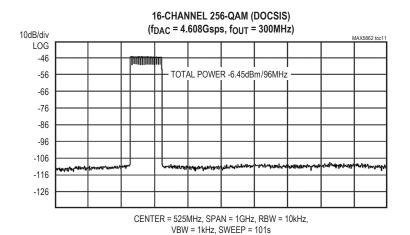

CENTER = 525MHz, SPAN = 1GHz, RBW = 10kHz VBW = 1kHz, SWEEP = 101s

#### 8-CHANNEL 256-QAM (DOCSIS) (fDAC = 4.608Gsps, fOUT = 875MHz, DPD = OFF) 10dB/div LOG -43 imm TOTAL POWER -6.97dBm/48MHz -53 -63 -73 fDAC/2 - 2fOUT 554MHz -83 -64.1dBc -93 f<sub>DAC</sub>/8 -103 -113 -123

CENTER = 525MHz, SPAN = 1GHz, RBW = 10kHz, VBW = 1Hz, SWEEP = 101s

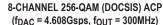

$(V_{AVDD33} = 3.3V, V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V, V_{DD10} = 1.0V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{CLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega$ , transformer-coupled differential output, DPD off, tests at  $T_J = +60^{\circ}C$ , unless otherwise noted.)

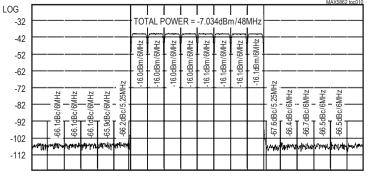

CENTER = 300MHz, SPAN = 120MHz, RBW = 20kHz, VBW = 2kHz, SWEEP = 7.449s

# 8-CHANNEL 256-QAM (DOCSIS) ACP (fDAC = 4.608Gsps, fOUT = 900MHz)

CENTER = 900MHz, SPAN = 120MHz, RBW = 20kHz, VBW = 2kHz, SWEEP = 7.449s

$(V_{AVDD33} = 3.3V, V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V, V_{DD10} = 1.0V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{CLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega, transformer-coupled differential output, DPD off, tests at T_J = +60°C, unless otherwise noted.)$

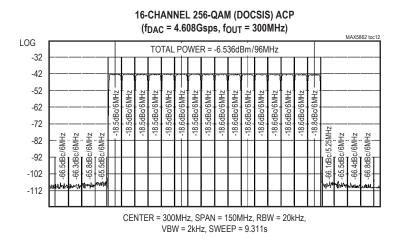

$(V_{AVDD33} = 3.3V, V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V, V_{DD10} = 1.0V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{CLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega, transformer-coupled differential output, DPD off, tests at T_J = +60°C, unless otherwise noted.)$

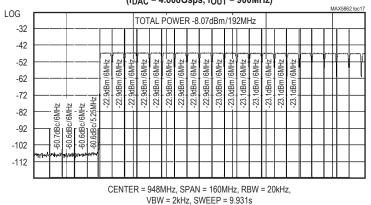

CENTER = 900MHz, SPAN = 160MHz, RBW = 20kHz, VBW = 2kHz, SWEEP = 9.931s

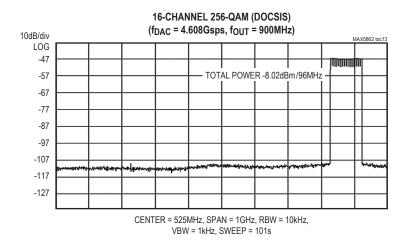

$(V_{AVDD33} = 3.3V, V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V, V_{DD10} = 1.0V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{CLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega, transformer-coupled differential output, DPD off, tests at T_J = +60°C, unless otherwise noted.)$

$(V_{AVDD33} = 3.3V, V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V, V_{DD10} = 1.0V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{CLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega$ , transformer-coupled differential output, DPD off, tests at  $T_{,1} = +60^{\circ}\text{C}$ , unless otherwise noted.)

# 32-CHANNEL 256-QAM (DOCSIS) ACP-UPPER CHANNELS (fDAC = 4.608Gsps, fOUT = 900MHz)

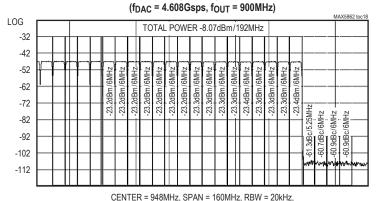

# 32-CHANNEL 256-QAM (DOCSIS) ACP-UPPER CHANNELS

VBW = 2kHz, SWEEP = 9.931s

$(V_{AVDD33} = 3.3V, V_{AVDD18} = V_{AVCLK} = V_{DD18} = V_{DD18L} = V_{DDDLL} = 1.8V, V_{DD10} = 1.0V, R_{SET} = 2k\Omega, V_{REFIO} = external 1.25V, V_{MOD} = V_{CLKDIV} = V_{DLLOFF} = 0V, V_{DELAY} = 1.8V, R_{REFRES} = 500\Omega, transformer-coupled differential output, DPD off, tests at T_J = +60°C, unless otherwise noted.)$

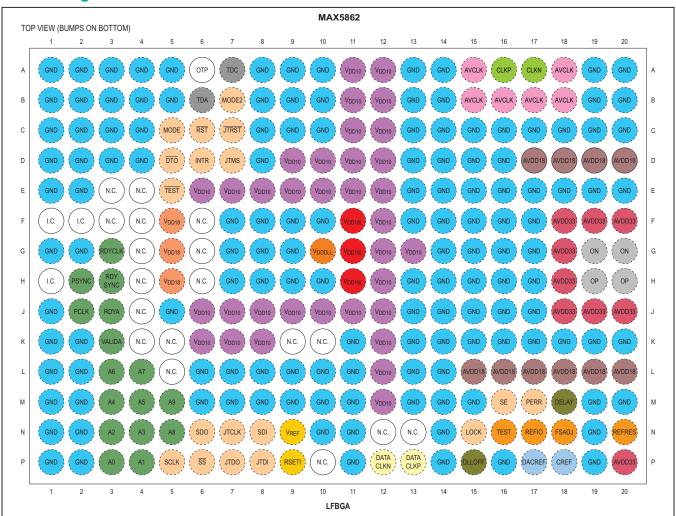

# **Ball Configuration**

## **Ball Description**

| BALL                                                                                                                                                                                                                                                                                                                                                     | NAME | FUNCTION                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------|

| A1–A5, A8–A10, A13, A14, A19, A20, B1–B5, B8–B10, B13, B14, B19, B20, C1–C4, C8–C10, C13–C20, D1–D4, D8, D13–D16, E1, E2, E13–E20, F7–F10, F13–F17, G1, G2, G7–G9, G14 –G17, H7–H10, H13–H17, J1, J5, J13–J17, K1, K2, K11, K13–K20, L1, L2, L6–L11, L13, L14, M1, M2, M6–M11, M13–M15, M19, M20, N1, N2, N10, N11, N14, N19, P1, P2, P11, P14, P16, P19 | GND  | Ground. Connect to ground plane with minimum inductance. P11 can be used as GND sense. |

| A6                                                                                                                                                                                                                                                                                                                                                       | OTP  | Manufacturer Test Pin. Connect to GND.                                                 |

| A7                                                                                                                                                                                                                                                                                                                                                       | TDC  | Temperature Diode Cathode Connection (MAX6642). Connect to GND.                        |

# **Ball Description (continued)**

| BALL                                                                                                    | NAME               | FUNCTION                                                                                                                                                       |  |

|---------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A11, A12, B11, B12, C11, C12,<br>D9–D12, E6–E12, F12, G12, G13,<br>H12, J6–J12, K6–K8, K12, L12,<br>M12 | V <sub>DD10</sub>  | Core V <sub>DD</sub> (1.0V). A11 can be used as V <sub>DD10</sub> sense                                                                                        |  |

| A15, A18, B15–B18                                                                                       | AVCLK              | Clock 1.8V Supply Voltage. Connect 47nF bypass capacitors between each AVCLK pin and GND                                                                       |  |

| A16                                                                                                     | CLKP               | Positive Converter Clock Input. There is an internal $100\Omega$ termination resistor between CLKP and CLKN.                                                   |  |

| A17                                                                                                     | CLKN               | Negative Converter Clock Input. There is an internal $100\Omega$ termination resistor between CLKP and CLKN.                                                   |  |

| B6                                                                                                      | TDA                | Temperature Diode Anode Connection (MAX6642)                                                                                                                   |  |

| B7                                                                                                      | MODE2              | Test Mode Control Pin 2.                                                                                                                                       |  |

| C5                                                                                                      | MODE               | Manufacturing Test Pin. Connect to V <sub>DD18</sub> (logic 1).                                                                                                |  |

| C6                                                                                                      | RST                | Active-Low Global Reset (except JTAG)                                                                                                                          |  |

| C7                                                                                                      | JTRST              | Active-Low JTAG Reset (Internal $50k\Omega$ Pullup Resistor). This pin should be pulsed low at startup or connected in parallel with $\overline{\text{RST}}$ . |  |

| D5                                                                                                      | DTO                | Digital Test Output. External pullup resistor may be required if DTO output state is high-impedance.                                                           |  |

| D6                                                                                                      | ĪNTR               | Active-Low Interrupt Flag                                                                                                                                      |  |

| D7                                                                                                      | JTMS               | JTAG Mode Select (Internal 50kΩ Pullup Resistor)                                                                                                               |  |

| D17-D20, L15-L20                                                                                        | AVDD18             | Analog 1.8V Supply Voltage. Connect 47nF bypass capacitors between each AVDD18 pin and GND.                                                                    |  |

| E3, E4, F3, F4, F6, G4, G6, H4,<br>H6, J4, K4, K5, K9, K10, L5, N12,<br>N13, P10                        | N.C.               | No connection. Not internally connected.                                                                                                                       |  |

| E5                                                                                                      | TEST               | Active-Low Manufacturing Test Pin. Connect to V <sub>DD18</sub> (logic 1).                                                                                     |  |

| F1, F2, H1                                                                                              | I.C.               | Internally connected. Do not connect.                                                                                                                          |  |

| F5, G5, H5                                                                                              | V <sub>DD18</sub>  | CMOS I/O V <sub>DD</sub> (1.8V)                                                                                                                                |  |

| F11, G11, H11                                                                                           | V <sub>DD18L</sub> | LVDS I/O V <sub>DD</sub> (1.8V)                                                                                                                                |  |

| F18–F20, G18, H18, J18–J20,<br>P20                                                                      | AVDD33             | Analog 3.3V Supply Voltage. Connect 47nF bypass capacitors between each AVDD33 pin and GND.                                                                    |  |

| G3                                                                                                      | RDYCLK             | Port Delayed Ready Clock Output                                                                                                                                |  |

| G10                                                                                                     | V <sub>DDDLL</sub> | Dedicated V <sub>DD</sub> for DLL and LVDS Bias Generator (1.8V). Connect to 1.8V even if DLL is not used.                                                     |  |

| G19, G20                                                                                                | ON                 | Negative Terminal of Differential DAC Output. OUTN has an internal $25\Omega$ resistor to AVDD33.                                                              |  |

| H2                                                                                                      | PSYNC              | Common Port Sync Input                                                                                                                                         |  |

| H3                                                                                                      | RDYSYNC            | Port Delayed Ready Sync Output                                                                                                                                 |  |

| H19, H20                                                                                                | OP                 | Positive Terminal of Differential DAC Output. OUTN has an internal $25\Omega$ resistor to AVDD33.                                                              |  |

| J2                                                                                                      | PCLK               | Common Port Clock Input                                                                                                                                        |  |

| J3                                                                                                      | RDYA               | Port A Ready Output                                                                                                                                            |  |

# **Ball Description (continued)**

| BALL | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                 |  |

|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| K3   | VALIDA           | Valid A Data Input                                                                                                                                                                                                                                                                                                                       |  |

| L3   | A6               | Port A Input Symbol Data, Bit 6                                                                                                                                                                                                                                                                                                          |  |

| L4   | A7               | Port A Input Symbol Data, Bit 7                                                                                                                                                                                                                                                                                                          |  |

| M3   | A4               | Port A Input Symbol Data, Bit 4                                                                                                                                                                                                                                                                                                          |  |

| M4   | A5               | Port A Input Symbol Data, Bit 5                                                                                                                                                                                                                                                                                                          |  |

| M5   | A9               | Port A Input Symbol Data, Bit 9                                                                                                                                                                                                                                                                                                          |  |

| M16  | SE               | Scan Enable Input. Connect to GND for normal operation. See the <i>Thermal Management</i> section for more detail.                                                                                                                                                                                                                       |  |

| M17  | PERR             | 1.8V CMOS Logic-Level Parity Error Output. When a parity error is detected in the DAC input data, this pin is set high for a minimum of 48 f <sub>CLK</sub> data periods. This can be used to provide failure monitoring for the system. Note that this pin can pulse high when power is initially applied and before the DLL is locked. |  |