#### **MAX2771**

### Multiband Universal GNSS Receiver

## **General Description**

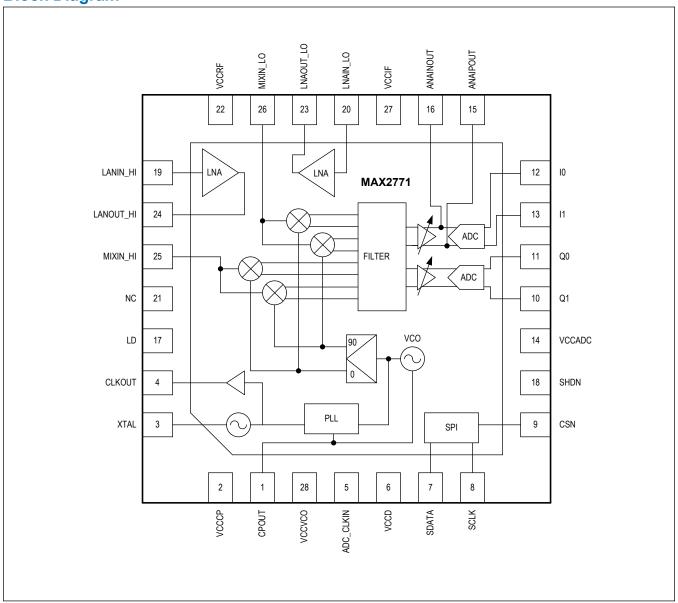

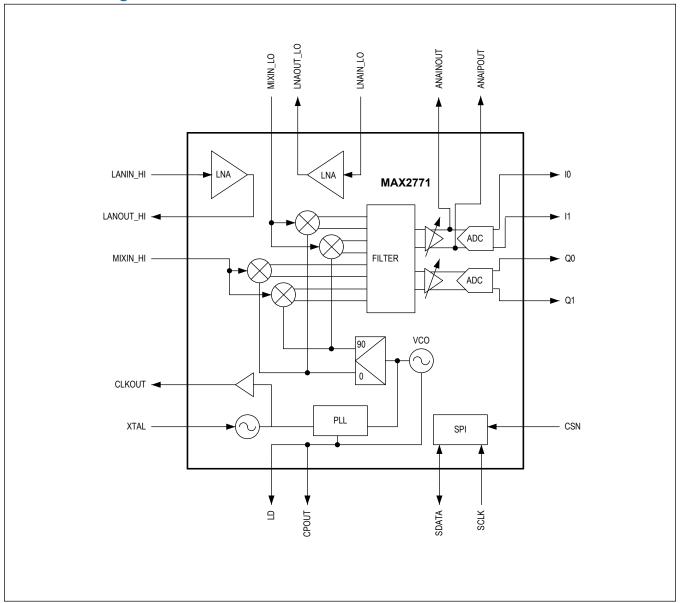

The MAX2771 is a next-generation Global Navigation Satellite System (GNSS) receiver covering E5/L5, L2, E6, E1/L1 bands and GPS, GLONASS, Galileo, QZSS, IRNSS, and BeiDou navigation satellite systems on a single chip.

Designed on Analog Devices' advanced, low-power SiGe BiCMOS process technology, the MAX2771 offers the highest performance and integration at a low cost. Incorporated on the chip is the complete receiver chain, including a dual-input LNA and mixer, followed by filter, PGA, and multi-bit ADC, along with a fractional-N frequency synthesizer, and crystal oscillator. The total cascaded noise figure of this receiver is as low as 1.4dB.

The MAX2771 completely eliminates the need for external IF filters by implementing on-chip monolithic filters and requires only a few external components to form a complete, low-cost GNSS RF receiver solution.

The MAX2771 is the most flexible receiver on the market. The integrated delta-sigma fractional-N frequency synthesizer allows programming of the IF frequency within a  $\pm 30$ Hz ( $f_{XTAL} = 32$ MHz) accuracy while operating with any reference or crystal frequencies that are available in the host system. The ADC outputs CMOS logic levels with one or two quantized bits for both I and Q channels, or up to 3 quantized bits for the I channel. The on-chip ADCs can be bypassed and the analog I and Q signals output for sampling with external ADCs. An analog monitoring feature is provided that allows simultaneous output of the on-chip ADC samples and the I analog signal.

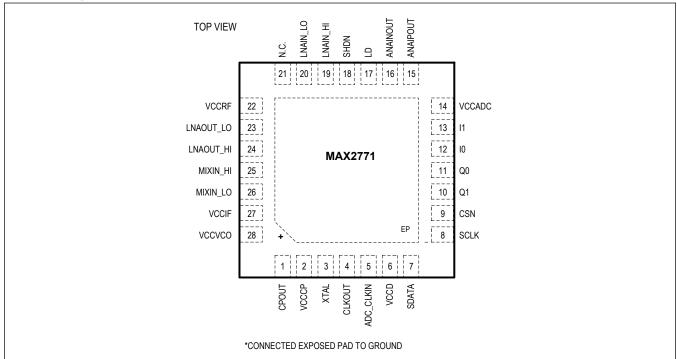

The MAX2771 is packaged in a 5mm  $\times$  5mm, 28-pin, TQFN package with an exposed paddle. It is also available as an unpackaged wafer die.

#### **Applications**

- Location-Enabled Mobile Handsets

- PNDs (Personal Navigation Devices)

- Telematics (Asset Tracking, Inventory Management)

- Marine/Avionics Navigation

- Software GPS

- Laptops and Netbooks

- Surveying Equipment

- Digital Still Cameras and Camcorders

- Vehicle Tracking and Fleet Management

#### **Benefits and Features**

- Multi-Constellation Support

- GPS, Galileo, GLONASS, BeiDou, IRNSS, QZSS, SBAS

- Multiband Support

- L1, L2, L5, E1, E5, E6, B1, B2, B3

- Programmable IF Bandwidths of 2.5MHz, 4.2MHz, 8.7MHz, 16.4MHz, 23.4MHz, 36MHz

- Supports Wide-Band Carriers for Precision Applications (e.g., GPS L5, Galileo E5)

- · Operates in Low-IF or Zero-IF Mode

- · Programmable IF Center Frequency

- Fractional-N Synthesizer with Integrated VCO Supports Wide Range of Reference Frequencies

- On-Chip LNAs to Support Multiple Bands

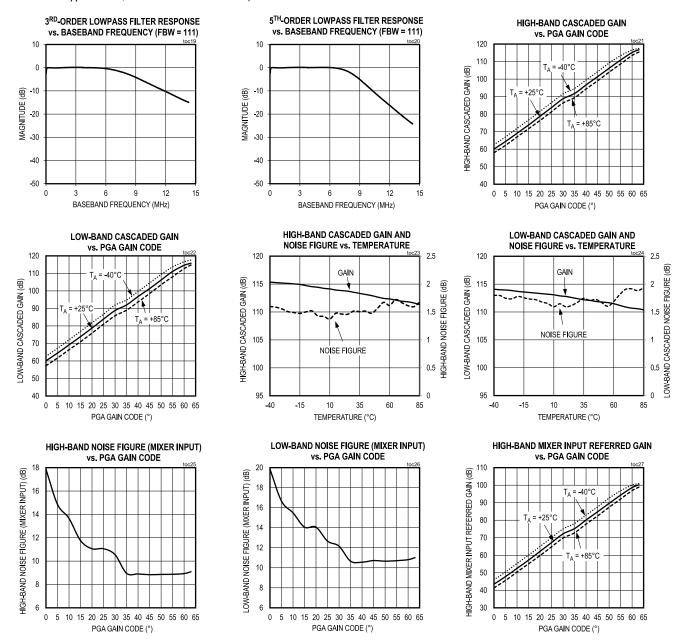

- 1.4dB Cascaded Noise Figure and 110dB of Cascaded Gain with Gain Control Range of 59dB from PGA

- Integrated Crystal Oscillator

- Supply Voltage Range: 2.7V to 3.3V

- 28-Pin, RoHS-Compliant, Thin QFN Lead-Free Package (5mm x 5mm)

- Wafer Die Option Available (2.6mm x 2.7mm)

www.datasheetall.com

Idle Mode is a trademark of Maxim Integrated Products, Inc.

Ordering Information appears at end of data sheet.

19-100378; Rev 2; 4/25

© 2025 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

# **Block Diagram**

## **TABLE OF CONTENTS**

| General Description                      | 1  |

|------------------------------------------|----|

| Applications                             | 1  |

| Benefits and Features                    | 1  |

| Block Diagram                            | 2  |

| Absolute Maximum Ratings                 | 7  |

| Package Information                      | 7  |

| 28 TQFN-EP                               | 7  |

| Electrical Characteristics               | 7  |

| Typical Operating Characteristics        | 12 |

| Pin Configuration                        | 15 |

| Pin Description                          | 16 |

| Functional Diagram                       | 17 |

| Detailed Description                     | 18 |

| Default Register Setting                 | 18 |

| Low-Noise Amplifier (LNA)                | 18 |

| Mixer                                    | 18 |

| Synthesizer                              | 19 |

| IF Filter                                | 20 |

| Programmable Gain Amplifier (PGA)        | 20 |

| Automatic Gain Control (AGC)             | 21 |

| ADC                                      | 21 |

| ADC Fractional Clock Divider             | 23 |

| ADC Clock Alignment                      | 24 |

| DSP Interface                            | 24 |

| Reference Clock                          | 25 |

| Serial Interface                         | 27 |

| Wafer Die Description                    | 29 |

| Register Map                             | 32 |

| Memory Map                               | 32 |

| Register Details                         | 33 |

| Applications Information                 | 45 |

| IF Filter Center Frequency Configuration | 45 |

| Operation for Wideband Signals           | 45 |

| Determining AGC Gain Setpoint            | 46 |

| PCB Layout Considerations                | 46 |

| Power-Supply Layout                      | 46 |

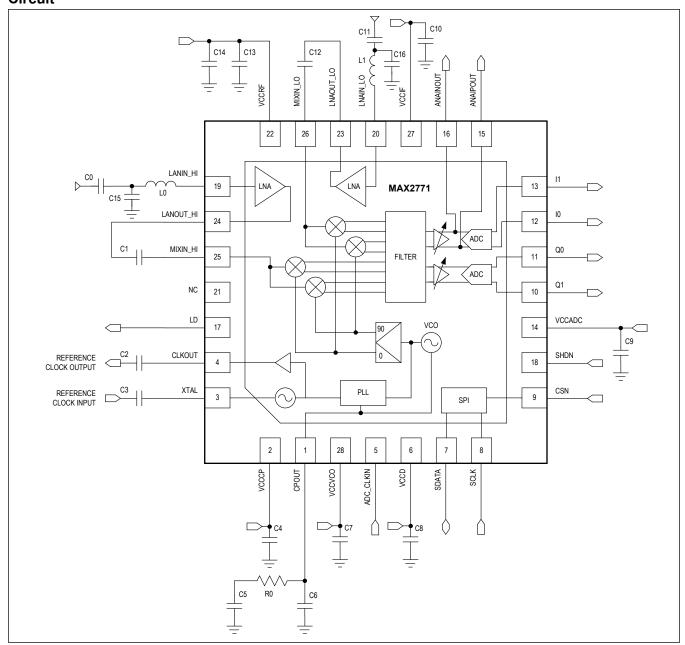

| Typical Application Circuits             | 47 |

| Circuit                                  | 47 |

| External Component List                  | 47 |

# MAX2771

# Multiband Universal GNSS Receiver

| TABLE OF CONTENTS (CONTINUED) |    |

|-------------------------------|----|

| Ordering Information          | 48 |

| Revision History              | 49 |

## LIST OF FIGURES

| Figure 1. ADC Quantization Levels for 2- and 3-Bit Cases           |      |

|--------------------------------------------------------------------|------|

| Figure 2. DSP Interface Top Level Connectivity and Control Signals | . 25 |

| Figure 3. Clock Distribution                                       | . 26 |

| Figure 4. Register Read Functional Timing                          | . 28 |

| Figure 5. Register Write Functional Timing                         | . 28 |

| Figure 6. Three-Wire Interface Timing Diagram                      | . 28 |

| Figure 7. Die Diagram                                              | . 29 |

# **LIST OF TABLES**

| Table 1. Required Register Bit Field Values                   | 18 |

|---------------------------------------------------------------|----|

| Fable 2. Default Register Setting                             | 18 |

| Fable 3. LNA Selection                                        | 18 |

| Fable 4. Mixer Selection                                      | 19 |

| Fable 5. IF Filter Mode Selection                             | 20 |

| Fable 6. IF Filter Order Selection                            | 20 |

| Fable 7. IF Filter Bandwidth Selection.                       | 20 |

| Fable 8. Gain Reference Settings                              | 21 |

| Fable 9. ADC Output Data Format Settings                      | 21 |

| Fable 10. IQ Channels Enable Settings                         | 21 |

| Fable 11. ADC Output Bits Setting                             | 21 |

| Fable 12. Output Data Format                                  | 22 |

| Fable 13. Frequency of ADC Sampling Clock vs. Reference Clock | 24 |

| Fable 14. Reference Divider Settings                          | 27 |

| Fable 15. Serial Interface Timing Requirements                | 28 |

| Fable 16. Die Pad Coordinates                                 | 30 |

## **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND0.3V to +4.2V                                   | Operating Temperature Range40°C to +85°C       |

|-----------------------------------------------------------------------|------------------------------------------------|

| MIXIN_ to GND0.3V to +0.3V                                            | Storage Temperature Range65°C to +150°C        |

| Other Pins to GND (Note 1)                                            | Junction Temperature+150°C                     |

| Maximum RF Input Power+15dBm                                          | Lead Temperature (Soldering, 10 seconds)+300°C |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C, derate 27 mW/°C |                                                |

| above +70°C.)                                                         |                                                |

Note 1: Except for LNAIN\_HI, LNAIN\_LO, MIXIN\_HI, MIXIN\_LO, XTAL, LNAOUT\_HI and LNAOUT\_LO

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 28 TQFN-EP

| Package Code        | T2855+8        |

|---------------------|----------------|

| Outline Number      | <u>21-0140</u> |

| Land Pattern Number | 90-0028        |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.analog.com/en/resources/packaging-quality-symbols-footprints/package-index.html">https://www.analog.com/en/resources/packaging-quality-symbols-footprints/package-index.html</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.analog.com/en/resources/technical-articles/thermal-characterization-of-ic-packages.html">https://www.analog.com/en/resources/technical-articles/thermal-characterization-of-ic-packages.html</a>.

#### **Electrical Characteristics**

$(V_{CC} = 2.7 \text{V to } 3.3 \text{V}, T_A = -40 ^{\circ}\text{C}$  to  $+85 ^{\circ}\text{C}$ . Registers are set to the specified default states. LNA input is driven from a  $50\Omega$  source. All RF measurements are done in the analog output mode with ADC bypassed. PGA gain is set to GAININ = 111010 through SPI interface, unless otherwise noted. Maximum IF output load is not to exceed  $10k\Omega||7.5pF$  on each pin. Typical values are at  $V_{CC} = 2.85V$  and  $T_A = +25 ^{\circ}\text{C}$ , unless otherwise noted. (Note 1))

| PARAMETER                                               | SYMBOL          | CONDITIONS                                                     | MIN | TYP     | MAX | UNITS |  |  |

|---------------------------------------------------------|-----------------|----------------------------------------------------------------|-----|---------|-----|-------|--|--|

| DC ELECTRICAL CHARACTERISTICS                           |                 |                                                                |     |         |     |       |  |  |

| Supply Voltage                                          | V <sub>CC</sub> |                                                                | 2.7 | 2.85    | 3.3 | V     |  |  |

|                                                         |                 | Default mode, high-band LNA and mixer input is active (Note 2) |     | 26      |     |       |  |  |

| Supply Current                                          |                 | Default mode, low-band LNA and mixer input is active (Note 2)  |     | 27      |     | mA    |  |  |

|                                                         |                 | Idle Mode <sup>TM</sup> , IDLE bit is 1, SHDN = high           |     | 5       |     | 1     |  |  |

|                                                         |                 | Shutdown mode, SHDN = low                                      |     | 200     |     | μA    |  |  |

| Digital Input Logic-High                                | V <sub>IH</sub> | Measure at the SHDN pin                                        | 1.5 |         |     | V     |  |  |

| Digital Input Logic-Low                                 | V <sub>IL</sub> | Measure at SHDN pin                                            |     |         | 0.4 | V     |  |  |

| AC ELECTRICAL CHARACTERISTICS / CASCADED RF PERFORMANCE |                 |                                                                |     |         |     |       |  |  |

| RF Frequency                                            |                 | L1 band                                                        |     | 1575.42 |     | MHz   |  |  |

| RF Frequency - L2/L5<br>Band                            |                 | L2/L5 band                                                     |     | 1227.6  |     | MHz   |  |  |

# **Electrical Characteristics (continued)**

$(V_{CC}$  = 2.7V to 3.3V,  $T_A$  = -40°C to +85°C. Registers are set to the specified default states. LNA input is driven from a 50Ω source. All RF measurements are done in the analog output mode with ADC bypassed. PGA gain is set to GAININ = 111010 through SPI interface, unless otherwise noted. Maximum IF output load is not to exceed  $10k\Omega||7.5pF$  on each pin. Typical values are at  $V_{CC}$  = 2.85V and  $T_A$  = +25°C, unless otherwise noted. (Note 1))

| PARAMETER                                                                 | SYMBOL | CONDITIONS                                                                                                | MIN | TYP  | MAX | UNITS |

|---------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Noise Figure                                                              |        | High band LNA input active, default mode (Note 3)                                                         |     | 1.4  |     | dB    |

| Noise Figure - L2/L5<br>Band                                              |        | L2/L5 band (Note 6). Low-band LNA input active, default mode (Note 3)                                     |     | 1.6  |     | dB    |

| Noise Figure                                                              |        | Measured at the high-band mixer input                                                                     |     | 10.3 |     | dB    |

| Noise Figure - L2/L5<br>Band                                              |        | L2/L5 band (Note 6). Measured at the low-band mixer input                                                 |     | 10.3 |     | dB    |

| Out-of-Band 3rd-Order<br>Input Intercept Point                            |        | Measured at the high-band mixer input (Note 4)                                                            |     | -9   |     | dBm   |

| Out-of-Band 3rd-Order<br>Input Intercept Point -<br>L2/L5 Band            |        | L2/L5 band (Note 6). Measured at the low-band mixer input (Note 4)                                        |     | -9   |     | dBm   |

| In-Band Mixer Input<br>Referred 1dB<br>Compression Point                  |        | Measured at the high-band mixer input                                                                     |     | -85  |     | dBm   |

| In-Band Mixer Input<br>Referred 1dB<br>Compression Point – L2/<br>L5 Band |        | L2/L5 band (Note 6). Measured at the low-band mixer input                                                 |     | -85  |     | dBm   |

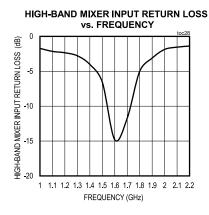

| Mixer Input Return Loss                                                   |        | Measured at high-band mixer input                                                                         |     | 10   |     | dB    |

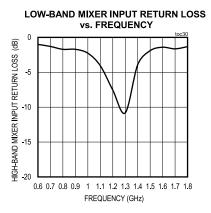

| Mixer Input Return Loss - L2/L5 Band                                      |        | Measured at low-band mixer input                                                                          |     | 8    |     | dB    |

| Image Rejection                                                           |        |                                                                                                           |     | 25   |     | dB    |

| Image Rejection - L2/L5<br>Band                                           |        | L2/L5 band (Note 6)                                                                                       |     | 25   |     | dB    |

| Spurs at High-Band LNA Input                                              |        | LO leakage                                                                                                |     | -101 |     | dBm   |

| Spurs at Low-Band LNA Input                                               |        | L2/L5 band (Note 6). LO leakage                                                                           |     | -101 |     | dBm   |

| Spurs at High-Band LNA Input                                              |        | Reference harmonics leakage                                                                               |     | -103 |     | dBm   |

| Spurs at Low-Band LNA Input                                               |        | L2/L5 band (Note 6). Reference harmonics leakage                                                          |     | -103 |     | dBm   |

| Maximum Voltage Gain                                                      |        | Measured from the high-band mixer input to the baseband analog output                                     | 89  | 96   | 104 | dB    |

| Maximum Voltage Gain for Die Parts                                        |        | Measured from the high-band mixer input to the baseband analog output; die parts only                     | 83  | 96   | 106 | dB    |

| Maximum Voltage Gain<br>- L2/L5 Band                                      |        | L2/L5 band (Note 6). Measured from the low-band mixer input to the baseband analog output                 | 89  | 96   | 104 | dB    |

| Maximum Voltage Gain for Die Parts - L2/L5 Band                           |        | L2/L5 band (Note 6). Measured from the low-band mixer input to the baseband analog output; die parts only | 83  | 96   | 106 | dB    |

# **Electrical Characteristics (continued)**

$(V_{CC}$  = 2.7V to 3.3V,  $T_A$  = -40°C to +85°C. Registers are set to the specified default states. LNA input is driven from a 50Ω source. All RF measurements are done in the analog output mode with ADC bypassed. PGA gain is set to GAININ = 111010 through SPI interface, unless otherwise noted. Maximum IF output load is not to exceed  $10k\Omega||7.5pF$  on each pin. Typical values are at  $V_{CC}$  = 2.85V and  $T_A$  = +25°C, unless otherwise noted. (Note 1))

| PARAMETER                               | SYMBOL        | CONDITIONS                                                                                                                          | MIN | TYP  | MAX | UNITS |

|-----------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| Variable Gain Range                     |               | Measured at high-band mixer input                                                                                                   | 53  | 59   |     | dB    |

| Variable Gain Range for Die Parts       |               | Measured at high-band mixer input; die parts only                                                                                   | 45  | 59   |     | dB    |

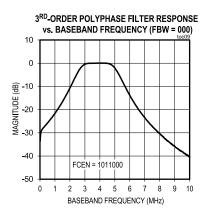

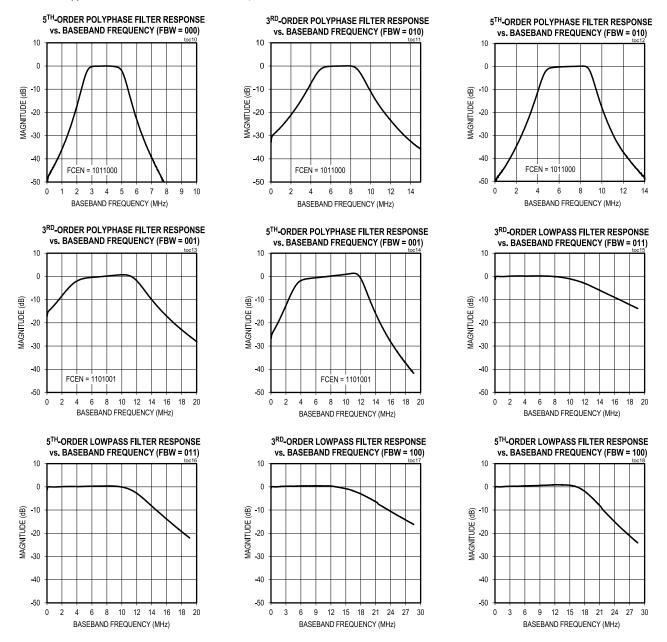

| AC ELECTRICAL CHARA                     | ACTERISTICS / | FILTER RESPONSE                                                                                                                     |     |      |     |       |

|                                         |               | FBW = 000, FCEN = 1011000 (Note 7)                                                                                                  |     | 3.9  |     |       |

| Passband Center<br>Frequency            |               | FBW = 010, FCEN = 1011000 (Note 7)                                                                                                  |     | 7.1  |     | MHz   |

| requericy                               |               | FBW = 001, FCEN = 1101001 (Note 7)                                                                                                  |     | 7.6  |     | 1     |

| - · · · · · · · · · · · · · · · · · · · |               | FBW = 000 (Note 7)                                                                                                                  |     | 2.5  |     |       |

| Passband 3dB<br>Bandwidth               |               | FBW = 010 (Note 7)                                                                                                                  |     | 4.2  |     | MHz   |

| Banawiatii                              |               | FBW = 001 (Note 7)                                                                                                                  |     | 8.7  |     | 1     |

|                                         |               | FBW = 011, single-sided BW (Note 7)                                                                                                 |     | 11.7 |     |       |

| Lowpass 3dB Bandwidth                   |               | FBW = 111, single-sided BW (Note 7)                                                                                                 |     | 8.2  |     | MHz   |

|                                         |               | FBW = 100, single-sided BW (Note 7)                                                                                                 |     | 18   |     | 1     |

| Stanband Attanuation                    |               | 3rd-order filter, bandwidth = 2.5MHz,<br>measured at 4MHz offset (Note 7)                                                           |     | 30   |     | 10    |

| Stopband Attenuation                    |               | 5th-order filter, bandwidth = 2.5MHz,<br>measured at 4MHz offset (Note 7)                                                           |     | 50   |     | - dB  |

| Passband Flatness                       |               | FBW = 001, filter center frequency = 8.9MHz, 5th-order BPF,  response magnitude at 5.1MHz - response magnitude at 11.6MHz  (Note 7) |     | 3    |     | dB    |

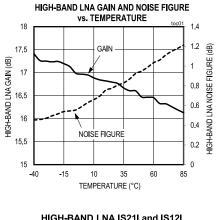

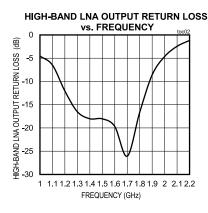

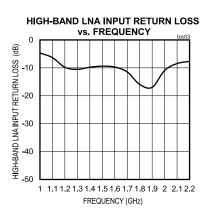

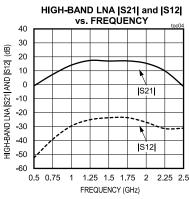

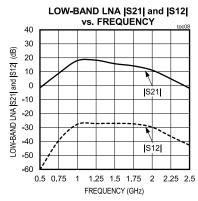

| AC ELECTRICAL CHARA                     | ACTERISTICS / | HIGH-BAND LNA                                                                                                                       |     |      |     |       |

| Power Gain                              |               |                                                                                                                                     |     | 18   |     | dB    |

| Power Gain for Die<br>Parts             |               | Die parts only                                                                                                                      |     | 15   |     | dB    |

| Noise Figure                            |               |                                                                                                                                     |     | 0.9  |     | dB    |

| Input IP3                               |               | (Note 5)                                                                                                                            |     | -1.1 |     | dBm   |

| Output Return Loss                      |               |                                                                                                                                     |     | 10   |     | dB    |

| Input Return Loss                       |               | With external matching circuit components of 5.6nH series inductor and 1.7pF shunt capacitor.                                       |     | 10   |     | dB    |

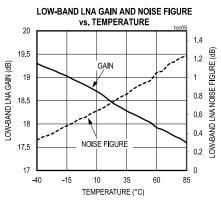

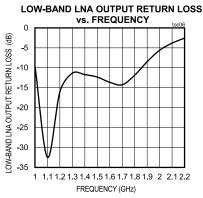

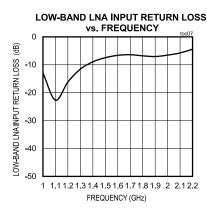

| AC ELECTRICAL CHARA                     | ACTERISTICS / | LOW-BAND LNA                                                                                                                        |     |      |     |       |

| Power Gain                              |               |                                                                                                                                     |     | 18   |     | dB    |

| Power Gain for Die<br>Parts             |               | Die parts only                                                                                                                      |     | 16   |     | dB    |

| Noise Figure                            |               |                                                                                                                                     |     | 0.9  |     | dB    |

| Input IP3                               |               | (Note 5)                                                                                                                            |     | -1.1 |     | dBm   |

| Output Return Loss                      |               |                                                                                                                                     |     | 10   |     | dB    |

| Input Return Loss                       |               | With external matching circuit components of 8.4nH series inductor and 1.1pF shunt capacitor.                                       |     | 8    |     | dB    |

### **Electrical Characteristics (continued)**

$(V_{CC}$  = 2.7V to 3.3V,  $T_A$  = -40°C to +85°C. Registers are set to the specified default states. LNA input is driven from a 50Ω source. All RF measurements are done in the analog output mode with ADC bypassed. PGA gain is set to GAININ = 111010 through SPI interface, unless otherwise noted. Maximum IF output load is not to exceed  $10k\Omega||7.5pF$  on each pin. Typical values are at  $V_{CC}$  = 2.85V and  $T_A$  = +25°C, unless otherwise noted. (Note 1))

| PARAMETER                              | SYMBOL        | CONDITIONS                                                              | MIN   | TYP  | MAX    | UNITS            |

|----------------------------------------|---------------|-------------------------------------------------------------------------|-------|------|--------|------------------|

| AC ELECTRICAL CHARA                    | ACTERISTICS / | FREQUENCY SYNTHESIZER                                                   | •     |      |        | •                |

| LO Frequency Range                     |               | 0.2V < V <sub>TUNE</sub> < (V <sub>CC</sub> - 0.25V), LOBAND<br>= 0     | 1525  |      | 1610   | MHz              |

| LO Frequency Range -<br>L2/L5 Band     |               | 0.2V < V <sub>TUNE</sub> < (V <sub>CC</sub> - 0.25V), LOBAND<br>= 1     | 1160  |      | 1290   | MHz              |

| LO Tuning Gain                         |               |                                                                         |       | 70   |        | MHz/V            |

| LO Tuning Gain - L2/L5<br>Band         |               |                                                                         |       | 76   |        | MHz/V            |

| Reference Input<br>Frequency           |               |                                                                         | 8     |      | 44     | MHz              |

| Main Divider Ratio                     |               |                                                                         | 36    |      | 32,767 | -                |

| Reference Divider Ratio                |               |                                                                         | 1     |      | 1023   | -                |

| Charge-Pump Current                    |               | ICP = 0                                                                 |       | 0.5  |        | m A              |

|                                        |               | ICP = 1                                                                 |       | 1    |        | mA mA            |

| AC ELECTRICAL CHARA                    | ACTERISTICS / | TXCO INPUT BUFFER/OUTPUT CLOCK BI                                       | UFFER |      |        | •                |

| Frequency Range                        |               | Load = 10kΩ  10pF                                                       | 8     |      | 44     | MHz              |

| Output High Level                      |               | With respect to ground, I <sub>OH</sub> = 10μA (DC-coupled)             | 2     |      |        | V                |

| Output High Level for Die Parts        |               | With respect to ground, $I_{OH} = 10\mu A$ (DC-coupled); die parts only |       | 2    |        | V                |

| Output Low Level                       |               | With respect to ground, I <sub>OL</sub> = 10μA (DC-coupled)             |       |      | 0.8    | V                |

| Capacitive Slew Current                |               | Load = 10kΩ  10pF, f <sub>CLKOUT</sub> = 44MHz                          |       | 11   |        | mA               |

| Output Load                            |               |                                                                         |       |      | 10  10 | kΩ  pF           |

| Reference Input Level                  |               | Sine wave                                                               | 0.5   |      |        | V <sub>P-P</sub> |

| Clock Output Multiply/<br>Divide Range |               | x2: max input frequency of 22MHz,<br>x4: max input frequency of 11MHz   | /4    |      | x4     | -                |

| AC ELECTRICAL CHAR                     | ACTERISTICS / | ADC                                                                     |       |      |        |                  |

| ADC Differential<br>Nonlinearity       |               | AGC enabled, 3-bit output                                               |       | ±0.1 |        | LSB              |

| ADC Integral<br>Nonlinearity           |               | AGC enabled, 3-bit output                                               |       | ±0.1 |        | LSB              |

- Note 1: MAX2771 is production tested at  $T_A$  = +25°C. User must program the registers to the specified default settings upon power-up.

- Note 2: Default mode of the IC. PLL is an an integer-N mode with f<sub>COMP</sub> = f<sub>TCXO</sub>/16 = 1.023MHz and I<sub>CP</sub> = 0.5mA. The complex IF filter is configured as a 5th-order Butterworth filter with a center frequency of 4MHz and bandwidth of 2.5MHz. Output data is in a 2-bit sign/magnitude format at CMOS logic levels in the I channel only.

- Note 3: The LNA output connects to the mixer input without a SAW filter between them.

- Note 4: Two tones are located at 12MHz and 24MHz offset frequencies from the GPS center frequency of 1575.42MHz or 1227.6MHz depending on band. Passive pole at the mixer output is programmed to be 13MHz.

- Note 5: Measured from the LNA input to the LNA output. Two tones are located at 12MHz and 24MHz offset frequencies from the GPS center frequency of 1575.42MHz or 1227.6MHz depending on band.

# MAX2771

# Multiband Universal GNSS Receiver

Note 6: Same global conditions except tune LO to 1223.508MHz which means change PLL integer divider ratio to 1196 and program LOBAND bit to 1.

Note 7: Filter response measured with PGA gain setting of GAININ = 000100, and mixer pole set to 36MHz (MIXPOLE = 1).

## **Typical Operating Characteristics**

(MAX2771 EV kit,  $V_{CC}$  = 2.7V to 3.3V,  $T_A$  = -40°C to +85°C. Registers are set to the default power-up states. LNA input is driven from a 50Ω source. LNA input has specified external matching circuit. All RF measurements are done in the analog output mode with ADC bypassed. PGA gain is set to GAININ = 111010 except for IF filter response plots in which case it is set to GAININ = 000100. For IF filter response plots, MIXPOLE = 1. Maximum IF output load is not to exceed  $10k\Omega||7.5pF$  on each pin. Typical values are at  $V_{CC}$  = 2.85V and  $T_A$  = +25°C, unless otherwise noted.)

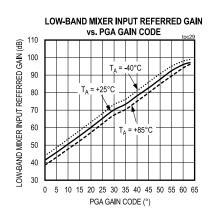

## **Typical Operating Characteristics (continued)**

(MAX2771 EV kit,  $V_{CC}$  = 2.7V to 3.3V,  $T_A$  = -40°C to +85°C. Registers are set to the default power-up states. LNA input is driven from a 50Ω source. LNA input has specified external matching circuit. All RF measurements are done in the analog output mode with ADC bypassed. PGA gain is set to GAININ = 111010 except for IF filter response plots in which case it is set to GAININ = 000100. For IF filter response plots, MIXPOLE = 1. Maximum IF output load is not to exceed  $10k\Omega||7.5pF$  on each pin. Typical values are at  $V_{CC}$  = 2.85V and  $T_A$  = +25°C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

(MAX2771 EV kit,  $V_{CC}$  = 2.7V to 3.3V,  $T_A$  = -40°C to +85°C. Registers are set to the default power-up states. LNA input is driven from a 50Ω source. LNA input has specified external matching circuit. All RF measurements are done in the analog output mode with ADC bypassed. PGA gain is set to GAININ = 111010 except for IF filter response plots in which case it is set to GAININ = 000100. For IF filter response plots, MIXPOLE = 1. Maximum IF output load is not to exceed  $10k\Omega||7.5pF$  on each pin. Typical values are at  $V_{CC}$  = 2.85V and  $T_A$  = +25°C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

(MAX2771 EV kit,  $V_{CC}$  = 2.7V to 3.3V,  $T_A$  = -40°C to +85°C. Registers are set to the default power-up states. LNA input is driven from a 50Ω source. LNA input has specified external matching circuit. All RF measurements are done in the analog output mode with ADC bypassed. PGA gain is set to GAININ = 111010 except for IF filter response plots in which case it is set to GAININ = 000100. For IF filter response plots, MIXPOLE = 1. Maximum IF output load is not to exceed  $10k\Omega||7.5pF$  on each pin. Typical values are at  $V_{CC}$  = 2.85V and  $T_A$  = +25°C, unless otherwise noted.)

# **Pin Configuration**

# **Pin Description**

| PIN | NAME      | FUNCTION                                                                                                                                                                                             | TYPE                     |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 1   | CPOUT     | Charge-Pump Output. Connect a PLL loop filter as a shunt C and a shunt combination of series R and C (see <i>Typical Application Circuit</i> ).                                                      | Analog output            |

| 2   | VCCCP     | PLL Charge-Pump Supply Voltage. Bypass to ground with a 100nF capacitor as close as possible to the pin.                                                                                             | Power                    |

| 3   | XTAL      | XTAL or Reference Oscillator Input. Connect to XTAL or a DC-blocking capacitor if a TCXO is used.                                                                                                    | Analog input             |

| 4   | CLKOUT    | Reference Clock Output.                                                                                                                                                                              | Digital output           |

| 5   | ADC_CLKIN | ADC Clock Input. Optionally, the ADCs can be clocked from the clock input on this pin. Refer to <u>ADC Clock Alignment</u> section for details.                                                      | Digital input            |

| 6   | VCCD      | Digital Circuitry Supply Voltage. Bypass to ground with a 100nF capacitor as close as possible to the pin.                                                                                           | Power                    |

| 7   | SDATA     | Data Signal of 3-Wire Serial Interface.                                                                                                                                                              | Digital input/<br>output |

| 8   | SCLK      | Clock Input of 3-Wire Serial Interface. Serial data is clocked in on the rising-edge of the SCLK and output on the falling-edge of SCLK.                                                             | Digital input            |

| 9   | CSN       | Chip-Select Input of 3-Wire Serial Interface. Set CSN low to select device. Set CS high when the SPI transaction is completed.                                                                       | Digital input            |

| 10  | Q1        | Q-Channel Voltage Outputs. Bits 0 and 1 of the Q-channel ADC output or analog differential voltage output.                                                                                           | Digital or analog output |

| 11  | Q0        | Q-Channel Voltage Outputs. Bits 0 and 1 of the Q-channel ADC output or analog differential voltage output.                                                                                           | Digital or analog output |

| 12  | 10        | I-Channel Voltage Outputs. Bits 0 and 1 of the I-channel ADC output or analog differential voltage output.                                                                                           | Digital or analog output |

| 13  | I1        | I-Channel Voltage Outputs. Bits 0 and 1 of the I-channel ADC output or analog differential voltage output.                                                                                           | Digital or analog output |

| 14  | VCCADC    | ADC Supply Voltage. Bypass to ground with a 100nF capacitor as close as possible to the pin.                                                                                                         | Power                    |

| 15  | ANAIPOUT  | Analog I+ Channel Output. This is used for the continuous spectrum monitoring function if the ANAIMON bit is set to 1. If continuous spectrum monitoring feature is not required, leave unconnected. | Analog output            |

| 16  | ANAINOUT  | Analog I- Channel Output. This is used for the continuous spectrum monitoring function if the ANAIMON bit is set to 1. If continuous spectrum monitoring feature is not required, leave unconnected. | Analog output            |

| 17  | LD        | Lock-Detector CMOS Logic Output. A logic-high indicates the PLL is locked.                                                                                                                           | Digital output           |

| 18  | SHDN      | Operation Control Logic Input. A logic-low shuts off the entire device.                                                                                                                              | Digital input            |

| 19  | LNAIN_HI  | High-Band LNA Input Port. Requires external matching circuit of 5.6nH series inductor and 1.7pF shunt capacitor.                                                                                     | Analog input             |

| 20  | LNAIN_LO  | Low-Band LNA Input Port. Requires external matching circuit of 8.4nH series inductor and 1.1pF shunt capacitor.                                                                                      | Analog input             |

| 21  | N.C.      | No Connection. Leave this pin unconnected.                                                                                                                                                           |                          |

| 22  | VCCRF     | RF Section Supply Voltage. Bypass to ground with 100nF and 100pF capacitors in parallel as close as possible to the pin.                                                                             | Power                    |

| 23  | LNAOUT_LO | Low-Band LNA Output. The LNA output is internally matched to $50\Omega$ for L2/L5 band.                                                                                                              | Analog output            |

| 24  | LNAOUT_HI | High-Band LNA Output. The LNA output is internally matched to $50\Omega$ for L1 band.                                                                                                                | Analog output            |

| 25  | MIXIN_HI  | High-Band Mixer Input. The mixer input is internally matched to 50Ω for L1 band.                                                                                                                     | Analog input             |

# **Pin Description (continued)**

| PIN | NAME     | FUNCTION                                                                                            | TYPE         |

|-----|----------|-----------------------------------------------------------------------------------------------------|--------------|

| 26  | MIXIN_LO | Low-Band Mixer Input. The mixer input is internally matched to $50\Omega$ for L2/L5 band.           | Analog input |

| 27  | VCCIF    | IF Section Supply Voltage. Bypass to ground with a 100nF capacitor as close as possible to the pin. | Power        |

| 28  | vccvco   | VCO Supply Voltage. Bypass to ground with a 100nF capacitor as close as possible to the pin.        | Power        |

# **Functional Diagram**

### **Detailed Description**

#### **Default Register Setting**

The registers will contain the reset values specified in the Register Map section of the data sheet upon power-up. It is necessary for certain bit fields in particular registers to be programmed with fixed values that are different from the power-on reset values. These register bit fields and the required values are given in <a href="Table 1">Table 1</a>. These values must be programmed whenever the IC is power-cycled. Note that these bits are described as "Reserved" in the data sheet. Nevertheless, for these reserved bits alone, the values indicated must be programmed.

**Table 1. Required Register Bit Field Values**

| REGISTER ADDRESS | BIT RANGE | BINARY VALUE |

|------------------|-----------|--------------|

| 0x0              | 29:22     | 11111010     |

| 0x9              | 24:22     | 011          |

<u>Table 2</u> includes the default register bit values with the above specified bits programmed, as in <u>Table 1</u>.

**Table 2. Default Register Setting**

| REGISTER NAME                 | ADDRESS        | DEFAULT    |  |  |

|-------------------------------|----------------|------------|--|--|

| Configuration 1               | 0x0            | 0xBEA41603 |  |  |

| Configuration 2               | 0x1            | 0x20550288 |  |  |

| Configuration 3               | 0x2            | 0x0EAFA1DC |  |  |

| PLL Configuration             | 0x3            | 0x698C0008 |  |  |

| PLL Integer Division Ratio    | 0x4 0x00C00080 |            |  |  |

| PLL Fractional Division Ratio | 0x5 0x08000070 |            |  |  |

| DSP Interface                 | 0x6            | 0x0800000  |  |  |

| Clock Configuration 1         | 0x7            | 0x010061B2 |  |  |

| Test Mode 1                   | 0x8            | 0x01E0F401 |  |  |

| Test Mode 2                   | 0x9            | 0x00C00002 |  |  |

| Clock Configuration 2         | 0xA            | 0x010061B0 |  |  |

#### Low-Noise Amplifier (LNA)

The MAX2771 integrates two low-noise amplifiers, one for the L1 band (high band) and the other for the L2/L5 band (low band). Both inputs require AC-coupling capacitors. Bits LNAMODE in the Configuration 1 register control the modes of the two LNAs. See <u>Table 2</u>. The high-band LNA input impedance is matched to  $50\Omega$  at a frequency of 1575MHz, providing the specified high-band external matching circuit is used. The low-band LNA input impedance is matched to  $50\Omega$  at a frequency of 1227MHz, providing the specified low-band external matching circuit is used.

The output of each LNA is brought out to a separate pin. The output impedance of the high-band LNA is matched to  $50\Omega$  at frequency of 1575MHz, and the low-band LNA input impedance is matched to  $50\Omega$  at a frequency of 1227MHz.

**Table 3. LNA Selection**

| LNA MODE (CONFIGURATION 1 REGISTER) | MODE                           |

|-------------------------------------|--------------------------------|

| 00                                  | LNA_HI is active               |

| 01                                  | LNA_LO is active               |

| 10                                  | Both LNA_HI and LNA_LO are off |

| 11                                  | RESERVED                       |

#### Mixer

The MAX2771 includes a quadrature mixer to output low-IF, or zero-IF, I and Q signals. There are two inputs to the mixer;

one for high-band and the other for low-band. The high-band mixer input impedance is matched to  $50\Omega$  at a frequency of 1575MHz, while the low-band mixer input impedance is matched to  $50\Omega$  at a frequency of 1227MHz. The quadrature mixer requires a low-side LO injection. The output of the LNA and the input of the mixer are brought off-chip to facilitate the use of a SAW filter. On the MAX2771, the RF signal has been made accessible between the first LNA stage output and mixer input. If filtering is not desired, these pins can be connected through a coupling capacitor. However, filtering introduced at this point has minimal effect on the excellent sensitivity of the receiver. For example, for typical device parameters, a SAW filter with 1dB insertion loss would degrade cascaded NF (and therefore receiver sensitivity) by only about 0.15dB. While no external filtering is required for stand-alone applications, coexistence with cellular or Wi-Fi transmissions in close proximity may require additional filtering to prevent compressing the receiver front-end. The mixer is configured for the desired band by the MIXERMODE[1:0] bits. See Table 4.

**Table 4. Mixer Selection**

| MIXERMODE (CONFIGURATION 1 REGISTER) | MODE                    |

|--------------------------------------|-------------------------|

| 00                                   | High-band mixer enabled |

| 01                                   | Low-band mixer enabled  |

| 10                                   | Both mixers disabled    |

| 11                                   | RESERVED                |

### Synthesizer

The MAX2771 integrates a 20-bit, sigma-delta, fractional-N synthesizer allowing the device to tune to a required LO frequency with an accuracy of approximately  $\pm 30$ Hz (when  $f_{XTAL} \leq 32$ MHz). The synthesizer includes a 10-bit reference divider with a divisor range programmable from 1 to 1023, a 15-bit integer portion main divider with a divisor range programmable from 36 to 32767, and also a 20-bit fractional portion main divider. The reference divider is programmable through the RDIV bits in the PLL Integer Division Ratio register, and can accommodate reference frequencies from 8MHz to 44MHz. The reference divider needs to be configured so the Phase Frequency Detector comparison frequency falls between 0.05MHz and 32MHz. In Integer-N mode, if the integer division ratio is divisible by 32, setting the PWRSAV bit of the PLL Configuration Register to 1 will reduce the power consumed by the PLL.

The PLL loop filter is the only external block of the synthesizer. A typical PLL filter is the classic C-R-C network at the charge-pump output. For example, see the  $\underline{Typical\ Application\ Circuit}$  for the recommended loop filter component values for  $f_{COMP} = 1.023 MHz$  and loop bandwidth = 56 kHz, with charge pump current of 0.5 mA and L1 band VCO. To calculate the loop filter component values for different LO frequencies, refer to the Design & Development section of the  $\underline{MAX2771}$   $\underline{product\ page}$ . The desired integer and fractional divider ratios can be calculated by dividing the LO frequency ( $f_{LO}$ ) by  $f_{COMP}$ .  $f_{COMP}$  can be calculated by dividing the TCXO frequency,  $f_{TCXO}$ , by the PLL reference division ratio,  $R_{DIV}$ . For example, let the TCXO frequency be 20MHz,  $R_{DIV}$  be 1, and the nominal LO frequency be 1575.42MHz. The following method can be used when calculating divider ratios supporting various reference and comparison frequencies:

$$f_{\text{COMP}} = \frac{f_{\text{TCXO}}}{\text{RDIV}} = \frac{20\text{MHz}}{1} = 20\text{MHz}$$

$$\text{LO\_Frequency\_Divider} = \frac{f_{\text{LO}}}{f_{\text{COMP}}} = \frac{1575.42\text{MHz}}{20\text{MHz}} = 78.771$$

Integer Divider = 78(d) = 000 0000 0100 1110 (binary)

Fractional Divider =  $0.771 \times 2^{20} = 808452$  (decimal) =  $1100 \ 0101 \ 0110 \ 0000 \ 0100$

In the fractional mode, the synthesizer should not be operated with integer division ratios greater than 251.

There are two LO tuning bands provided. These are referred to as the L1 band and L2/L5 band respectively. The L1 band is designed for L1 and Commercial Mobile Satellite Services (CMSS) such as Inmarsat used for SBAS. The L2/L5 band is for L2 and L5 bands. The selection of a band is done by programming the LOBAND bit in the PLL Configuration register. For example, if the desired LO frequency is 1227.6MHz, since this falls into the L2/L5 band, set LOBAND = 1. Assuming the same comparison TCXO frequencies as the previous example, the PLL divider ratio would be set to 1227.6/20 = 61.38.

Integer Divider = 61(d) = 000 0000 0011 1101 (binary)

Fractional Divider =  $0.38 \times 2^{20} = 398459$  (decimal) =  $0110\ 0001\ 0100\ 0111\ 1011$

The LD output provides an indication of the PLL lock state. Note that the lock detector requires a reference clock in order to operate.

#### IF Filter

The IF filter of the receiver can be programmed to be a lowpass filter or a complex bandpass filter by setting the bit FCENX bit in the Configuration 1 register to either 0 for lowpass filter mode or 1 for bandpass filter mode. See <u>Table 5</u>.

**Table 5. IF Filter Mode Selection**

| FCENX (CONFIGURATION 1 REGISTER) | FILTER MODE |

|----------------------------------|-------------|

| 0                                | Lowpass     |

| 1                                | Bandpass    |

Also, the IF filter can be configured either as a 3rd-order Butterworth filter for reduced group delay or a 5th-order Butterworth filter for steeper out-of-band rejection by setting the bit F3OR5 either 1 or 0, respectively in the Configuration 1 register. See <u>Table 6</u>.

**Table 6. IF Filter Order Selection**

| F3OR5 (CONFIGURATION 1 REGISTER) | IF FILTER ORDER          |

|----------------------------------|--------------------------|

| 0                                | 5th-order<br>Butterworth |

| 1                                | 3rd-order<br>Butterworth |

The two-sided 3dB corner bandwidth can be selected to be 2.5MHz, 4.2MHz, 8.7MHz, 16.4MHz, 23.4MHz, or 36MHz by programming the FBW bits in the Configuration 1 register. See <u>Table 7</u>. When the FCENX bit in the Configuration 1 register is set to 1, the lowpass filter becomes a complex bandpass filter and the center frequency can be programmed with the FCEN bits in the Configuration 1 register. The IF center frequency is adjustable in 127 steps with the 7-bit FCEN value. See the <u>Applications Information</u> section of this document for information on how to configure the desired IF filter center frequency. If the filter is configured as a lowpass filter, the FCEN bits are ignored and the center frequency of the filter is at 0Hz.

The narrow-band filter settings are designed to pass the first null-to-first null main lobe of narrowband signals such as GPS L1 (2.046MHz) or Beidou B1 (4.092MHz). The 8.7MHz setting is for the GLONASS L1 band. The 16.4MHz setting is for signals having an intermediate bandwidth greater than the narrow band signals, but not as wide as the 20.46MHz wide signals. For example, Galileo E1 (14.3MHz) or Galileo E6 (10.23MHz). The 23.4MHz setting is for the wide-band signals typically having main lobe bandwidth of 20.46MHz; for example, GPS L1 P(Y), modernized GLONASS L3OC or BeiDou B2. Finally, the 36MHz setting is designed to allow simultaneous reception of two constellations, specifically GPS and GLONASS in either the L1 or L2 bands. Simultaneous reception of GPS L1 and GLONASS L1 provides a greater selection of visible satellites, which in turn allows faster time to fix and a more accurate navigation solution.

Table 7. IF Filter Bandwidth Selection

| FBW (CONFIGURATION 1 REGISTER) | BANDWIDTH (DOUBLE-SIDED) |

|--------------------------------|--------------------------|

| 000                            | 2.5MHz                   |

| 010                            | 4.2MHz                   |

| 001                            | 8.7MHz                   |

| 011 (Lowpass mode only)        | 23.4MHz                  |

| 111 (Lowpass mode only)        | 16.4MHz                  |

| 100 (Lowpass mode only)        | 36.0MHz                  |

| All other settings             | RESERVED                 |

#### **Programmable Gain Amplifier (PGA)**

The MAX2771 integrates a baseband programmable gain amplifier that provides typically 59dB of gain control range. The PGA gain can either be controlled autonomously by the MAX2771 using the AGC function, or be directly controlled by the

host through programming of the GAININ bits in the Configuration 3 register. The AGCMODE bits in the Configuration 2 register are used to select the control mode for the PGA gain. The gain can be adjusted with approximately 1dB resolution.

#### **Automatic Gain Control (AGC)**

The MAX2771 provides a control loop that automatically programs the PGA gain to provide the ADC with an input power that optimally fills the converter and establishes a desired magnitude bit density at its output. The AGC algorithm operates by counting the number of magnitude bits over 512 ADC clock cycles and comparing the magnitude bit count to the reference value provided through a control word (GAINREF) in the Configuration 2 register. The desired magnitude bit density is expressed as a value of GAINREF in a decimal format divided by the counter length of 512. For example, to achieve the magnitude bit density of 33%, which is optimal for a 2-bit converter, program GAINREF to 170, since 170/512 = 33%. See Table 8.

### **Table 8. Gain Reference Settings**

| GAINREF (CONFIGURATION 2 REGISTER) | MAGNITUDE BIT DENSITY REFERENCE |

|------------------------------------|---------------------------------|

| 11101010                           | 234                             |

| 1010100                            | 84                              |

| 100111010                          | 314                             |

#### **ADC**

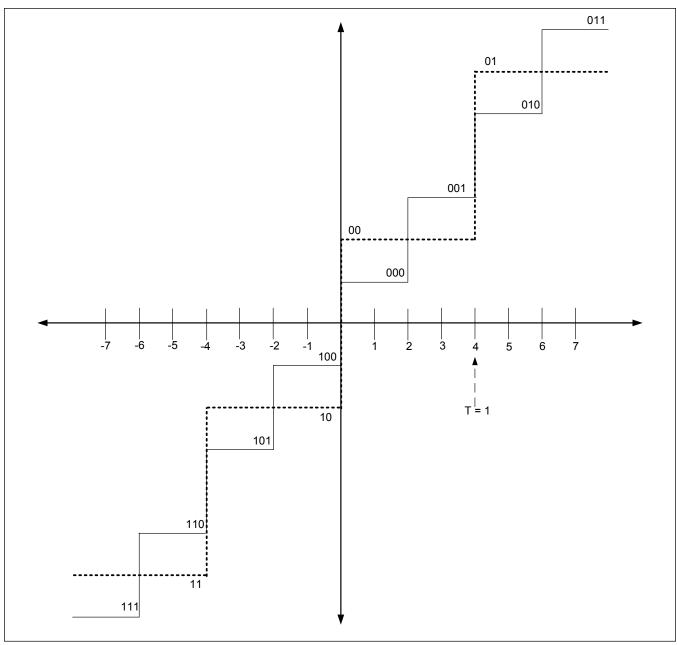

The MAX2771 features an on-chip ADC to digitize the down-converted GNSS signal. The ADC supports the digital output in three different formats: unsigned binary, sign and magnitude, or two's complement format by setting the FORMAT bits in Configuration 2 register. See <a href="Table 9">Table 9</a>. The sampled output is provided in a 2-bit format (1-bit magnitude and 1-bit sign) by default, and also can be configured as 1-bit or 2-bit in both I and Q channels, or 1-bit, 2-bit, or 3-bit in the I channel only. If only the I channel is used, the Q channel can be disabled with the IQEN bits in the Configuration 2 register. See <a href="Table 10">Table 10</a>. MSB bits are output on the I1 or Q1 pins and LSB bits are output on the I0 or Q0 pins, for I or Q channel, respectively. In the case of 3-bit output data format, the MSB is output on I1, the second bit is on I0, and the LSB is on Q1. The Q ADC must be enabled in 3-bit output data mode by setting the IQEN bit to 1. The number of bits of the ADC can be configured through the BITS field in the Configuration 2 register. See <a href="Table 11">Table 11</a>. Figure 1 illustrates the ADC quantization levels for 2-bit and 3-bit cases and also describes the sign/magnitude data mapping. The variable T = 1 designates the location of the magnitude threshold for the 2-bit case. Also see <a href="Table 12">Table 12</a>. The maximum ADC sampling rate is 44MHz.

#### Table 9. ADC Output Data Format Settings

| FORMAT (CONFIGURATION 2 REGISTER) | ADC OUTPUT DATA FORMAT  |

|-----------------------------------|-------------------------|

| 00                                | Unsigned binary         |

| 01                                | Sign and magnitude      |

| 1X                                | Two's complement binary |

#### **Table 10. IQ Channels Enable Settings**

| IQEN (CONFIGURATION 2 REGISTER) | ENABLED CHANNEL       |

|---------------------------------|-----------------------|

| 0                               | I channel only        |

| 1                               | Both I and Q channels |

#### **Table 11. ADC Output Bits Setting**

| BITS (CONFIGURATION 2 REGISTER) | NUMBER OF BITS IN THE ADC |  |  |

|---------------------------------|---------------------------|--|--|

| 000                             | 1 bit                     |  |  |

| 010                             | 2 bits                    |  |  |

| 100                             | 3 bits                    |  |  |

**Table 12. Output Data Format**

| INTEGER | SIGN/MAGNITUDE |    |     | UNSIGNED BINARY |    |     | TWO'S COMPLEMENT BINARY |    |     |

|---------|----------------|----|-----|-----------------|----|-----|-------------------------|----|-----|

| VALUE   | 1b             | 2b | 3b  | 1b              | 2b | 3b  | 1b                      | 2b | 3b  |

| 7       | 0              | 01 | 011 | 1               | 11 | 111 | 0                       | 01 | 011 |

| 5       | 0              | 01 | 010 | 1               | 11 | 110 | 0                       | 01 | 010 |

| 3       | 0              | 00 | 001 | 1               | 10 | 101 | 0                       | 00 | 001 |

| 1       | 0              | 00 | 000 | 1               | 10 | 110 | 0                       | 00 | 000 |

| -1      | 1              | 10 | 100 | 0               | 01 | 011 | 1                       | 11 | 111 |

| -3      | 1              | 10 | 101 | 0               | 01 | 010 | 1                       | 11 | 110 |

| -5      | 1              | 11 | 110 | 0               | 00 | 001 | 1                       | 10 | 101 |

| -7      | 1              | 11 | 111 | 0               | 00 | 000 | 1                       | 10 | 100 |

Figure 1. ADC Quantization Levels for 2- and 3-Bit Cases

#### **ADC Fractional Clock Divider**

A 12-bit fractional clock divider is located in the clock path prior to the ADC and can be used to generate an ADC clock that is a fraction of the reference input clock. In fractional divider mode, the instantaneous division ratio alternates between integer division ratios to achieve the required fraction. For example, if the fractional output clock is 4.5 times lower frequency than the input clock, an average division ratio of 4.5 is achieved through an equal series of alternating divide-by-4 and divide-by-5 periods. The fractional division ratio is given by:

$f_{OUT}/f_{IN} = LCOUNT/(4096 - MCOUNT + LCOUNT)$

where LCOUNT and MCOUNT are the 12-bit counter values in the Clock Configuration 2 register. The fractional division

ratio cannot exceed 0.5. This divider can be enabled or bypassed by using the FCLKIN bit in the Clock Configuration 1 register. Also the sampling clock, ADCCLK, can be taken either before or after the Reference Clock Divider/Multiplier depending on the ADCCLK bit setting. See <u>Table 13</u>. Note that REFCLK in this table is possibly the output of the REFCLK fractional divider.

Moreover, it is possible to take the ADC clock from outside the IC. If the EXTADCCLK bit in the Clock Configuration 1 register is 1, the ADC clock will be taken from the ADC\_CLKIN pin instead of using the internally generated clock. This allows simple synchronization of multiple MAX2771 ICs to a common ADC sampling clock.

Table 13. Frequency of ADC Sampling Clock vs. Reference Clock

| FCLKIN (FRACTIONAL CLOCK DIVISION RATIO REGISTER) | ADCCLK (FRACTIONAL CLOCK DIVISION RATIO REGISTER) | SAMPLING CLOCK<br>FREQUENCY           |

|---------------------------------------------------|---------------------------------------------------|---------------------------------------|

| 0                                                 | 0                                                 | /2,/4,x2,x4 REFCLK                    |

| 0                                                 | 1                                                 | REFCLK                                |

| 1                                                 | 0                                                 | /2,/4,x2,x4 REFCLK * Fractional_Ratio |

| 1                                                 | 1                                                 | REFCLK * Fractional_Ratio             |

#### **ADC Clock Alignment**

In the case where multiple MAX2771 devices are used in a system, and the ADCs are being clocked at the same rate, which is some fraction of the reference clock frequency, the ADC outputs of the devices will not necessarily be aligned in time. A baseband that is processing the outputs of multiple devices may need to include additional logic to align the ADC samples from each device.

To allow simple synchronization of the ADCs of each device, the ability to clock the ADCs from an externally applied clock is provided. If the EXTADCCLK bit in the Clock Configuration 1 register is 1, the ADC clock will be taken from the ADC\_CLKIN pin instead of using the internally generated clock. In a multiple MAX2771 scenario, all devices are assumed to be running off the same TCXO clock. One device would be designated as the clock source and configured to output its ADC clock on its CLKOUT pin. This clock signal can then be buffered and distributed through an external clock tree. The buffered clocks are then input on the ADC\_CLKIN pins of all MAX2771 devices (including the clock source), and all devices are configured to use this external clock as their ADC clock. Alternatively, the source of the clock may not necessarily be a MAX2771 but could be some clock source elsewhere in the system.

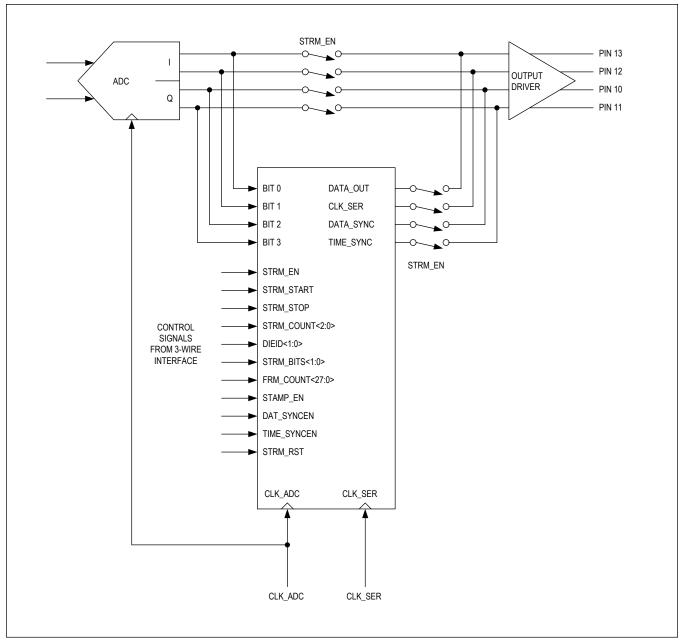

#### **DSP Interface**

GNSS data is output from the ADC as the four logic signals (bit0, bit1, bit2, and bit3) that represent sign/magnitude, unsigned binary, or two's complement binary data in the I (bit0 and bit1) and Q (bit2 and bit3) channels. The resolution of the ADC can be set up to 3 bits per channel. For example, the 2-bit I and Q data in sign/magnitude format is mapped as follows: bit0 = ISIGN, bit1 = IMAG, bit2 = QSIGN, and bit3 = QMAG. The data can be serialized in 16-bit segments of bit0, followed by bit1, bit2, and bit3. The number of bits to be serialized is controlled by the bits STRMBITS in the Configuration 3 register. This selects between bit0; bit0 and bit1; bit0 and bit2; and bit0, bit1, bit2, and bit3 cases. If only bit0 is serialized, the data stream consists of bit0 data only. If a serialization of bit0 and bit1 (or bit2) is selected, the stream data pattern consists of 16 bits of bit0 data, followed by 16 bits of bit1 (or bit2) data. This, in turn, is followed by 16 bits of bit0 data, and so on. In this case, the serial clock must be at least twice as fast as the ADC clock. If a 4-bit serialization of bit0, bit1, bit2, and bit3 is chosen, the serial clock must be at least four times faster than the ADC clock.

The ADC data is loaded, in parallel, into four holding registers that correspond to four ADC outputs. Holding registers are 16 bits long and are clocked by the ADC clock. At the end of the 16-bit ADC cycle, the data is transferred into four shift registers and shifted serially to the output during the next 16-bit ADC cycle. Shift registers are clocked by a serial clock that must be chosen fast enough so that all data is shifted out before the next set of data is loaded from the ADC. An all-zero pattern follows the data after all valid ADC data are streamed to the output. A DATASYNC signal is used to signal the beginning of each valid 16-bit data slice. In addition, there is a TIME\_SYNC signal that is output every 128 to 16,384 cycles of the ADC clock.

Given that the serial clock has to run multiple times faster than the ADC clock, the use of the DSP interface is limited to narrowband signals that do not require a high ADC sampling clock frequency.

Figure 2. DSP Interface Top Level Connectivity and Control Signals

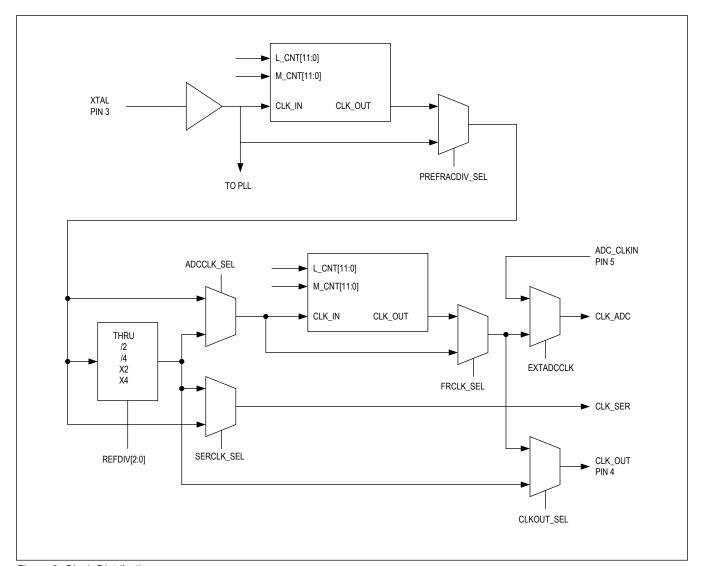

#### **Reference Clock**

The crystal clock input on pin 3 is used to generate internal clocks and a reference clock that is output to the baseband. The block diagram illustrating the clock distribution is shown in <a href="Figure 3">Figure 3</a>. There is a 12-bit fractional pre-divider that optionally allows division of the XTAL clock by some fractional amount. In the fractional divider mode, the instantaneous division ratio alternates between integer division ratios to achieve the required fraction. For example, if the fractional output clock is 4.5 times lower frequency than the input clock, an average division ratio of 4.5 is achieved through an equal series of alternating divide-by-4 and divide-by-5 periods. The fractional division ratio is given by:

$f_{OUT}/f_{IN} = LCOUNT/(4096 - MCOUNT + LCOUNT)$

where LCOUNT and MCOUNT are the 12-bit counter values in the Clock Configuration 1 register. The fractional division ratio cannot exceed 0.5. This divider can be enabled or bypassed by setting the PREFRACDIV\_SEL bit in the Clock Configuration 2 register to either 0 or 1.

The reference clock can then be optionally divided by either two or four, or multiplied by two or four. This is determined by the REFCLK bits in the PLL Configuration Register. See <u>Table 14</u>. This table ignores the fractional ratio. The maximum frequency of the pre-divided reference clock is 22MHz if the x2 option is selected, and 11MHz if the x4 option is selected. The ADC sampling clock can then be generated by a second fractional divider. This is described in the section on the ADC. The CLKOUT signal to the baseband can be selected to either be the output of the integer divider/multiplier block or the ADC clock. This selection is done through the CLKOUT SEL bit in the Clock Configuration 2 register.

The ADC clock can either be selected to be the internally generated clock, or taken from outside the IC. The EXTADCLK register bit selects whether the ADCs are clocked from the internally generated clock, or use the clock provided on the ADC\_CLKIN pin. This feature allows multiple MAX2771 devices connected to a common baseband IC to have synchronized ADC outputs.

The maximum clock frequency for any of these clocks is 44MHz.

Figure 3. Clock Distribution

| REFDIV (PLL CONFIGURATION REGISTER) | CLOCK OUTPUT      |

|-------------------------------------|-------------------|

| 000                                 | XTAL frequency x2 |

| 001                                 | XTAL frequency /4 |

| 010                                 | XTAL frequency /2 |

| 011                                 | XTAL frequency    |

| 100                                 | XTAL frequency x4 |

**Table 14. Reference Divider Settings**

#### **Serial Interface**

A serial interface is used to program the MAX2771 for configuring the different operating modes. The serial interface is controlled by three signals: SCLK (serial clock), CSN (chip select), and SDATA (serial data). The interface is based on the industry-standard Serial Peripheral Interface (SPI). The MAX2771 is a SPI slave and the device responsible for programming the MAX2771, such as a microprocessor or baseband controller, is the SPI controller. The SPI controller will be referred to henceforth as the "host". The host is responsible for driving SCLK, CSN, and SDATA. The MAX2771 only drives SDATA at certain times during the transaction so as to avoid bus contention with the controller.

The transfer of a set of data between host and MAX2771 is referred to as a "SPI transaction". An SPI transaction consists of 48 SCLK pulses. The base value of SCLK is low. Data on SDATA is output on the falling edge of SCLK and is sampled on the rising edge of SCLK by both host and the MAX2771.

The SDATA line is normally tri-stated by both the host and the MAX2771. It can only be driven by the MAX2771 during the latter part of a Read SPI transaction provided that CSN = 0. SDATA is driven by the host during the entire SPI transaction in the case of Write transactions, and only during the first part of Read transactions.

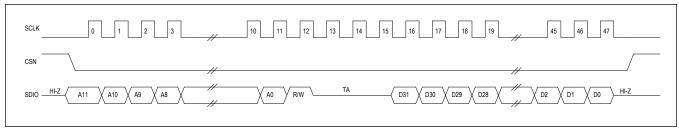

The first 12 bits transferred from host to the MAX2771 during an SPI transaction contain the address of the register to be accessed. The first 8 bits are always zero, while the last four bits are the address of the register. The 13th bit transferred from controller to MAX2771 is the R/W bit. If R/W = 1, the transaction is a read and the MAX2771 will drive SDATA in the latter part of the transaction. If R/W = 0, the transaction is a write, and the host will continue to drive SDATA for the remainder of the transaction. The 14th through 16th bits are turnaround bits that are denoted TA. The purpose of these bits is to allow time for the bus to change direction in the case of a read and so avoid any possible contention for the bus. In the case of a read transaction, the host releases SDATA during this interval, and the MAX2771 does not yet start driving SDATA. In the case of a write transaction, the host can continue to drive SDATA during this interval. The value of the bits is irrelevant (don't care). The remaining bits of the transaction are the data bits. The number of data bits will always be a 32 since all the registers in the MAX2771 are 32-bits wide.

Figure 4 shows a register read transaction. In this example, a 32 bit register is read by the host. The host first asserts CSN, begins driving SDATA with the register address preceded by 8 zeros and starts toggling SCLK. The MAX2771 samples the bits on SDATA on the rising edge of SCLK. After the address is output, the host outputs a R/W bit having value of 1 indicating this a read transaction. The next three bits are the TA bits during which the host releases the SDATA line. In this figure, SDATA is shown as tri-stated during this bit interval to emphasize that nothing is actively driving it. The MAX2771 can be configured to resistively pull up SDATA, pull it down, or apply a bus-hold during periods when it is not driving the bus. The MAX2771 then starts driving SDATA and outputting the 32 bits of the addressed register starting from the most significant bit. After the last bit has been output, the MAX2771 tri-states SDATA, and the host subsequently brings CSN high completing the transaction.

Figure 5 shows a register write transaction. In this example, a 32-bit register is written by the host. The host first asserts CSN, begins driving SDATA with the register address preceded by 8 zeros and starts toggling SCLK. The MAX2771 samples the bits on SDATA on the rising edge of SCLK. After the address is output, the host outputs a R/W bit having value of 0 indicating this a write transaction. The next bits are the TA bits. Since this is a write, the host may choose to continue driving SDATA during this interval. The next 32 SCLKs, the host outputs the 32-bit data to be written to the addressed register starting from the most significant bit. After the last bit has been output, the host tri-states SDATA, and subsequently brings CSN high completing the transaction.

If the host does not assert CSN, the MAX2771 will ignore any activity on SCLK or SDATA. This allows multiple MAX2771 devices to be connected to the SPI and controlled by one host. Only the MAX2771 that has its CSN input asserted will react to the host.

Figure 4. Register Read Functional Timing

Figure 5. Register Write Functional Timing

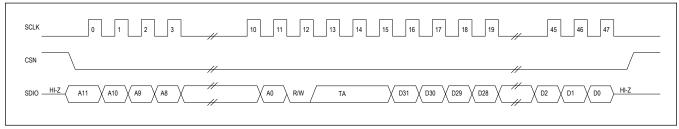

Figure 6 illustrates the timing relationships between the three signals of the three-wire interface. See Table 15.

Figure 6. Three-Wire Interface Timing Diagram

# **Table 15. Serial Interface Timing Requirements**

| SYMBOL           | PARAMETER                                                  | MIN | MAX | UNITS |

|------------------|------------------------------------------------------------|-----|-----|-------|

| t <sub>CSS</sub> | Falling edge of CSN to rising edge of the first SCLK pulse | 10  |     | ns    |

| t <sub>DS</sub>  | Data in to SCLK setup time                                 | 10  |     | ns    |

| t <sub>DH</sub>  | Data in to SCLK hold time                                  | 10  |     | ns    |

| t <sub>CP</sub>  | SCLK period                                                | 250 |     | ns    |

| t <sub>DAZ</sub> | SCLK falling edge to SDATA tri-stated                      |     | 25  | ns    |

| t <sub>DZA</sub> | SCLK falling edge to SDATA active                          |     | 25  | ns    |

| tcsh             | Last SCLK rising edge to rising edge of CSN                | 10  |     | ns    |

| t <sub>DP</sub>  | SCLK falling edge to data out propagation delay            |     | 25  | ns    |

| tCSNOFF          | CSN rising edge to next SPI transaction CSN falling edge   | 100 |     | ns    |

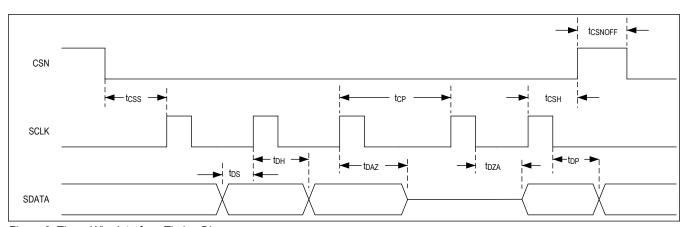

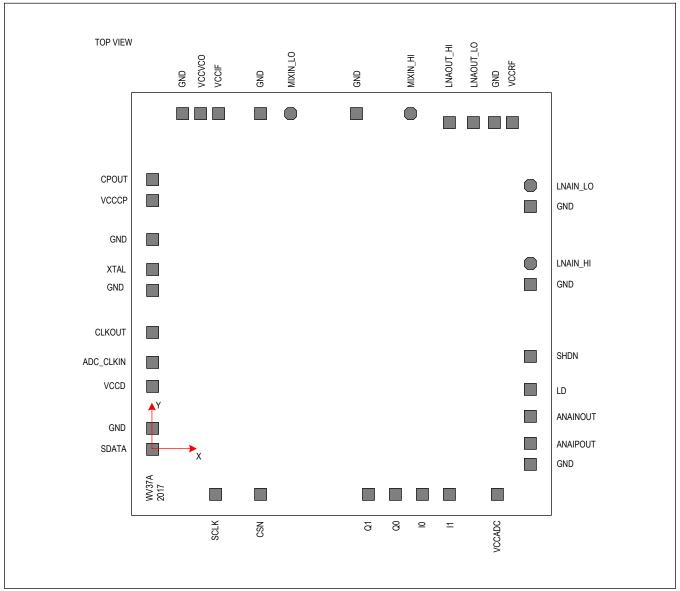

#### **Wafer Die Description**

The MAX2771 is sold in wafer die form in addition to the TQFN packaged part. An approximately to-scale diagram of the die is shown in *Figure 7*. If one views the die through a microscope with the same orientation, it will resemble the figure. The bonding pads are depicted as squares or octagons. At the bottom left corner of the die is the die ID text. This can be used as an aid for orientation. The dimensions of the die are 2585 microns (horizontal) x 2685 microns (vertical). A micron is one micrometer (10<sup>-6</sup>m).

The bonding pad names match the names in the <u>Pin Description</u> table. For the packaged version of the IC, the GND bonding pads are down-bonded to an exposed paddle. The GND pads should be connected to the ground plane of the substrate to which the die is attached.

Figure 7. Die Diagram

In order to provide information on the locations of the bonding pads, a Cartesian coordinate system is established with

the origin at the center of the SDATA bonding pad at the bottom left corner of the die. The coordinate system is depicted in the die diagram. A positive X coordinate is to the right of the origin, and a negative X coordinate is the left of the origin. A positive Y coordinate is above the origin, and a negative Y coordinate is below the origin. Table 16 provides the X and Y coordinates of each pad. The list of pads starts at the top left corner of the die and proceeds counter-clockwise around the die. The coordinates are for the center of each pad. The dimensions are microns. As an example, the coordinates of the CSN are (X, Y) = (656.1, -293.9). Hence the center of the CSN pad is 656.1 microns to the right of, and 293.9 microns below, the center of the SDATA pad.

**Table 16. Die Pad Coordinates**

| PAD       | X      | Υ      |

|-----------|--------|--------|

| CPOUT     | 0.0    | 1743.4 |

| VCCCP     | 0.0    | 1612.7 |

| GND       | 0.0    | 1366.1 |

| XTAL      | 0.0    | 1181.1 |

| GND       | 0.0    | 1048.1 |

| CLKOUT    | 0.0    | 771.9  |

| ADC_CLKIN | 0.0    | 571.7  |

| VCCD      | 0.0    | 403.5  |

| GND       | 0.0    | 136.8  |

| SDATA     | 0.0    | 0.0    |

| SCLK      | 381.7  | -293.9 |

| CSN       | 656.1  | -293.9 |

| Q1        | 1311.5 | -293.9 |

| Q0        | 1483.5 | -293.9 |

| 10        | 1655.5 | -293.9 |

| I1        | 1827.5 | -293.9 |

| VCCADC    | 2121.9 | -293.9 |

| GND       | 2320.8 | -107.9 |

| ANAIPOUT  | 2320.8 | 33.1   |

| ANAINOUT  | 2320.8 | 201.3  |

| LD        | 2320.8 | 375.5  |

| SHDN      | 2320.8 | 584.7  |

| GND       | 2310.3 | 1038.8 |

| LNAIN_HI  | 2307.8 | 1174.9 |

| GND       | 2310.2 | 1534.0 |

| LNAIN_LO  | 2310.2 | 1659.7 |

| VCCRF     | 2210.0 | 2056.6 |

| GND       | 2101.8 | 2056.6 |

| LNAOUT_LO | 1976.6 | 2056.6 |

| LNAOUT_HI | 1835.3 | 2056.6 |

| MIXIN_HI  | 1589.5 | 2126.9 |

| GND       | 1256.4 | 2126.9 |

| MIXIN_LO  | 845.2  | 2126.9 |

| GND       | 643.8  | 2126.9 |

| VCCIF     | 391.5  | 2126.9 |

## **Table 16. Die Pad Coordinates (continued)**

| PAD    | x     | Y      |

|--------|-------|--------|

| VCCVCO | 268.4 | 2126.9 |

| GND    | 149.6 | 2126.9 |