# nanoPower Supervisor and Watchdog Timer

### **General Description**

The MAX16152/MAX16153/MAX16154/MAX16155 ultralow-current supervisory circuits monitor a single system supply voltage and the integrity of code execution by a microprocessor or microcontroller. These supervisors assert the reset output whenever the  $V_{CC}$  supply voltage is greater than the minimum operating voltage, but less than the reset threshold. After the supply voltage rises above the reset threshold, the reset output remains asserted for the reset timeout period, and then deasserts. Reset voltage thresholds are available from 1.50V to 5.0V in approximately 100mV increments.

A watchdog timer circuit monitors microprocessor or microcontroller activity. During normal operation, the microprocessor or microcontroller should repeatedly toggle the watchdog input (WDI) before the supervisor's watchdog timeout period elapses to confirm that the system is executing code properly. If the microprocessor or microcontroller does not provide a valid watchdog input transition before the timeout period expires, the supervisor asserts a watchdog (WDO) output to signal that the system is not executing code as expected. The watchdog output pulse can be used to reset the microprocessor or microcontroller, or it may be used to interrupt the system to warn of execution errors. The MAX16152 and MAX16153 feature a manual reset input (MR) to allow an external pushbutton or logic signal to initiate a reset pulse. The MAX16154 and MAX16155 feature a logic input (WD EN) that allows the system to enable and disable the watchdog function.

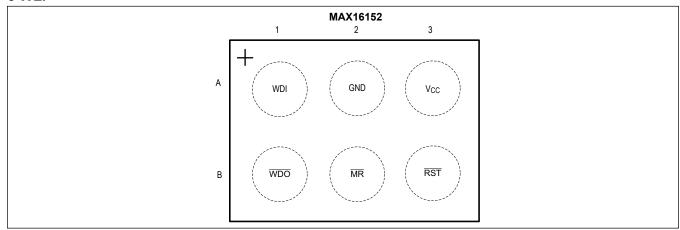

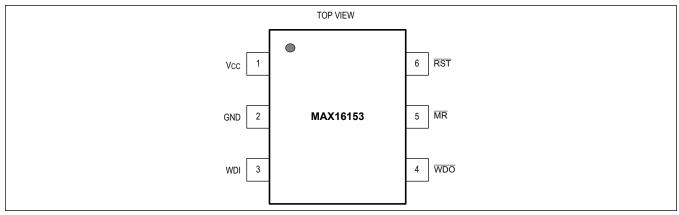

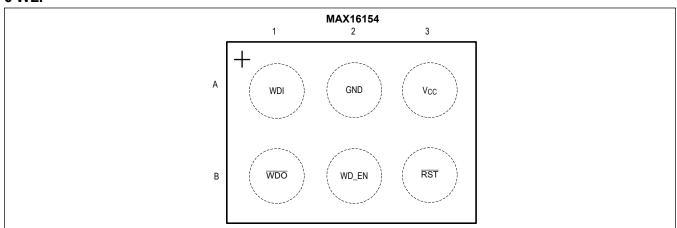

The MAX16152 and MAX16154 are offered in a 0.86mm x 1.27mm 6-bump WLP, while the MAX16153 and MAX16155 are offered in 6-pin SOT23 package. All devices operate over the -40°C to +125°C temperature range.

## **Applications**

- Portable/Battery-Powered Equipment

- Tablets/e-Readers/Mobile Devices

- Glucose Monitors/Patient Monitor

- Metering

#### **Benefits and Features**

- 400nA (typ) Supply Current

- 1.2V to 5.5V Operating Supply Range

- Monitors Supply Voltage and Provides System Reset Signal

- 1.5V to 5.0V Input Threshold Range in 100mV Increments

- Watchdog Function Detects Faulty Code Execution

- Open-Drain Reset and Watchdog Outputs

- Watchdog Timer Enable Input

- 6-Bump WLP Package

- 6-Pin SOT23 Package

- -40°C to +125°C Operating Temperature Range

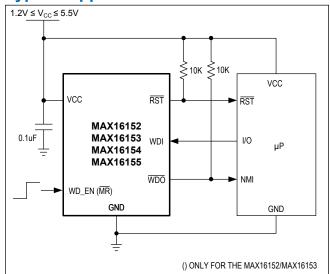

## **Typical Application Circuit**

# nanoPower Supervisor and Watchdog Timer

## **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND                   | 0.3V to +6V                |

|------------------------------------------|----------------------------|

| WDI, WD_EN to GND                        | $-0.3V$ to $V_{CC} + 0.3V$ |

| WDO, RST to GND                          | 0.3V to +6V                |

| Maximum Current, Any Pin (input/output)  | 20mA                       |

| Continuous Power Dissipation (WLP) (TA = |                            |

| mW/°C above +70°C)                       | 840mW                      |

| Continuous Power Dissipation | (SOT23) ( $T_A = +70^{\circ}C$ , derate |

|------------------------------|-----------------------------------------|

| 8.70mW/°C above +70°C)       | 696mW                                   |

| Operating Temperature Range. | 40°C to +125°C                          |

| Junction Temperature         | +150°C                                  |

|                              |                                         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### **6 SOT23**

| Package Code                           | U6+1           |

|----------------------------------------|----------------|

| Outline Number                         | 21-0058        |

| Land Pattern Number                    | <u>90-0175</u> |

| Thermal Resistance, Four-Layer Board   |                |

| Junction to Ambient (θ <sub>JA</sub> ) | 115°C/W        |

| Junction to Case (θ <sub>JC</sub> )    | 80°C/W         |

#### 6 WLP

| Package Code                         | W60C1+2          |

|--------------------------------------|------------------|

| Outline Number                       | <u>21-100258</u> |

| Land Pattern Number                  | _                |

| Thermal Resistance, Four-Layer Board |                  |

| Junction to Case $(\theta_{JC})$     | 95°C/W           |

For the latest package outline information and land patterns (footprints), go to <a href="www.analog.com/en/resources/packaging-quality-symbols-footprints/package-index.html">www.analog.com/en/resources/packaging-quality-symbols-footprints/package-index.html</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.analog.com/en/resources/technical-articles/thermal-characterization-of-ic-packages.html">www.analog.com/en/resources/technical-articles/thermal-characterization-of-ic-packages.html</a>.

### **Electrical Characteristics**

( $V_{CC}$  = 1.2V to 5.5V,  $T_A$  = -40°C to +125°C. Typical values are at  $T_A$  = +25°C and  $V_{CC}$  =  $V_{TH}$  + 150mV.)

| , ,,                                          |                    | 7.                                                                  |      | •   |      |       |

|-----------------------------------------------|--------------------|---------------------------------------------------------------------|------|-----|------|-------|

| PARAMETER                                     | SYMBOL             | CONDITIONS                                                          | MIN  | TYP | MAX  | UNITS |

| Supply Voltage Range                          | V <sub>CC</sub>    |                                                                     | 1.2  |     | 5.5  | V     |

| Supply Current                                | Icc                | Outputs are not asserted, V <sub>CC</sub> = V <sub>TH</sub> + 150mV |      | 400 | 900  | nA    |

| V <sub>CC</sub> Threshold Range               |                    |                                                                     | 1.5  |     | 5    | V     |

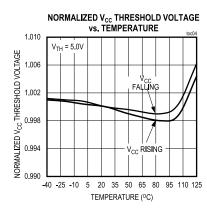

| V <sub>CC</sub> Reset Threshold Accuracy      | V <sub>TH_AC</sub> | V <sub>CC</sub> falling                                             | -2.5 |     | +2.5 | %     |

| V <sub>CC</sub> Reset Threshold<br>Hysteresis |                    | V <sub>CC</sub> rising                                              |      | 0.4 |      | %     |

### **Electrical Characteristics (continued)**

(V<sub>CC</sub> = 1.2V to 5.5V,  $T_A$  = -40°C to +125°C. Typical values are at  $T_A$  = +25°C and  $V_{CC}$  =  $V_{TH}$  + 150mV.)

| PARAMETER                                | SYMBOL             | COND                                                | ITIONS                                      | MIN                      | TYP | MAX                      | UNITS |

|------------------------------------------|--------------------|-----------------------------------------------------|---------------------------------------------|--------------------------|-----|--------------------------|-------|

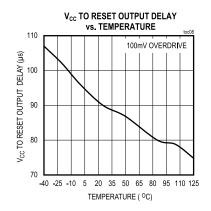

| V <sub>CC</sub> to Reset Delay           | t <sub>RD</sub>    | V <sub>CC</sub> falling from (V <sub>T</sub> 100mV) | <sub>H</sub> + 100mV) to (V <sub>TH</sub> - |                          | 80  |                          | μs    |

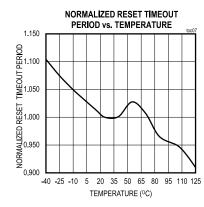

| Reset Timeout Period<br>Accuracy         | t <sub>RP_AC</sub> | Note 1                                              |                                             | -50                      |     | +50                      | %     |

| WATCHDOG                                 |                    |                                                     |                                             |                          |     |                          |       |

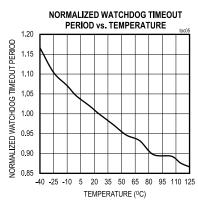

| Watchdog Timeout<br>Period Accuracy      | t <sub>WD_AC</sub> |                                                     |                                             | -50                      |     | +50                      | %     |

| Watchdog Startup Delay<br>Accuracy       | tSTART-UP_AC       |                                                     |                                             | -50                      |     | +50                      | %     |

| Watchdog Setup Time                      | <sup>†</sup> SETUP | Time between low-to WD_EN and watchd                |                                             |                          | 300 |                          | μs    |

|                                          |                    | V <sub>CC</sub> ≥ 1.0V, I <sub>SINK</sub> =         | 50μΑ                                        |                          |     | 0.3                      |       |

| Output Voltage Low                       | V <sub>OL</sub>    | V <sub>CC</sub> > 2.7V, I <sub>SINK</sub> =         |                                             |                          |     | 0.3                      | V     |

|                                          |                    | V <sub>CC</sub> > 4.5V, I <sub>SINK</sub> =         | 3.2mA                                       |                          |     | 0.4                      |       |

| Watchdog Input Pulse<br>Width            | t <sub>WDI</sub>   | After WDO deassert                                  | ed                                          | 1                        |     |                          | μs    |

| Watchdog Output Pulse<br>Width           | t <sub>WDO</sub>   |                                                     |                                             | 100                      |     | 300                      | ms    |

| Input Voltage High                       | V <sub>IH</sub>    |                                                     |                                             | 0.8 x<br>V <sub>CC</sub> |     |                          | V     |

| Input Logic-Low                          | V <sub>IL</sub>    | WDI, MR, WD_EN                                      | V <sub>CC</sub> ≥ 1.5V                      |                          |     | 0.3 x<br>V <sub>CC</sub> | V     |

| Watchdog Output<br>Leakage Current       |                    | $V_{\overline{WDO}} = 0$ to 5.5V, o                 | utput deasserted                            |                          |     | 1                        | μΑ    |

| Reset Ouput Leakage<br>Current           |                    | $V_{\overline{RST}}$ = 0 to 5.5V, re deasserted     | set output                                  |                          |     | 1                        | μΑ    |

| WD_EN Input Glitch<br>Rejection          |                    |                                                     |                                             |                          | 300 |                          | ns    |

| Manual Reset Input<br>Glitch Rejection   |                    |                                                     |                                             |                          | 200 |                          | ns    |

| Manual Reset Input to Reset Output Delay | t <sub>MRD</sub>   |                                                     |                                             |                          | 250 |                          | ns    |

| Manual Reset Internal<br>Pullup Resistor |                    |                                                     |                                             | 70                       | 100 | 145                      | kΩ    |

| Input Leakage Current                    |                    | MR, WDI, WD_EN. I<br>or V <sub>CC</sub>             | nput connected GND                          | -1                       |     | +1                       | μΑ    |

Note 1: The reset timeout period is affected by the  $V_{CC}$  rise time during power-up. For a  $V_{CC}$  rise time of 10µs or faster, the additional  $t_{RP}$  is about 4ms (typ) due to the power-up delay of internal blocks.

Note 2: Limits over the operating temperature range and relevant supply voltage range are guaranteed by production test and/or characterization.

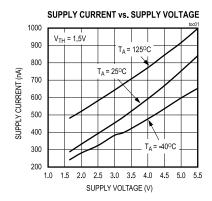

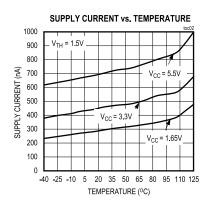

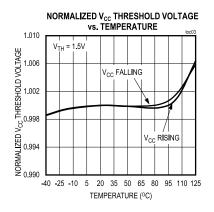

## **Typical Operating Characteristics**

$(V_{CC} = 1.2V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to } +125^{\circ}C)$

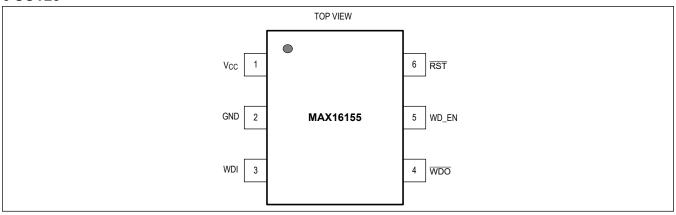

## **Pin Configurations**

## 6 WLP

### **6 SOT23**

### 6 WLP

# nanoPower Supervisor and Watchdog Timer

### **6 SOT23**

## **Pin Description**

|          | Р        | IN       |          | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                           |

|----------|----------|----------|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX16152 | MAX16153 | MAX16154 | MAX16155 | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                           |

| А3       | 1        | A3       | 1        | V <sub>CC</sub> | Supply Voltage. $V_{CC}$ is the power supply input and the monitoring input. Bypass with a $0.1\mu F$ capacitor to GND.                                                                                                                                                                                            |

| A2       | 2        | A2       | 2        | GND             | Ground                                                                                                                                                                                                                                                                                                             |

| A1       | 3        | A1       | 3        | WDI             | Watchdog Input. If WDI remains either high or low for the duration of the watchdog timeout period (t <sub>WD</sub> ), WDO pulses low for the watchdog output pulse width, t <sub>WDO</sub> . The internal watchdog timer clears whenever RST is deasserted or whenever WDI sees a falling edge.                    |

| B1       | 4        | B1       | 4        | WDO             | Watchdog Output. WDO pulses low for the watchdog output pulse width, two, when the internal watchdog times out. WDO is an opendrain output and requires a pullup resistor.                                                                                                                                         |

| B2       | 5        | _        | _        | MR              | Manual Reset Input. Drive $\overline{MR}$ low to manually reset the device. $\overline{RST}$ remains asserted for the reset timeout period after $\overline{MR}$ is released. $\overline{MR}$ is internally pulled up to $V_{CC}$ with a 100k $\Omega$ resistor.                                                   |

| _        | _        | B2       | 5        | WD_EN           | Watchdog Enable Input. Drive WD_EN high to enable the watchdog timer. Drive WD_EN low to disable the watchdog timer.                                                                                                                                                                                               |

| В3       | 6        | В3       | 6        | RST             | Reset Output. $\overline{RST}$ asserts when $V_{CC}$ falls below the factory-set threshold. When $V_{CC}$ goes above $V_{TH} + V_{HYS}$ , $\overline{RST}$ remains asserted for the reset timeout period ( $t_{RP}$ ) and then deasserts. $\overline{RST}$ is an open-drain output and requires a pullup resistor. |

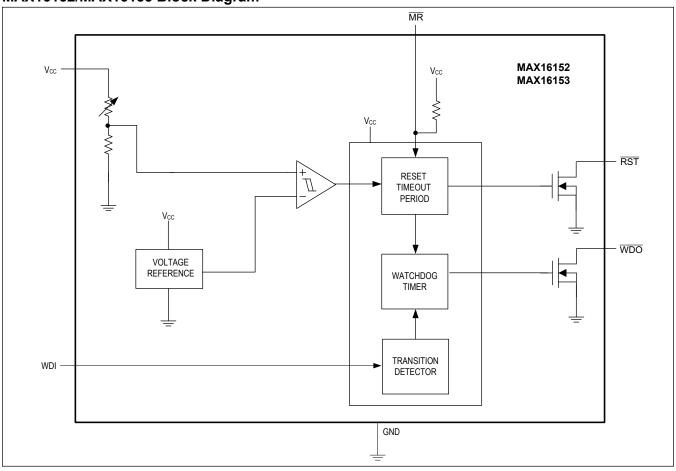

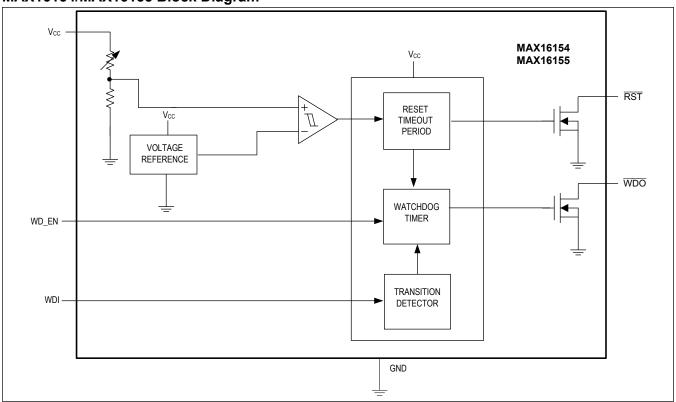

# **Functional Diagrams**

## MAX16152/MAX16153 Block Diagram

### MAX16154/MAX16155 Block Diagram

# nanoPower Supervisor and Watchdog Timer

### **Detailed Description**

The MAX16152/MAX16153/MAX16154/MAX16155 are ultra-low-current supervisory circuits that monitor a single system supply voltage and assert an active-low reset signal when the supply voltage drops below the factory-trimmed reset threshold. After the supply voltage rises above the threshold voltage, the reset output remains asserted during the reset timeout period, and finally asserts after the timeout period ends. In addition, a watchdog timer circuit monitors microprocessor or microcontroller activity. During normal operation, the microprocessor or microcontroller toggles the WDI input periodically with a valid logic transition (low to high or high to low). If the WDI input is toggled within the watchdog timeout period ( $t_{WD}$ ), the internal timer is cleared and restarted, and the WDO output remains high. If the input is not strobed before the timeout period expires, the watchdog output is asserted low for a period equal to the watchdog output pulse width ( $t_{WDO}$ ).

#### **Input Threshold**

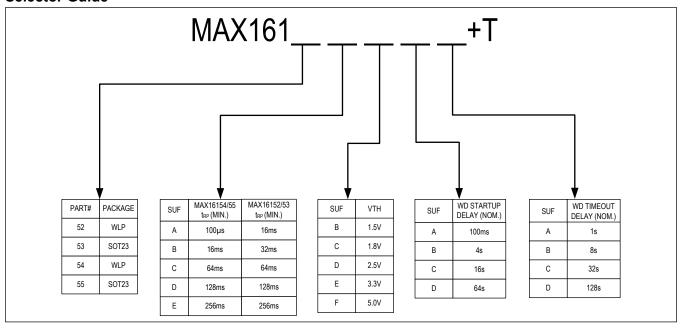

The MAX16152/MAX16153/MAX16154/MAX16155 monitor  $V_{CC}$  with ±2.5% accuracy across the full temperature and supply voltage ranges. The input threshold is programmable from 1.5V to 5V in approximately 100mV increments. Contact Analog Devices for thresholds not listed in the <u>Selector Guide</u>.

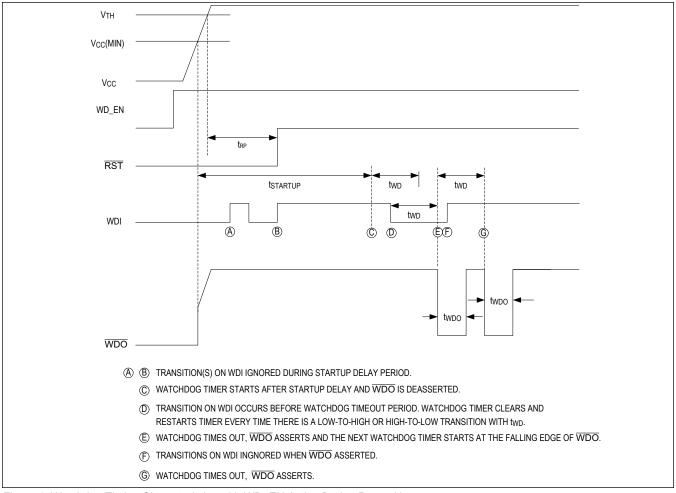

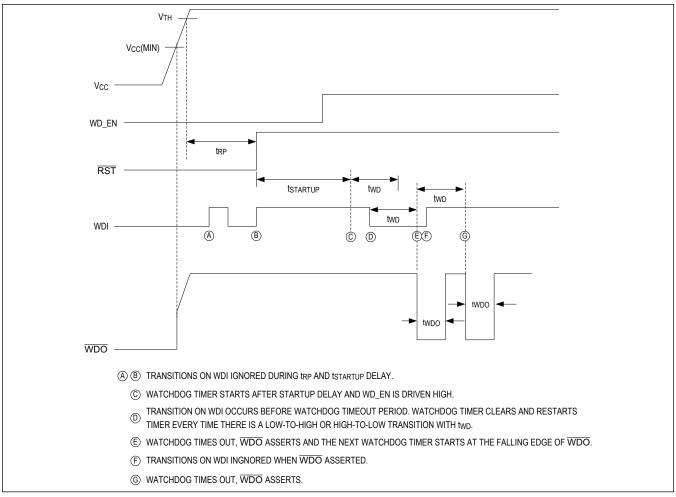

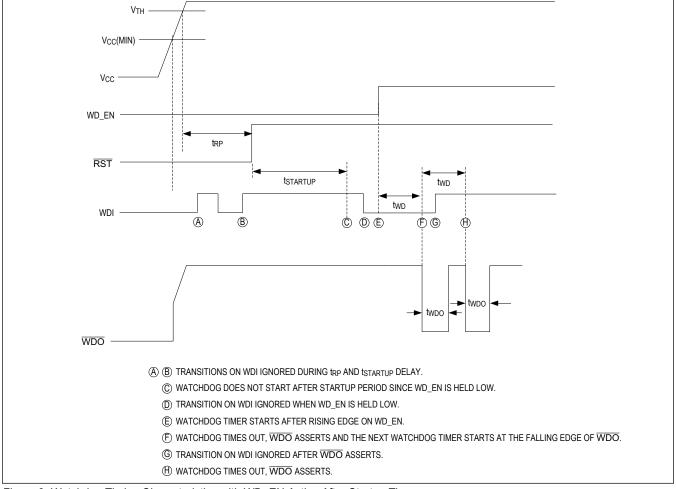

### Watchdog

The MAX16152/MAX16153/MAX16154/MAX16155 offer flexible watchdog circuits for monitoring microprocessor or microcontroller activity. During normal operation, the internal timer is cleared and restarted each time the WDI input undergoes a valid logic transition (high-to-low) within the selected timeout period (t<sub>WD</sub>). The WDO remains high as long as the WDI input is strobed within the selected timeout period. If the WDI input is not strobed before the timeout period expires, the watchdog output is asserted low for the watchdog output pulse width (t<sub>WDO</sub>). The MAX16154 and MAX16155 feature a logic input to enable/disable the watchdog timer during normal operation while the MAX16152 and MAX16153 does not. The watchdog timer for the MAX16152 and MAX16153 can be disabled by leaving the WDI floating.

#### **Watchdog Startup Delay**

All devices feature a factory-set startup delay. The startup delay provides an initial delay for the watchdog timer circuit to power up and initialize before assuming responsibility for normal watchdog input monitoring. For the MAX16152 and MAX16153, monitoring of the WDI input begins after the startup time is complete. For the MAX16154 and MAX16155, monitoring of the WDI input begins after the startup delay if WD\_EN is pulled high. To ensure that the system generates no undesired watchdog outputs, the routine watchdog input transitions should begin before the minimum startup delay period has expired. The startup delay is activated after the reset output is deasserted. See the <u>Selector Guide</u> for available watchdog startup delay options.

#### **Watchdog Timeout Period**

An open-drain, active-low watchdog output (WDO) asserts if a valid watchdog input transition is not received before the timeout period elapses. See the <u>Selector Guide</u> for available watchdog timeout period options.

#### Watchdog Enable Input (WD\_EN)

The MAX16154 and MAX16155 feature an active-high logic input (WD\_EN) to enable or disable the watchdog function. Applying a logic-low to WD\_EN disables the watchdog function, causing the MAX16154 and MAX16155 to ignore any signals applied to WDI. Applying a logic-high to WD\_EN enables the watchdog function after 300µs (max) of setup time tsetup. See Figure 1, Figure 2, and Figure 3 for more details.

Figure 1. Watchdog Timing Characteristics with WD\_EN Active During Power-Up

Figure 2. Watchdog Timing Characteristics with WD\_EN Active During Startup

Figure 3. Watchdog Timing Characteristics with WD\_EN Active After Startup Time

#### Watchdog Input Signal

Watchdog timing is measured from the last WDI falling edge associated with a pulse of at least 1 $\mu$ s (min) in width. WDI transitions are ignored when WDO and/or RST are asserted, and during the startup delay period. Watchdog input transitions are also ignored for a setup period ( $t_{SETLIP}$ ) of up to 300 $\mu$ s after WD EN is asserted.

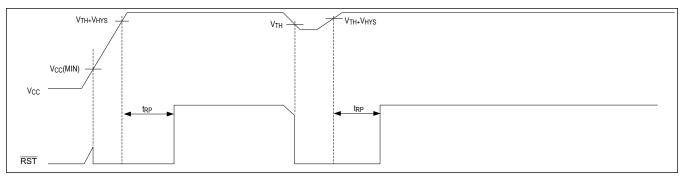

#### **Reset Timeout Period**

The MAX16152/MAX16153/MAX16154/MAX16155 feature an active-low open-drain reset output ( $\overline{RST}$ ) that asserts low when V<sub>CC</sub> drops below the factory-set threshold voltage, V<sub>TH</sub>. The reset output remains asserted as long as V<sub>CC</sub> remains below the threshold voltage. When V<sub>CC</sub> rises above the threshold voltage plus the required hysteresis, the reset output remains asserted during the reset timeout period, and then deasserts. See <u>Figure 4</u> for more details. See the <u>Selector Guide</u> for available reset timeout period options.

# nanoPower Supervisor and Watchdog Timer

Figure 4. Reset Output Timing Diagram

**Note:** The reset timeout period does not include additional power-up delay specified in the <u>Electrical Characteristics</u> table.

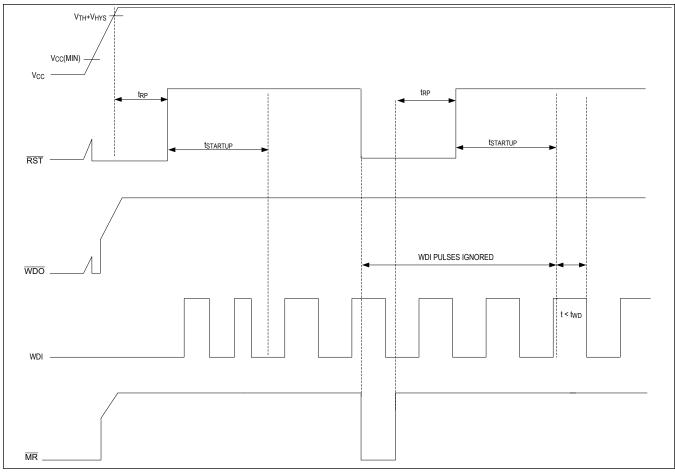

#### **Manual Reset**

The MAX16152 and the MAX16153 include an active-low manual reset input,  $\overline{\text{MR}}$ . Forcing  $\overline{\text{MR}}$  low asserts the reset output after 250ns (typ) delay period (t<sub>MRD</sub>). The reset output remains asserted as long as  $\overline{\text{MR}}$  is held low. The reset output deasserts after the reset timeout period when  $\overline{\text{MR}}$  is released. See Figure 5 below for  $\overline{\text{MR}}$  timing characteristics.  $\overline{\text{MR}}$  has an internal pullup resistor to  $V_{CC}$  and can be left unconnected if not used.

Figure 5. Manual Reset Input Timing Characteristics

### **Applications Information**

#### **Power Supply Bypassing**

The MAX16152/MAX16153/MAX16154/MAX16155 operate from a 1.2V to 5.5V supply. Bypass  $V_{CC}$  to ground with a 0.1 $\mu$ F capacitor as close to the device as possible to improve transient immunity. For fast-rising  $V_{CC}$  transients, additional capacitance may be required.  $V_{CC}$  rise time >50 $\mu$ s ensures proper operation.

#### **Watchdog Software Considerations**

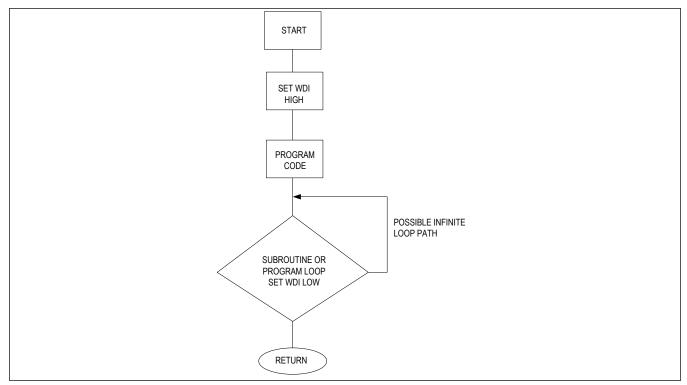

To help the watchdog timer monitor software execution more closely, set and reset the watchdog input at different points in the program, rather than pulsing the watchdog input high-low-high or low-high-low. This technique avoids a stuck loop, in which the watchdog timer would continue to be reset inside the loop, keeping the watchdog from timing out. Figure 6 shows an example of a flow diagram where the I/O driving the watchdog input is set high at the beginning of the program, set low at the end of every subroutine or loop, then set high again when the program returns to the beginning. If the program should hang in any subroutine, the problem would be quickly corrected, since the I/O is continually set low and the watchdog timer is allowed to time out, causing WDO to pulse.

Figure 6. Watchdog Flow Diagram

#### **Negative-Going V<sub>CC</sub> Transients Protection**

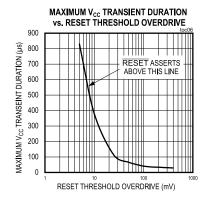

The MAX16152/MAX16153/MAX16154/MAX16155 are relatively immune to short-duration negative-going  $V_{CC}$  transients (glitches). It is usually undesirable to reset the system when  $V_{CC}$  experiences only small glitches. The *Typical Operating Characteristics* show *Maximum Transient Duration vs. Reset Threshold Overdrive*, for which reset pulses are not generated. The graph was produced using negative-going  $V_{CC}$  pulses, starting above  $V_{TH}$  and ending below the reset threshold by the magnitude indicated (reset threshold overdrive). The graph shows the maximum pulse width that a negative-going  $V_{CC}$  transient may typically have without causing a reset pulse to be issued. As the amplitude of the transient increases (i.e., goes farther below the reset threshold), the maximum allowable pulse width decreases. A  $0.1\mu F$

bypass capacitor mounted close to the V<sub>CC</sub> pin provides additional transient immunity.

#### **Selector Guide**

## **Ordering Information**

| PART NUMBER    | TEMPERATURE RANGE | PIN-PACKAGE |

|----------------|-------------------|-------------|

| MAX16152ABAD+T | -40°C to +125°C   | 6 WLP       |

| MAX16154DBAD+T | -40°C to +125°C   | 6 WLP       |

| MAX16154DBAA+T | -40°C to +125°C   | 6 WLP       |

| MAX16155ABAB+T | -40°C to +125°C   | 6 SOT23     |

| MAX16155ABAD+T | -40°C to +125°C   | 6 SOT23     |

| MAX16155BCAA+T | -40°C to +125°C   | 6 SOT23     |

| MAX16155DECC+T | -40°C to +125°C   | 6 SOT23     |

| MAX16155DDCC+T | -40°C to +125°C   | 6 SOT23     |

| MAX16155DDCD+T | -40°C to +125°C   | 6 SOT23     |

| MAX16152+T*    | -40°C to +125°C   | 6 WLP       |

| MAX16153+T*    | -40°C to +125°C   | 6 SOT23     |

| MAX16154+T*    | -40°C to +125°C   | 6 WLP       |

| MAX16155+T*    | -40°C to +125°C   | 6 SOT23     |

**Note:** See the <u>Selector Guide</u> for reset timeout period, threshold voltage, watchdog startup delay, and watchdog timeout options. >For additional options and future products, visit <u>www.analog.com</u>.

<sup>+</sup> Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape-and-reel.

<sup>\*</sup> Potential future product.

# nanoPower Supervisor and Watchdog Timer

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                                                                                                                                                                        | PAGES<br>CHANGED       |

|--------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 0                  | 4/19          | Initial release                                                                                                                                                                                                                                                                    | _                      |

| 1                  | 4/19          | Updated Package Information section                                                                                                                                                                                                                                                | 3                      |

| 2                  | 8/19          | Updated Typical Application Circuit, Electrical Characteristics table, Pin Configuration diagrams, Pin Description table, Figures 1–3, Selector Guide, and Ordering Information table                                                                                              | 2, 4, 5, 7–9,<br>13–15 |

| 3                  | 4/21          | Updated Benefits and Features, Typical Application Circuit, Electrical Characteristics table, Typical Operating Characteristics, Pin Configurations, Pin Description table, Functional Diagrams, Detailed Description, Figures 1–5, Selector Guide, and Ordering Information table | 1–15                   |

| 4                  | 5/21          | Updated Electrical Characteristics table, Package Information, and Ordering Information table                                                                                                                                                                                      | 2, 3, 16               |

| 5                  | 7/21          | Updated Typical Application Circuit                                                                                                                                                                                                                                                | 1                      |

| 6                  | 10/21         | Updated Selector Guide and Ordering Information table                                                                                                                                                                                                                              | 16                     |

| 7                  | 5/22          | Updated Selector Guide                                                                                                                                                                                                                                                             | 16                     |

| 8                  | 3/23          | Updated Ordering Information table                                                                                                                                                                                                                                                 | 16                     |

| 9                  | 8/25          | Updated Ordering Information table                                                                                                                                                                                                                                                 | 16                     |

| 10                 | 11/25         | Updated Ordering Information table                                                                                                                                                                                                                                                 | 16                     |

| 11                 | 12/25         | Updated Ordering Information table                                                                                                                                                                                                                                                 | 16                     |