LTC2066

# 10µA Supply Current, Low I<sub>B</sub>, Zero-Drift Operational Amplifier

## FEATURES

- Low Supply Current: 10µA Maximum (per Amplifier)

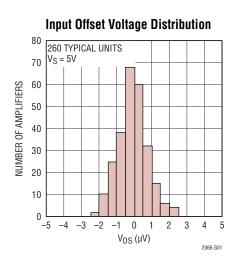

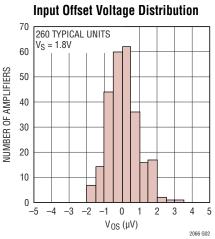

- Offset Voltage: 5µV Maximum

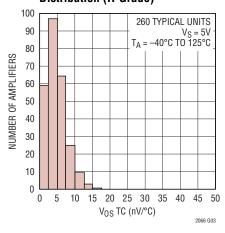

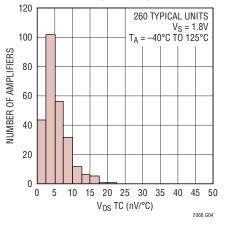

- Offset Voltage Drift: 0.02µV/°C Maximum

- Input Bias Current:

- 5pA Typical

- 50pA Maximum, –40°C to 85°C

- **150pA Maximum, –40°C to 125°C**

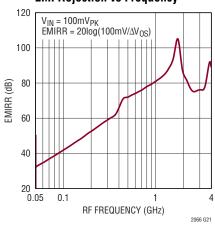

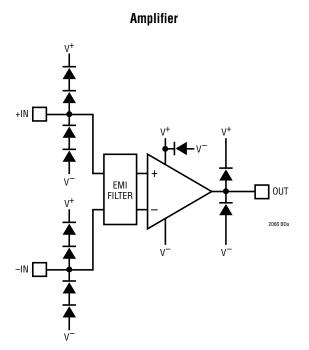

- Integrated EMI Filter (90dB Rejection at 1.8GHz)

- Shutdown Current: 170nA Maximum (per Amplifier)

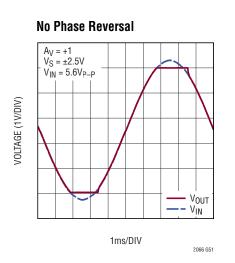

- Rail-to-Rail Input and Output

- 1.7V to 5.25V Operating Supply Range

- A<sub>VOL</sub>: 140dB Typical

- Low-Charge Power-Up for Duty Cycled Applications

- Specified Temperature Ranges:

- –40°C to 85°C

- –40°C to 125°C

- SC70, TSOT23, MS8, DFN10, TSSOP14 and QFN16 Packages

# **APPLICATIONS**

- Signal Conditioning in Wireless Mesh Networks

- Portable Instrumentation Systems

- Low-Power Sensor Conditioning

- Gas Detection

- Temperature Measurement

- Medical Instrumentation

- Energy Harvesting Applications

- Low Power Current Sensing

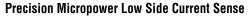

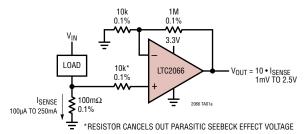

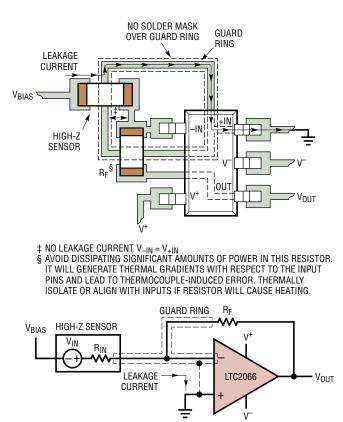

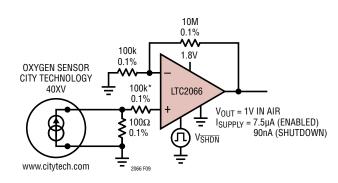

# TYPICAL APPLICATION

# DESCRIPTION

The LTC<sup>®</sup>2066/LTC2067/LTC2068 are single, dual, and quad low power, zero-drift, 100kHz amplifiers. The LTC2066/LTC2067/LTC2068 enable high resolution measurement at extremely low power levels.

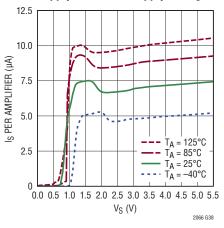

Typical supply current is  $7.5\mu$ A per amplifier with a maximum of  $10\mu$ A. The available shutdown mode has been optimized to minimize power consumption in duty-cycled applications and features low charge loss during power-up, reducing total system power.

The LTC2066/LTC2067/LTC2068's self-calibrating circuitry results in very low input offset ( $5\mu$ V max) and offset drift ( $0.02\mu$ V/°C). The maximum input bias current is only 35pA and does not exceed 150pA over the full specified temperature range. The extremely low input bias current of the LTC2066/LTC2067/LTC2068 allows the use of high value power-saving resistors in the feedback network.

With its ultralow quiescent current and outstanding precision, the LTC2066/LTC2067/LTC2068 can serve as a signal chain building block in portable, energy harvesting and wireless sensor applications.

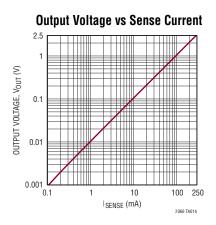

The LTC2066 is available in 6-lead SC70 and 5-lead TSOT-23 packages. The LTC2067 is available in 8-lead MSOP and 10-lead DFN packages. The LTC2068 is available in 14-lead TSSOP and 16-lead  $3mm \times 3mm$  QFN packages. These devices are fully specified over the -40°C to 85°C and -40°C to 125°C temperature ranges.

All registered trademarks and trademarks are the property of their respective owners.

### www.datasheetall.com

# ABSOLUTE MAXIMUM RATINGS (Note 1)

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH   | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|--------------------|-------------------|---------------|---------------------------------|-------------------|

| LTC2066ISC6#TRMPBF | LTC2066ISC6#TRPBF | LHDB          | 6-Lead Plastic SC70             | -40°C to 85°C     |

| LTC2066HSC6#TRMPBF | LTC2066HSC6#TRPBF | LHDB          | 6-Lead Plastic SC70             | -40°C to 125°C    |

| LTC2066IS5#TRMPBF  | LTC2066IS5#TRPBF  | LTHCZ         | 5-Lead Plastic TSOT-23          | –40°C to 85°C     |

| LTC2066HS5#TRMPBF  | LTC2066HS5#TRPBF  | LTHCZ         | 5-Lead Plastic TSOT-23          | -40°C to 125°C    |

| LTC2067IMS8#PBF    | LTC2067IMS8#TRPBF | LTHDC         | 8-Lead Plastic MSOP             | –40°C to 85°C     |

| LTC2067HMS8#PBF    | LTC2067HMS8#TRPBF | LTHDC         | 8-Lead Plastic MSOP             | –40°C to 125°C    |

| LTC2067IDD#PBF     | LTC2067IDD#TRPBF  | LHDD          | 10-Lead (3mm × 3mm) Plastic DFN | –40°C to 85°C     |

| LTC2067HDD#PBF     | LTC2067HDD#TRPBF  | LHDD          | 10-Lead (3mm × 3mm) Plastic DFN | -40°C to 125°C    |

| LTC2068IUD#PBF     | LTC2068IUD#TRPBF  | LHKV          | 16-Lead (3mm × 3mm) Plastic QFN | –40°C to 85°C     |

| LTC2068HUD#PBF     | LTC2068HUD#TRPBF  | LHKV          | 16-Lead (3mm × 3mm) Plastic QFN | -40°C to 125°C    |

| LTC2068IF#PBF      | LTC2068IF#TRPBF   | LTC2068       | 14-Lead TSSOP                   | –40°C to 85°C     |

| LTC2068HF#PBF      | LTC2068HF#TRPBF   | LTC2068       | 14-Lead TSSOP                   | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Parts ending with PBF are RoHS and WEEE compliant.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

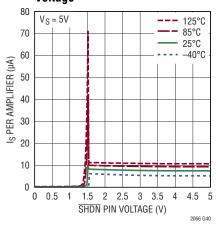

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}$ C. Unless otherwise noted,  $V_S = 1.8V$ ,  $V_{CM} = V_{OUT} = V_S/2$ ,  $V_{\overline{SHDN}} = 1.8V$ ,  $R_L$  to  $V_S/2$ .

| SYMBOL                     | PARAMETER                                                      | CONDITIONS                                                                          |   | MIN                     | TYP        | MAX                     | UNITS          |

|----------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------|---|-------------------------|------------|-------------------------|----------------|

| V <sub>OS</sub>            | Input Offset Voltage (Note 6)                                  | V <sub>S</sub> = 1.7V                                                               | • |                         | 1          | ±5<br>±10               | μV<br>μV       |

| $\Delta V_{OS} / \Delta T$ | Input Offset Voltage Drift (Note 6)                            | –40°C to 85°C<br>–40°C to 125°C                                                     | • |                         |            | ±0.03<br>±0.05          | μV/°C<br>μV/°C |

| I <sub>B</sub>             | Input Bias Current (Note 7)                                    |                                                                                     |   |                         | ±2         |                         | pА             |

| l <sub>os</sub>            | Input Offset Current (Note 7)                                  |                                                                                     |   |                         | ±4         |                         | pА             |

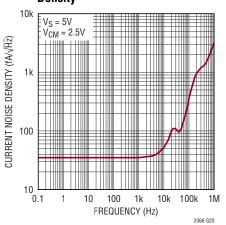

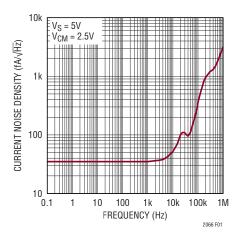

| i <sub>n</sub>             | Input Noise Current Spectral Density                           | f ≤ 100Hz                                                                           |   |                         | 35         |                         | fA/√Hz         |

| en                         | Input Noise Voltage Spectral Density                           | f ≤ 100Hz                                                                           |   |                         | 90         |                         | nV/√Hz         |

| e <sub>n P-P</sub>         | Input Noise Voltage                                            | DC to 10Hz                                                                          |   |                         | 1.9        |                         | $\mu V_{P-P}$  |

| C <sub>IN</sub>            | Input Capacitance                                              | Differential<br>Common Mode                                                         |   |                         | 3.3<br>3.5 |                         | pF<br>pF       |

| V <sub>CMR</sub>           | Input Voltage Range                                            | Guaranteed by CMRR                                                                  |   | (V <sup>-</sup> ) – 0.1 |            | (V <sup>+</sup> ) + 0.1 | V              |

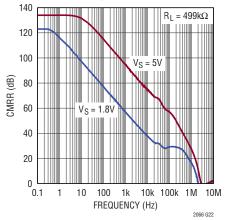

| CMRR                       | Common Mode Rejection Ratio (Note 8)                           | $V_{CM} = (V^{-}) - 0.1V$ to $(V^{+}) + 0.1V$<br>R <sub>L</sub> = 499k              | • | 103<br>100              | 123        |                         | dB<br>dB       |

| PSRR                       | Power Supply Rejection Ratio                                   | V <sub>S</sub> = 1.7V to 5.25V<br>R <sub>L</sub> = 499k                             | • | 108<br>106              | 126        |                         | dB<br>dB       |

| A <sub>VOL</sub>           | Open Loop Gain                                                 | $V_{OUT} = (V^-) + 0.1V$ to $(V^+) - 0.1V$ , $R_L = 499k$                           |   |                         | 135        |                         | dB             |

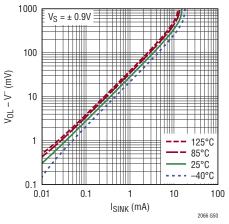

| V <sub>OL</sub>            | Output Voltage Swing Low (V <sub>OUT</sub> – V <sup>-</sup> )  | R <sub>L</sub> = 499k                                                               |   |                         | 0.05       |                         | mV             |

|                            |                                                                | R <sub>L</sub> = 10k                                                                | • |                         | 3          | 10<br>20                | mV<br>mV       |

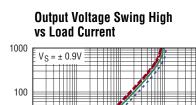

| V <sub>OH</sub>            | Output Voltage Swing High (V <sup>+</sup> – V <sub>OUT</sub> ) | R <sub>L</sub> = 499k                                                               |   |                         | 0.1        |                         | mV             |

|                            |                                                                | R <sub>L</sub> = 10k                                                                | • |                         | 4.5        | 10<br>50                | mV<br>mV       |

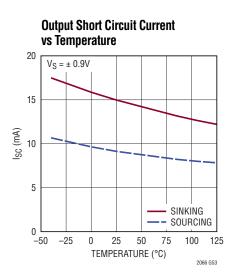

| I <sub>SC</sub>            | Output Short Circuit Current                                   | Sourcing                                                                            | • | 5.8<br>4                | 7.5        |                         | mA<br>mA       |

|                            |                                                                | Sinking                                                                             | • | 10.4<br>5               | 13         |                         | mA<br>mA       |

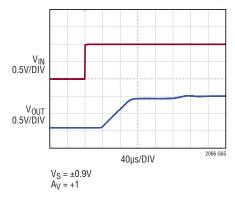

| SR                         | Slew Rate                                                      | A <sub>V</sub> = +1                                                                 |   |                         | 17.5       |                         | V/ms           |

| GBW                        | Gain Bandwidth Product                                         | R <sub>L</sub> = 499k                                                               |   |                         | 100        |                         | kHz            |

| t <sub>ON</sub>            | Power-Up Time                                                  |                                                                                     |   |                         | 0.4        |                         | ms             |

| f <sub>C</sub>             | Internal Chopping Frequency                                    |                                                                                     |   |                         | 25         |                         | kHz            |

| V <sub>S</sub>             | Supply Voltage Range                                           | Guaranteed by PSRR                                                                  | • | 1.7                     |            | 5.25                    | V              |

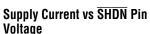

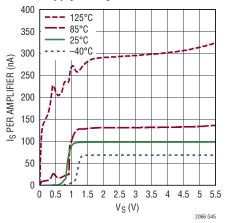

| I <sub>S</sub>             | Supply Current per Amplifier                                   | No Load<br>-40°C to 85°C<br>-40°C to 125°C                                          | • |                         | 7.4        | 10<br>12.5<br>20        | μΑ<br>μΑ<br>μΑ |

|                            |                                                                | In Shutdown ( <del>SHDN</del> = V <sup>-</sup> )<br>-40°C to 85°C<br>-40°C to 125°C | • |                         | 90         | 170<br>250<br>500       | nA<br>nA<br>nA |

| V <sub>H</sub>             | SHDN Pin Threshold, Logic High (Referred to V <sup>-</sup> )   |                                                                                     | • | 1.0                     |            |                         | V              |

| VL                         | SHDN Pin Threshold, Logic Low (Referred to V <sup>-</sup> )    |                                                                                     | • |                         |            | 0.65                    | V              |

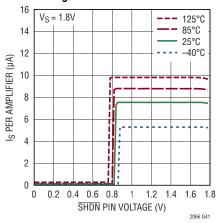

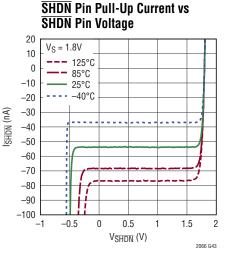

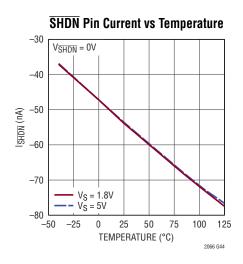

| I <sub>SHDN</sub>          | SHDN Pin Current                                               | V <sub>SHDN</sub> = 0V                                                              |   | -150                    |            | -20                     | nA             |

Rev. B

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25$ °C. Unless otherwise noted,  $V_S = 5V$ ,  $V_{CM} = V_{OUT} = V_S/2$ ,  $V_{SHDN} = 5V$ ,  $R_L$  to  $V_S/2$ .

| SYMBOL                     | PARAMETER                                                                                                                                                                 | CONDITIONS                                                             |   | MIN                     | TYP                  | MAX                     | UNITS                |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|---|-------------------------|----------------------|-------------------------|----------------------|

| V <sub>OS</sub>            | Input Offset Voltage (Note 6)                                                                                                                                             | V <sub>S</sub> = 5.25V                                                 | • |                         | 1                    | ±5<br>±10               | μV<br>μV             |

| $\Delta V_{0S} / \Delta T$ | Input Offset Voltage Drift (Note 6)                                                                                                                                       | -40°C to 85°C<br>-40°C to 125°C                                        | • |                         |                      | ±0.02<br>±0.04          | μV/°C<br>μV/°C       |

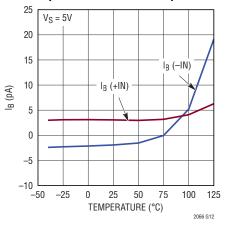

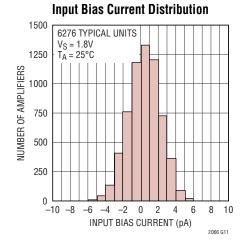

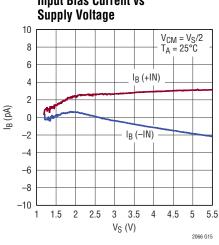

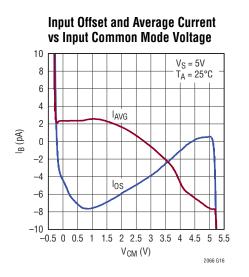

| I <sub>B</sub>             | Input Bias Current                                                                                                                                                        | -40°C to 85°C<br>-40°C to 125°C                                        | • |                         | ±5                   | ±35<br>±50<br>±150      | pA<br>pA<br>pA       |

| I <sub>OS</sub>            | Input Offset Current                                                                                                                                                      | LTC2066, LTC2067<br>-40°C to 85°C<br>-40°C to 125°C                    | • |                         | ±10                  | ±35<br>±50<br>±150      | pA<br>pA<br>pA       |

|                            |                                                                                                                                                                           | LTC2068<br>-40°C to 85°C<br>-40°C to 125°C                             | • |                         | ±10                  | ±65<br>±70<br>±170      | pA<br>pA<br>pA       |

| i <sub>n</sub>             | Input Noise Current Spectral Density                                                                                                                                      | f ≤ 100Hz                                                              |   |                         | 35                   |                         | fA/√Hz               |

| en                         | Input Noise Voltage Spectral Density                                                                                                                                      | f ≤ 100Hz                                                              |   |                         | 80                   |                         | nV/√Hz               |

| e <sub>n P-P</sub>         | Input Noise Voltage                                                                                                                                                       | DC to 10Hz                                                             |   |                         | 1.7                  |                         | μV <sub>P-P</sub>    |

| C <sub>IN</sub>            | Input Capacitance                                                                                                                                                         | Differential<br>Common Mode                                            |   |                         | 3.3<br>3.5           |                         | pF<br>pF             |

| V <sub>CMR</sub>           | Input Voltage Range                                                                                                                                                       | Guaranteed by CMRR                                                     | • | (V <sup>−</sup> ) − 0.1 |                      | (V <sup>+</sup> ) + 0.1 | V                    |

| CMRR                       | Common Mode Rejection Ratio                                                                                                                                               | $V_{CM} = (V^{-}) - 0.1V$ to $(V^{+}) + 0.1V$<br>R <sub>L</sub> = 499k | • | 111<br>108              | 134                  |                         | dB<br>dB             |

| PSRR                       | Power Supply Rejection Ratio                                                                                                                                              | V <sub>S</sub> = 1.7V to 5.25V<br>R <sub>L</sub> = 499k                | • | 108<br>106              | 126                  |                         | dB<br>dB             |

| EMIRR                      | $ \begin{array}{l} \mbox{EMI Rejection Ratio} \\ \mbox{V}_{RF} = 100m \mbox{V}_{PK} \\ \mbox{EMIRR} = 20 \bullet \log(\mbox{V}_{RF}/\mbox{$\Delta V_{OS}$}) \end{array} $ | f = 400MHz<br>f = 900MHz<br>f = 1800MHz<br>f = 2400MHz                 |   |                         | 66<br>79<br>90<br>76 |                         | dB<br>dB<br>dB<br>dB |

| A <sub>VOL</sub>           | Open Loop Gain                                                                                                                                                            | $V_{0UT} = (V^-) + 0.1V$ to $(V^+) - 0.1V$ , $R_L = 499k$              | • | 112<br>110              | 140                  |                         | dB<br>dB             |

| V <sub>OL</sub>            | Output Voltage Swing Low (V <sub>OUT</sub> – V <sup>-</sup> )                                                                                                             | R <sub>L</sub> = 499k                                                  |   |                         | 0.1                  |                         | mV                   |

|                            |                                                                                                                                                                           | R <sub>L</sub> = 10k                                                   | • |                         | 5.5                  | 15<br>20                | mV<br>mV             |

| V <sub>OH</sub>            | Output Voltage Swing High (V <sup>+</sup> – V <sub>OUT</sub> )                                                                                                            | R <sub>L</sub> = 499k                                                  |   |                         | 0.15                 |                         | mV                   |

|                            |                                                                                                                                                                           | R <sub>L</sub> = 10k                                                   | • |                         | 7                    | 15<br>20                | mV<br>mV             |

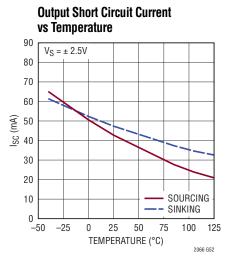

| I <sub>SC</sub>            | Output Short Circuit Current                                                                                                                                              | Sourcing                                                               | • | 30<br>16                | 51                   |                         | mA<br>mA             |

|                            |                                                                                                                                                                           | Sinking                                                                | • | 20<br>5                 | 48                   |                         | mA<br>mA             |

| SR                         | Slew Rate                                                                                                                                                                 | A <sub>V</sub> = +1                                                    |   |                         | 17.5                 |                         | V/ms                 |

| GBW                        | Gain Bandwidth Product                                                                                                                                                    | R <sub>L</sub> = 499k                                                  | 1 |                         | 100                  |                         | kHz                  |

| t <sub>ON</sub>            | Power-Up Time                                                                                                                                                             |                                                                        |   |                         | 0.4                  |                         | ms                   |

| f <sub>C</sub>             | Internal Chopping Frequency                                                                                                                                               |                                                                        | 1 |                         | 25                   |                         | kHz                  |

| V <sub>S</sub>             | Supply Voltage Range                                                                                                                                                      | Guaranteed by PSRR                                                     | • | 1.7                     |                      | 5.25                    | V                    |

| Is                         | Supply Current per Amplifier                                                                                                                                              | No Load<br>-40°C to 85°C<br>-40°C to 125°C                             | • |                         | 7.5                  | 10<br>12.5<br>20        | μΑ<br>μΑ<br>μΑ       |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Unless otherwise noted,  $V_S = 5V$ ,  $V_{CM} = V_{OUT} = V_S/2$ ,  $V_{SHDN} = 5V$ ,  $R_L$  to  $V_S/2$ .

| SYMBOL            | PARAMETER                                                    | CONDITIONS                                                              |   | MIN  | ТҮР | MAX               | UNITS          |

|-------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|---|------|-----|-------------------|----------------|

|                   |                                                              | In Shutdown (SHDN = V <sup>−</sup> )<br>-40°C to 85°C<br>-40°C to 125°C | • |      | 90  | 170<br>250<br>500 | nA<br>nA<br>nA |

| V <sub>H</sub>    | SHDN Pin Threshold, Logic High (Referred to V <sup>-</sup> ) |                                                                         |   | 1.8  |     |                   | V              |

| VL                | SHDN Pin Threshold, Logic Low (Referred to V <sup>-</sup> )  |                                                                         | • |      |     | 0.8               | V              |

| I <sub>SHDN</sub> | SHDN Pin Current                                             | V <sub>SHDN</sub> = 0V                                                  | • | -150 |     | -20               | nA             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: The inputs are protected by two series connected ESD protection diodes to each power supply. The input current should be limited to less than 10mA. The input voltage should not exceed 300mV beyond the power supply.

Note 3: A heat sink may be required to keep the junction temperature below the absolute maximum rating when the output is shorted indefinitely.

Note 4: The LTC2066I/LTC2067I/LTC2068I is guaranteed to meet specified performance from -40°C to 85°C. The LTC2066H/LTC2067H/LTC2068H is guaranteed to meet specified performance from -40°C to 125°C.

Note 5: Thermal resistance varies with the amount of PC board metal connected to the package. The specified values are for short traces connected to the leads.

Note 6: These parameters are guaranteed by design. Thermocouple effects preclude measurements of these voltage levels during automated testing. V<sub>OS</sub> is measured to a limit determined by test equipment capability.

Note 7: Input Bias Current, Input Offset Current and Open Loop Gain are only production tested at 5V. Input Bias Current and Input Offset Current at 1.8V are expected to meet 5V specifications.

Note 8: Minimum specifications for these parameters are limited by noise and the capabilities of the automated test system.

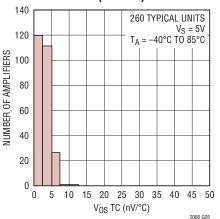

### Input Offset Voltage Drift **Distribution (H-Grade)**

**Input Offset Voltage Drift**

260 TYPICAL UNITS

TΔ

=

35

40 45 50

2066 G06

V<sub>S</sub> = 1.8V -40°C TO 85°C

Distribution (I-Grade)

120

100

80

60

40

20

0

0 5

NUMBER OF AMPLIFIERS

**Input Offset Voltage Drift** Distribution (H-Grade)

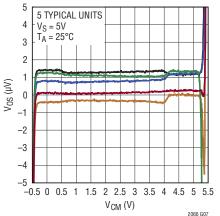

**Input Offset Voltage vs** Input Common Mode Voltage

**Input Offset Voltage Drift** Distribution (I-Grade)

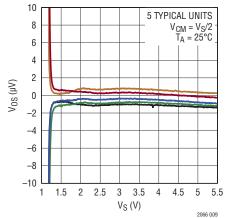

**Input Offset Voltage vs**

**5 TYPICAL UNITS**

$V_{\rm S} = 1.8V$

$T_{A} = 25^{\circ}C$

5

4

3

2

1 V<sub>0S</sub> (µV)

0

-1

-2

-3

-4

-5

-0.5

0

0.5

1

$V_{CM}(V)$

1.5

2

2.5

2066 G08

Input Common Mode Voltage

Input Offset Voltage vs Supply Voltage

10 15 20 25 30

V<sub>OS</sub> TC (nV/°C)

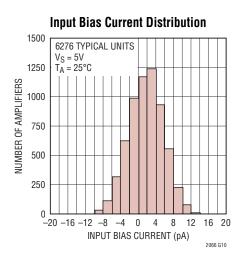

**Input Bias Current vs Temperature**

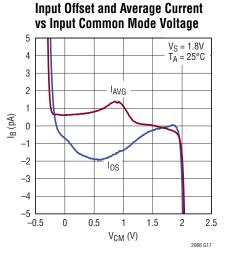

**Input Bias Current vs** Input Common Mode Voltage 10 V<sub>S</sub> = 1.8V  $T_A = 25^{\circ}C$ 8 6 4 I<sub>B</sub> (–IN) 2 I<sub>B</sub> (pA) 0 I<sub>B</sub> (+IN) -2 -4 -6 -8 -10 -0.5 0 0.5 1.5 2 2.5 1 V<sub>CM</sub> (V) 2066 G14

**Input Bias Current vs** Input Common Mode Voltage

**Input Bias Current vs**

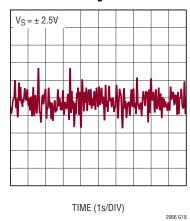

### DC to 10Hz Voltage Noise

INPUT REFERRED VOLTAGE NOISE (0.5µV/DIV)

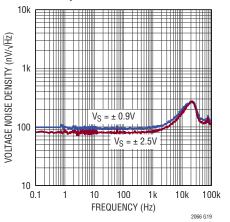

Input Referred Voltage Noise Density

Common Mode Rejection Ratio vs Frequency

Input Referred Current Noise Density

**Power Supply Rejection Ratio**

PSRR

$V_{\rm S} = 5V$

$R_L = 499k\Omega$

vs Frequency

-PSRR

100

120

100

80

60

40

20

0

10

PSRR (dB)

EMI Rejection vs Frequency

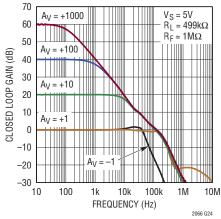

Closed Loop Gain vs Frequency

1k

10k

FREQUENCY (Hz)

100k

1M

2066 G23

2066 G36

2k FREQUENCY (Hz)

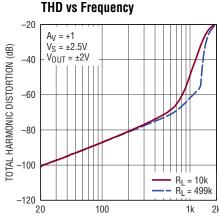

**Maximum Undistorted Output Amplitude vs Frequency** MAXIMUM UNDISTORTED OUTPUT VOLTAGE (VP-P) 6 5 4 3 2  $A_V = +1$  $V_{S}^{v} = \pm 2.5V$ 1 THD < -40dB  $R_{L} = 499k$ 0 100 1k 10k FREQUENCY (Hz)

**Supply Current vs Supply Voltage**

Supply Current vs Temperature 12  $V_{S} = 1.8V$  $V_{S} = 5V$ 11 10 IS PER AMPLIFIER (µA) 9 8 7 6 5 -25 25 50 75 100 -50 0 125 TEMPERATURE (°C) 2066 G39

2066 G37

### Supply Current vs SHDN Pin Voltage

Shutdown Supply Current vs Supply Voltage

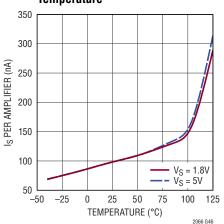

Shutdown Supply Current vs Temperature

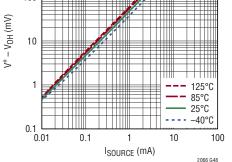

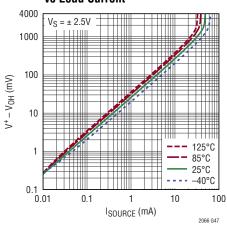

Output Voltage Swing High vs Load Current

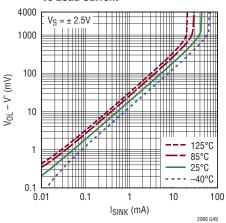

Output Voltage Swing Low vs Load Current

Output Voltage Swing Low vs Load Current

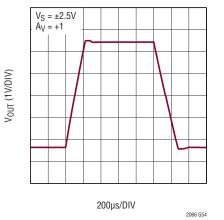

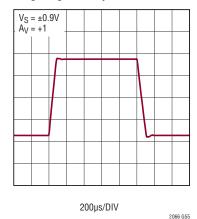

Large Signal Response

Large Signal Response

V<sub>0UT</sub> (0.5V/DIV)

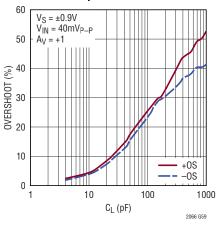

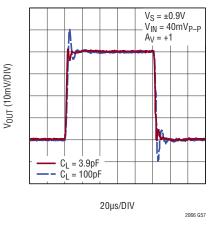

**Small Signal Response**

Vour (10mV/DIV)

2066 G56

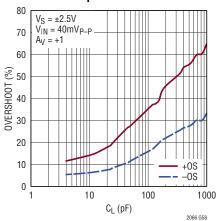

Small Signal Overshoot vs Load Capacitance

Small Signal Response

2066 G62

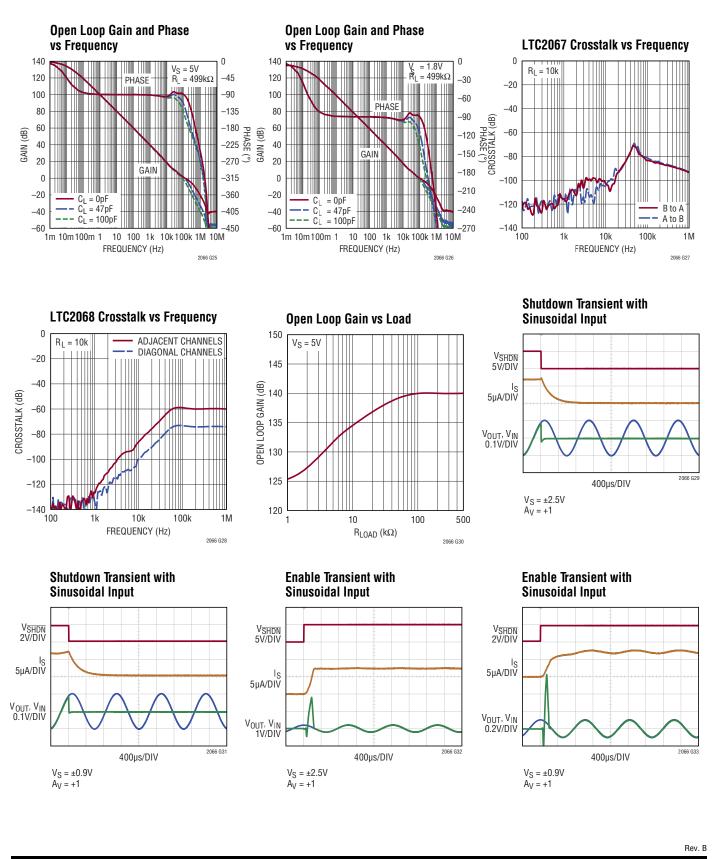

# **TYPICAL PERFORMANCE CHARACTERISTICS**

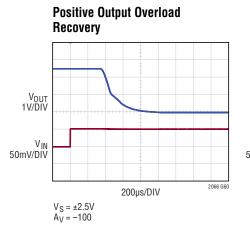

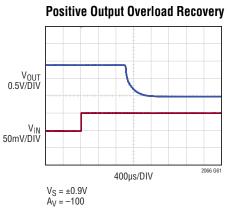

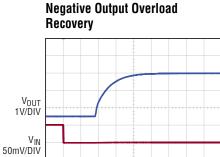

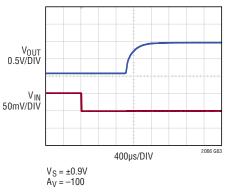

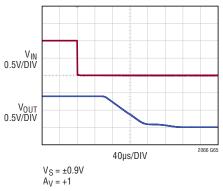

$V_{S} = \pm 2.5 V$ A<sub>V</sub> = -100

Negative Output Overload Recovery

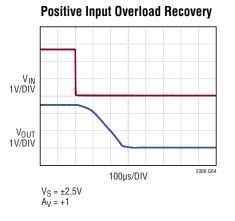

**Positive Input Overload Recovery**

200µs/DIV

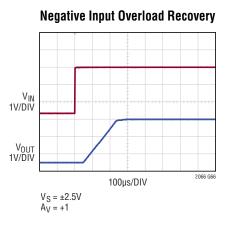

Negative Input Overload Recovery

# PIN FUNCTIONS

**OUT:** Amplifier Output

-IN: Inverting Amplifier Input

+IN: Noninverting Amplifier Input

**V<sup>+</sup>:** Positive Power Supply. A bypass capacitor should be used between supply pins and ground.

**V**<sup>-</sup>: Negative Power Supply. A bypass capacitor should be used between supply pins and ground.

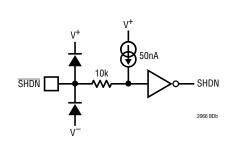

**SHDN**: Shutdown Control Pin. The SHDN pin threshold is referenced to V<sup>-</sup>. If tied to V<sup>+</sup>, the part is enabled. If tied to V<sup>-</sup>, the part is disabled and draws less than 170nA of supply current per amplifier. It is recommended not to float this pin.

# **BLOCK DIAGRAM**

**Shutdown Circuit**

### Using the LTC2066/LTC2067/LTC2068

The LTC2066/LTC2067/LTC2068 are single, dual, and quad zero-drift operational amplifiers with the open-loop voltage gain and bandwidth characteristics of a conventional operational amplifier. Advanced circuit techniques allow the LTC2066/LTC2067/LTC2068 to operate continuously through its entire bandwidth while self-calibrating unwanted errors.

### **Input Voltage Noise**

Zero-drift amplifiers like the LTC2066/LTC2067/LTC2068 achieve low input offset voltage and 1/f noise by heterodyning DC and flicker noise to higher frequencies. In early zero-drift amplifiers, this process resulted in idle tones at the self-calibration frequency, often referred to as the chopping frequency. These artifacts made early zero-drift amplifiers difficult to use. The advanced circuit techniques used by the LTC2066/LTC2067/LTC2068 suppress these spurious artifacts, allowing for trouble-free use.

### **Input Current Noise**

For applications with high source and feedback impedances, input current noise can be a significant contributor to total output noise. For this reason, it is important to consider noise current interaction with circuit elements placed at the amplifier's inputs.

Figure 1. Input Current Noise Spectrum

The current noise spectrum of the LTC2066/LTC2067/ LTC2068 is shown in Figure 1. Low input current noise is achieved through the use of MOSFET input devices and self-calibration techniques to eliminate 1/f current noise. As with all zero-drift amplifiers, there is an increase in current noise at the offset-nulling frequency. This phenomenon is discussed in the Input Bias Current and Clock Feedthrough section.

Input current noise also rises with frequency due to capacitive coupling of MOSFET channel thermal noise.

### **Input Bias Current and Clock Feedthrough**

The input bias current of zero-drift amplifiers has different characteristics than that of a traditional operational amplifier. The specified input bias current is the DC average of transient currents which conduct due to the input stage's switching circuitry. In addition to this, junction leakages can contribute additional input bias current at elevated temperatures. Through careful design and the use of an innovative boot-strap circuit, the input bias current of the LTC2066/LTC2067/LTC2068 does not exceed 35pA at room and 150pA over the full temperature range. This minimizes bias current induced errors even in high impedance circuits.

Transient switching currents at the input interact with source and feedback impedances, producing error voltages which are indistinguishable from a valid input signal. The resulting error voltages are amplified by the amplifier's closed-loop gain, which acts as a filter, attenuating frequency components above the circuit bandwidth. This phenomenon is known as clock feedthrough and is present in all zero-drift amplifiers. Understanding the cause and effect of clock feedthrough is important when using zero-drift amplifiers.

For zero-drift amplifiers, clock feedthrough is proportional to source and feedback impedances, as well as the magnitude of the transient currents. These transient currents have been minimized in the LTC2066/LTC2067/LTC2068 to allow use with high source and feedback impedances. Many circuit designs require high feedback impedances

to minimize power consumption and/or require a sensor which is intrinsically high impedance. In these cases, a capacitor can be used, either at the input or across the feedback resistor, to limit the bandwidth of the closedloop system. Doing so will effectively filter out the clock feedthrough signal.

### Thermocouple Effects

In order to achieve accuracy on the microvolt level, thermocouple effects must be considered. Any connection of dissimilar metals forms a thermoelectric junction and generates a small temperature-dependent voltage. Also known as the Seebeck Effect, these thermal EMFs can be the dominant error source in low-drift circuits.

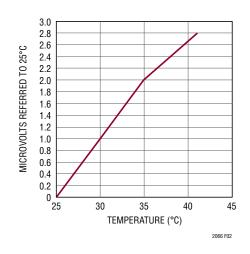

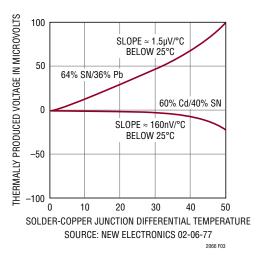

Connectors, switches, relay contacts, sockets, resistors, and solder are all candidates for significant thermal EMF generation. Even junctions of copper wire from different manufacturers can generate thermal EMFs of 200nV/°C, which significantly exceeds the maximum drift specification of the LTC2066/LTC2067/LTC2068. Figures 2 and 3 illustrate the potential magnitude of these voltages and their sensitivity to temperature.

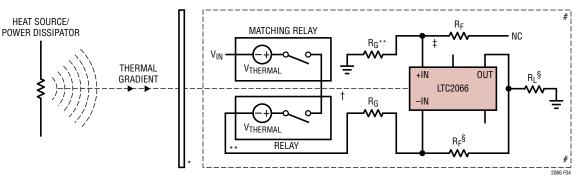

In order to minimize thermocouple-induced errors, attention must be given to circuit board layout and component selection. It is good practice to minimize the number of junctions in the amplifier's input signal path and avoid connectors, sockets, switches, and relays whenever possible. If such components are required, they should be selected for low thermal EMF characteristics. Furthermore, the number, type, and layout of junctions should be matched for both inputs with respect to thermal gradients on the circuit board. Doing so may involve deliberately introducing dummy junctions to offset unavoidable junctions.

Air currents can also lead to thermal gradients and cause significant noise in measurement systems. It is important to prevent airflow across sensitive circuits. Doing so will often reduce thermocouple noise substantially. A summary of techniques can be found in Figure 4.

Figure 2. Thermal EMF Generated by Two Copper Wires from Different Manufacturers

Figure 3. Solder-Copper Thermal EMFs

### Leakage Effects

Leakage currents into high impedance signal nodes can easily degrade measurement accuracy of sub-nanoamp signals. High voltage and high temperature applications are especially susceptible to these issues. Quality insulation materials should be used, and insulating surfaces should be cleaned to remove fluxes and other residues. For humid environments, surface coating may be necessary to provide a moisture barrier.

CUT SLOTS IN PCB FOR THERMAL ISOLATION.

\*\* INTRODUCE DUMMY JUNCTIONS AND COMPONENTS TO OFFSET UNAVOIDABLE JUNCTIONS OR CANCEL THERMAL EMFs.

ALIGN INPUTS SYMMETRICALLY WITH RESPECT TO THERMAL GRADIENTS. t

INTRODUCE DUMMY TRACES AND COMPONENTS FOR SYMMETRICAL THERMAL HEAT SINKING. ŧ

LOADS AND FEEDBACK CAN DISSIPATE POWER AND GENERATE THERMAL GRADIENTS. BE AWARE OF THEIR THERMAL EFFECTS. § #

COVER CIRCUIT TO PREVENT AIR CURRENTS FROM CREATING THERMAL GRADIENTS.

LEAKAGE CURRENT IS ABSORBED BY GROUND INSTEAD OF CAUSING A MEASUREMENT ERROR.

2066 F05

Figure 5. Example Layout of Inverting Amplifier with Leakage Guard Ring

Board leakage can be minimized by encircling the input connections with a guard ring operated at a potential very close to that of the inputs. The ring must be tied to a low impedance node. For inverting configurations, the guard ring should be tied to the potential of the positive input (+IN). For noninverting configurations, the guard ring should be tied to the potential of the negative input (-IN). In order for this technique to be effective, the guard ring must not be covered by solder mask. Ringing both sides of the printed circuit board may be required. See Figure 5 for an example of proper layout.

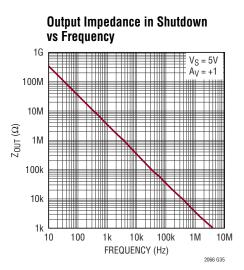

### Shutdown Mode

The LTC2066 in the SC70 package, the LTC2067 in the DFN package, and the LTC2068 in the QFN package feature a shutdown mode for low-power applications. In the OFF state, each amplifier draws less than 170nA of supply current and the outputs present a high impedance to external circuitry.

Shutdown operation is accomplished by tying SHDN below V<sub>L</sub>. If the shutdown feature is not required, it is recommended that SHDN be tied to V<sup>+</sup>. A current source pulls the SHDN pin high to keep the amplifier in the ON state when the pin is floated, however this may not be reliable at elevated temperatures due to board leakage (see SHDN Circuit Block Diagram, page 14). For operation in noisy environments, a capacitor between SHDN and V<sup>+</sup> is recommended to prevent noise from changing the shutdown state. When there is a danger of SHDN being pulled beyond the supply rails, resistance in series with the SHDN pin is recommended to limit the resulting current.

### Start-Up Characteristics

Micropower op amps are often not micropower during start-up, which can cause problems when used on low current supplies. Large transient currents can conduct during power-up until the internal bias nodes settle to their final values. A large amount of current can be drawn from the supplies during this transient, which can sustain for several milliseconds in the case of a micropower part. In the worst case, there may not be enough supply current available to take the system up to nominal voltages. In other cases, this transient power-up current will lead to added power loss in duty-cycled applications.

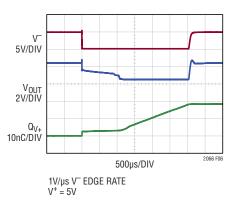

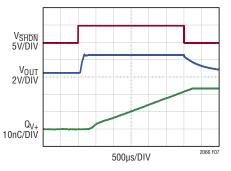

A way to quantify the transient current loss is to integrate the supply current during power-up to examine the total charge loss. If there were no additional transient current, the integrated supply current would appear as a smooth, straight line with a slope equal to the DC supply current of the part. Any deviation from a straight line indicates additional transient current that is drawn from the supply. The LTC2066/LTC2067/LTC2068 have been designed to minimize this charge loss during power-up so that power can be conserved in duty-cycled applications. Figure 6 shows the integrated supply current (i.e. charge) of the LTC2066 during power-up. Likewise, Figure 7 shows the charge loss due to enabling and disabling the part via the SHDN pin.

Figure 6. LTC2066 Charge Loss During Power-Up

Figure 7. LTC2066 Charge Loss Due to Enabling and Disabling via SHDN Pin

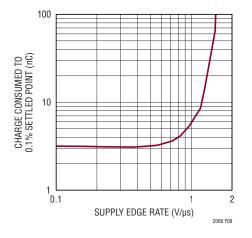

There are benefits when the SHDN pin is used to disable and enable the part in duty-cycled applications, rather than powering down the external supply voltage  $(V^+)$ . Powering up and powering down the external supply will tend to waste charge due to charging and discharging the external decoupling capacitors. For these power-cycled applications, a relay or MOS device can be located after the decoupling capacitors to alleviate this; however there are drawbacks to this approach. The LTC2066 draws an initial charge of approximately 3nC when powered up. This recurring charge loss is unavoidable in power-cycled applications. Additionally, if the supply ramp rate exceeds 0.4V/us, an internal transient ESD clamp will trigger, conducting additional current from V<sup>+</sup> to V<sup>-</sup>. This will waste charge and can make insignificant any savings that may have been expected by power-cycling the supply. Figure 8 shows the charge loss at power-up.

The shutdown pin can be used to overcome these limitations in duty-cycled applications. The typical charge loss transitioning into and out of shutdown is only 2.3nC. Since the supply is not transitioned, the external decoupling capacitors do not draw charge from the supply.

Figure 8. LTC2066 Power-Up Charge vs Supply Edge Rate

### **Gas Sensor**

This low power precision gas sensor circuit operates in an oxygen level range of 0% to 30%, with a nominal output of 1V in normal atmospheric oxygen concentrations (20.9%) when the gas sensor has been fully initialized. Total active power consumption is less than 10.1 $\mu$ A on a single rail supply.

Since this gas sensor produces  $100\mu$ A in a normal oxygen environment and requires a  $100\Omega$  load resistor, the resulting input signal is typically around 10mV. The LTC2066's rail-to-rail input means no additional DC level shifting is necessary, all the way down to very low oxygen concentrations.

Due to the extremely low input offset voltage of the LTC2066, which is  $1\mu$ V typically and  $5\mu$ V maximum, it is possible to gain up the mV-scale input signal substantially without introducing significant error. In the configuration shown in Figure 9, with a noninverting gain of 101V/V, the worst-case input offset results in a maximum of 0.5mV offset on the 1V output, or 0.05% error.

Although the  $100k\Omega$  resistor in series with the gas sensor does not strictly have the same precision requirement as the  $10M\Omega$  and  $100k\Omega$  resistors that set the gain, it is important to use a similar resistor at both input terminals. This helps to minimize additional offset voltage at the inputs due to thermocouple effects and bias current, hence the similar 0.1% precision requirement.

<sup>\*</sup>RESISTOR CANCELS OUT PARASITIC SEEBECK EFFECT VOLTAGE

Figure 9. Micropower Precision Oxygen Sensor

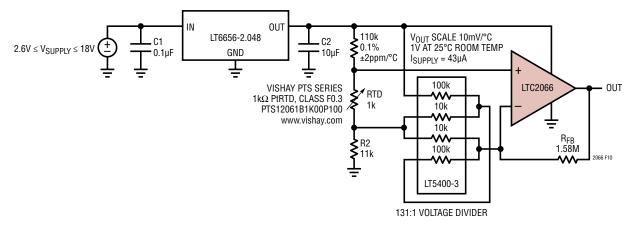

### **RTD Sensor**

This low power platinum resistance temperature detector (RTD) sensor circuit draws only  $43\mu$ A total supply current on a minimum 2.6V rail, and is accurate to within  $\pm$ 1°C at room temperature, including all error intrinsic to the Vishay PTS Class F0.3 Variant RTD. It covers the temperature range from -40°C to 85°C in 10mV/°C increments and produces an output of 1V at nominal room temperature of 25°C.

The LTC2066's extremely low typical offset of  $1\mu$ V and typical input bias current of 5pA allows for the use of a very low excitation current in the RTD. Thus, self-heating is negligible, improving accuracy.

The LT5400-3, B-grade, is used to provide a  $\pm 0.025\%$  matched resistor network that is effectively a precision 131:1 voltage divider. This precision divider forms one half of a bridge circuit, with the 0.1% 110k $\Omega$  and RTD in the other branch. Note that the 110k $\Omega$ 's precision requirement is to ensure matching with the RTD. The 11k $\Omega$  R2 serves to provide a DC offset for the entire bridge so

that the output is 1V at room temperature. Since bridge imbalances can lead to error, it is recommended to minimize the length of the leads connecting the RTD to reduce additional lead resistance.

The LT6656-2.048 reference helps create a known excitation current in the RTD at each temperature of operation, and also acts as a supply for the LTC2066, all while using less than 1 $\mu$ A itself. The LT6656 can accept input voltages anywhere between 2.6V and 18V, allowing for flexibility in selection of supply voltage while maintaining a fixed output range. The LT6656 reference can easily source the 43 $\mu$ A required to run the entire circuit, thanks to the LTC2066's 10 $\mu$ A maximum supply current and ability to handle microvolt signals produced by the RTD under low excitation current.

Care should be taken to minimize thermocouple effects by preventing significant thermal gradients between the two op amp inputs. It is also important to choose feedback and series resistors that are low-tempco to minimize error due to drift over the entire temperature range.

Figure 10. RTD Sensor

### V<sub>IN</sub> 4.5V TO 90V R<sub>IN</sub> 49.9Ω 0.1% C2 10µF R1 C1 REF ISENSE Ş $\mathsf{R}_{\mathsf{SENSE}}$ BSP322P 49.9Ω LTC2066 F LT1389-4.096 3.3µF 0µA to 250mA 0.1Ω M1 0.1% V<sub>OUT</sub> = 10 • I<sub>SENSE</sub> D1 1mV TO 2.5V C3 1N4148 C4**≹** R<sub>OUT</sub> 4.99k I OAD 100nF 22µF ┣ 0.1% BSP322P ┛ M2 ' R3 499k 2066 F11

# **APPLICATIONS INFORMATION**

Figure 11. High Side Current Sense

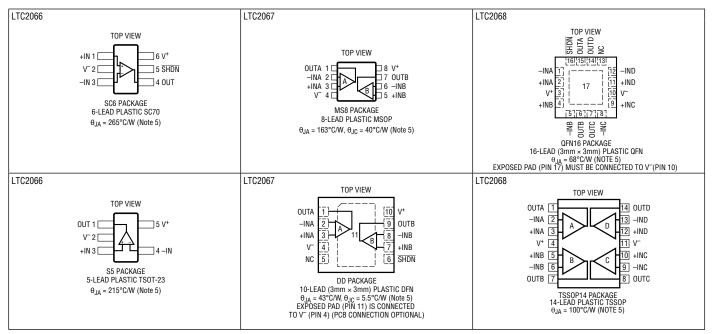

### 90V High Side Current Sense

This micropower precision LTC2066 high side current sense circuit measures currents from  $100\mu A$  to 250mA over a 4.5V to 90V input voltage range.

The output of this circuit is:

$V_{OUT} = \frac{R_{OUT} \bullet R_{SENSE}}{R_{IN}} I_{SENSE} = 10 \bullet I_{SENSE}$

The LTC2066's low typical input offset voltage of  $1\mu$ V and low input bias current of 5pA contribute output errors that are much smaller than the error due to precision limitations of the resistors used. Thus, output accuracy is mainly set by the accuracy of the resistors R<sub>SENSE</sub>, R<sub>IN</sub>, and  $R_{OUT}$ . R1 helps cancel out parasitic Seebeck effect voltages at -IN by balancing with an identical voltage at +IN.

The LT1389-4.096 reference, along with the bootstrap circuit composed of M2, R3, and D1, establishes a very low power isolated 3V rail that protects the LTC2066 from reaching its absolute maximum voltage of 5.5V while allowing for much higher input voltages.

Since the LTC2066's gain-bandwidth product is 100kHz, it is recommended to use this circuit to measure currents that do not change faster than 10kHz. Note that the output filter as drawn will limit the frequency to 1.5Hz, which optimizes for lowest noise. If this output filter bandwidth is too narrow, removing C4 leads to an output filter with 318Hz bandwidth, created by C3 and  $R_{OUT}$ .

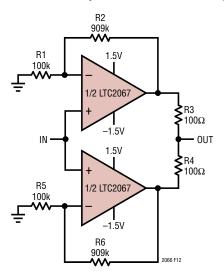

Parallel LTC2067 Amplifiers to Reduce Noise by  $\sqrt{2}$

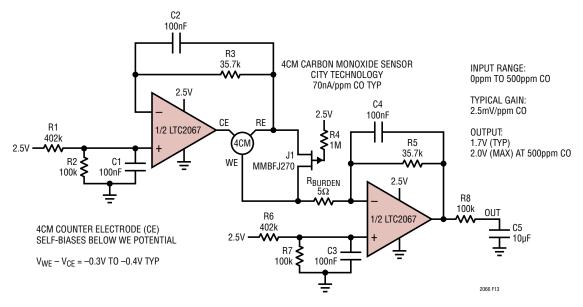

Precision, Micropower Carbon Monoxide Detector

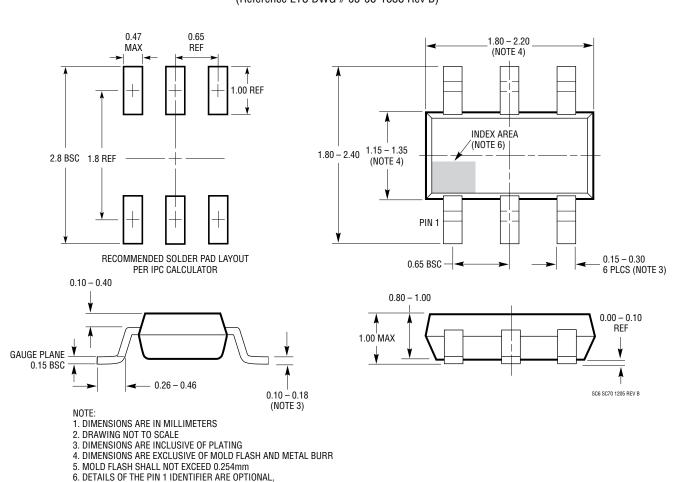

BUT MUST BE LOCATED WITHIN THE INDEX AREA 7. EIAJ PACKAGE REFERENCE IS EIAJ SC-70

8. JEDEC PACKAGE REFERENCE IS MO-203 VARIATION AB

SC6 Package 6-Lead Plastic SC70 (Reference LTC DWG # 05-08-1638 Rev B)

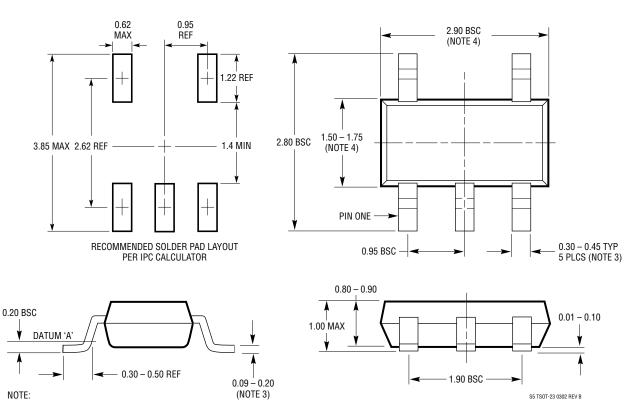

S5 Package 5-Lead Plastic TSOT-23 (Reference LTC DWG # 05-08-1635 Rev B)

NOTE:

1. DIMENSIONS ARE IN MILLIMETERS 2. DRAWING NOT TO SCALE

3. DIMENSIONS ARE INCLUSIVE OF PLATING

4. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

5. MOLD FLASH SHALL NOT EXCEED 0.254mm

6. JEDEC PACKAGE REFERENCE IS MO-193

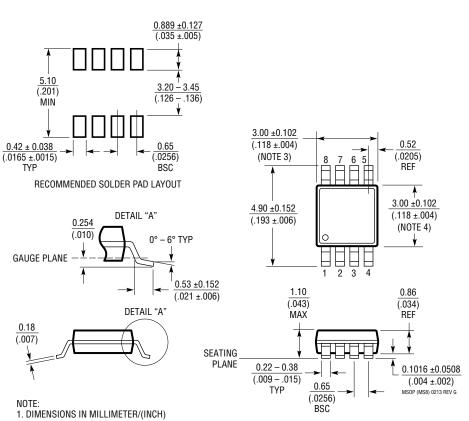

### **MS8** Package 8-Lead Plastic MSOP (Reference LTC DWG # 05-08-1660 Rev G)

2. DRAWING NOT TO SCALE

3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX

Rev B

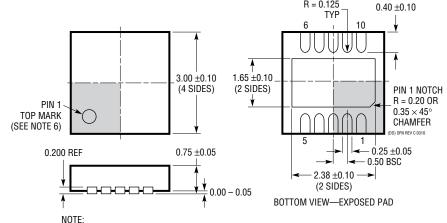

### **DD** Package 10-Lead Plastic DFN (3mm × 3mm) (Reference LTC DWG # 05-08-1699 Rev C)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

R = 0.125

1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-2). CHECK THE LTC WEBSITE DATA SHEET FOR CURRENT STATUS OF VARIATION ASSIGNMENT

DRAWING NOT TO SCALE

ALL DIMENSIONS ARE IN MILLIMETERS

DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH, MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE 5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

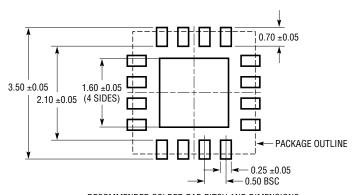

**Exposed Pad Variation BB** BOTTOM VIEW-EXPOSED PAD PIN 1 NOTCH R = 0.20 TYP R = 0.115  $0.75 \pm 0.05$ 3.00 ±0.10 (4 SIDES) OR 0.25 × 45° CHAMFER TYP 15 16 PIN 1 0.40 ±0.10 )TOP MARK l¥ (NOTE 6) 2 1.60 ±0.10 (4-SIDES) VAR BB) GFN 0119 REV Ø - 0.200 REF -0.25 ±0.05 → 🛛 🖛 0.00 - 0.05 - 0.50 BSC NOTE: 1. DRAWING CONFORMS TO JEDEC PACKAGE OUTLINE MO-220 VARIATION (WEED-4) 2. DRAWING NOT TO SCALE

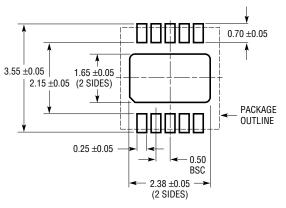

**UD Package** 16-Lead Plastic QFN (3mm × 3mm) (Reference LTC DWG # 05-08-1782 Rev Ø)

DRAWING NOT TO SCALE

ALL DIMENSIONS ARE IN MILLIMETERS

DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

NiPdAu PPF TERMINAL FINISH

SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

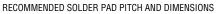

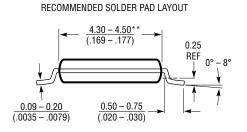

(Reference LTC DWG # 05-08-1650) (Reference LTC DWG # 05-08-1650)  $4.50 \pm 0.10$

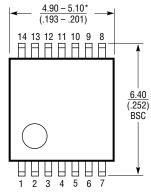

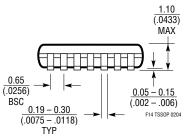

F Package 14-Lead Plastic TSSOP (4.4mm)

0.45 ±0.05 → | ← 0.65 BSC

NOTE:

- 1. CONTROLLING DIMENSION: MILLIMETERS

- 2. DIMENSIONS ARE IN MILLIMETERS (INCHES)

3. DRAWING NOT TO SCALE

- \*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED .152mm (.006") PER SIDE

- \*\*DIMENSIONS DO NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED .254mm (.010") PER SIDE

# **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                  | PAGE NUMBER |

|-----|-------|------------------------------|-------------|

| A   | 07/18 | Adding LTC2067 to data sheet | All Pages   |

| В   | 06/20 | Added LTC2068 to data sheet  | All Pages   |

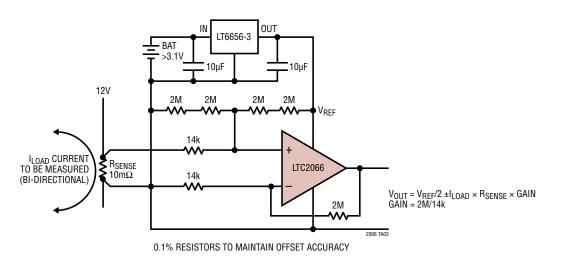

# TYPICAL APPLICATION

Battery Powered Current Sense Amplifier Floats with Sense Resistor Voltage

# **RELATED PARTS**

| PART NUMBER                       | DESCRIPTION                                                | COMMENTS                                                                                                              |

|-----------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| ADA4051-1/ADA4051-2               | Micropower, Single/Dual, Zero-Drift Operational Amplifiers | 7μΑ I <sub>S</sub> , 15μV V <sub>OS</sub> , 11.8V to 5.5V V <sub>S</sub> , 115kHz, RRIO                               |

| LTC2063/LTC2064/<br>LTC2065       | Micropower, Low IB Single/Dual/Quad, Zero-Drift Op Amps    | 2µA I <sub>S</sub> , 5µV V <sub>OS</sub> , 1.7V to 5.25V V <sub>S</sub> , 20kHz, RRIO                                 |

| LTC2054/LTC2055                   | Micropower, Single/Dual, Zero-Drift Operational Amplifier  | 130 $\mu$ A I <sub>S</sub> , 5 $\mu$ V V <sub>OS</sub> , 2.7V to 11 V V <sub>S</sub> , 500kHz, RR Output              |

| ADA4522-1/ADA4522-2/<br>ADA4522-4 | 55V, Low Noise Zero-Drift Operational Amplifier            | 900µA I <sub>S</sub> , 5.8nV/ $\sqrt{\text{Hz}}$ , 5µV V <sub>OS</sub> , 4.5V to 55V V <sub>S</sub> , 3MHz, RR Output |

| LTC2057/LTC2057HV                 | High Voltage-Low Noise Zero-Drift Operational Amplifier    | $4\mu$ V V <sub>OS</sub> , 1.2mA I <sub>S</sub> , 4.75V to 60V V <sub>S</sub> , 1.5MHz, RR Output                     |

| LTC2058                           | 36V, Low Noise Zero-Drift Operational Amplifier            | $5\mu$ V V <sub>0S</sub> , 1.2mA I <sub>S</sub> , 4.75V to 36V V <sub>S</sub> , 2.5MHz, RR Output                     |

| LTC2050/LTC2050HV                 | Zero-Drift Operational Amplifier                           | $3\mu$ V V <sub>0S</sub> , 1.5mA I <sub>S</sub> , 2.7V to 12V V <sub>S</sub> , 3MHz, RR Output                        |

| LTC2051/LTC2052                   | Dual/Quad Zero-Drift Operational Amplifier                 | $3\mu V V_{OS}$ , 1.5mA I <sub>S</sub> , 2.7V to 12V V <sub>S</sub> , 3MHz, RR Output                                 |

| ADA4528-1/ADA4528-2               | 5V Ultra Low Noise Zero-Drift Op Amps                      | 5µV V <sub>0S</sub> , 5.6nV/ $\sqrt{\text{Hz}}$ , 1.7mA I <sub>S</sub> , 2.2V to 5.5V V <sub>S</sub> , 4MHz, RRIO     |

| LT®1494/LT1495/<br>LT1496         | 1.5µA Max, Over-The-Top Precision Operational Amplifier    | 1.5 $\mu A$ I_S, 375 $\mu V$ V_OS, 2.2V to 36V V_S, 2.7kHz, RRIO                                                      |

| LT6003/LT6004/LT6005              | 1.6V, 1µA Precision Rail-to-Rail Input and Output Op Amps  | 1μΑ I <sub>S</sub> , 500μV V <sub>OS</sub> , 1.6V to 16V V <sub>S</sub> , 2kHz, RRIO                                  |

| LT6023                            | Micropower, Enhanced Slew Op Amp                           | 20µА I <sub>S</sub> , 20µV V <sub>OS</sub> , 3V to 30V V <sub>S</sub> , 40kHz                                         |

| LTC2053                           | Precision, Rail-to-Rail, Zero-Drift, PGIA                  | 1.3mA I <sub>S</sub> , 10µV V <sub>OS</sub> , 2.7V to 12V V <sub>S</sub> , 200kHz, RRIO                               |

| LT5400                            | Quad Matched Resistor Network                              | 0.01% Matching, 8ppm/°C Temp Drift , 0.2ppm/°C Temp Matching                                                          |