**Data Sheet**

### FEATURES

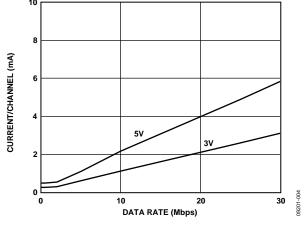

Narrow body, 8-lead SOIC package Low power operation **5 V operation** 1.1 mA per channel maximum at 0 Mbps to 2 Mbps 3.7 mA per channel maximum at 10 Mbps 8.2 mA per channel maximum at 25 Mbps **3 V operation** 0.8 mA per channel maximum at 0 Mbps to 2 Mbps 2.2 mA per channel maximum at 10 Mbps 4.8 mA per channel maximum at 25 Mbps Precise timing characteristics High common-mode transient immunity: >25 kV/µs Safety and regulatory approvals **UL** recognition 2500 V rms for 1 minute per UL 1577 **CSA Component Acceptance Notice #5A VDE Certificate of Conformity** DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12 VIORM = 560 V peak

#### ENHANCED PRODUCT FEATURES

Supports defense and aerospace applications (AQEC) Military temperature range (-55°C to +125°C) Controlled manufacturing baseline Enhanced product change notification Qualification data available on request

#### **APPLICATIONS**

Size-critical multichannel isolation SPI interface/data converter isolation RS-232/RS-422/RS-485 transceiver isolation Digital field bus isolation

# **Dual-Channel Digital Isolator**

## ADuM1200-EP

#### **GENERAL DESCRIPTION**

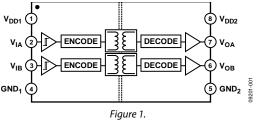

The ADuM1200-EP<sup>1</sup> is a dual-channel, digital isolator based on the Analog Devices, Inc., *i*Coupler<sup>®</sup> technology. Combining high speed CMOS and monolithic transformer technologies, this isolation component provides outstanding performance characteristics superior to alternatives, such as optocouplers.

By avoiding the use of LEDs and photodiodes, *i*Coupler devices remove the design difficulties commonly associated with optocouplers. The typical optocoupler concerns regarding uncertain current transfer ratios, nonlinear transfer functions, and temperature and lifetime effects are eliminated with the simple *i*Coupler digital interfaces and stable performance characteristics. The need for external drivers and other discrete components is eliminated with these *i*Coupler products. Furthermore, *i*Coupler devices consume one-tenth to one-sixth the power of optocouplers at comparable signal data rates.

The ADuM1200-EP isolator provides two independent isolation channels with a supply voltage on either side ranging from 3.0 V to 5.5 V. In addition, the ADuM1200-EP provides low pulse width distortion and tight channel-to-channel matching. Unlike other optocoupler alternatives, the ADuM1200-EP isolator has a patented refresh feature that ensures dc correctness in the absence of input logic transitions and during power-up/ power-down conditions.

Full details about this enhanced product are available in the ADuM1200/ADuM1201 data sheet, which should be consulted in conjunction with this data sheet.

### FUNCTIONAL BLOCK DIAGRAM

<sup>1</sup> Protected by U.S. Patents 5,952,849; 6,873,065; 6,903,578; and 7,075,329. Other patents are pending.

Rev. B Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2010–2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

### www.datasheetall.com

## TABLE OF CONTENTS

| Features                                            | 1 |

|-----------------------------------------------------|---|

| Enhanced Product Features                           | 1 |

| Applications                                        | 1 |

| General Description                                 | 1 |

| Functional Block Diagram                            | 1 |

| Revision History                                    | 2 |

| Specifications                                      | 3 |

| Electrical Characteristics—5 V operation            | 3 |

| Electrical Characteristics—3 V operation            | 5 |

| Electrical Characteristics—Mixed 5 V/3 V or 3 V/5 V |   |

| Operation                                           | 6 |

| Package Characteristics                             | 8 |

### **REVISION HISTORY**

### 2/14—Rev. A to Rev. B

| Changed +105°C to +125°C in Operating Temperature            |     |

|--------------------------------------------------------------|-----|

| Range Through                                                | out |

| Changed Minimum V <sub>DDx</sub> from 2.7 V to 3.0 V Through | out |

| Changes to Table 6                                           | 8   |

| Changes to Table 7                                           | 9   |

| Changes to Table 10                                          |     |

| 5/12 Dec 0.4. Dec 4                                          |     |

#### 5/12-Rev. 0 to Rev. A

| Removed RoHS-Compliant from Features Section1      |

|----------------------------------------------------|

| Changed ADuM1200WSRZ55 to ADuM1200UR-EP, Table 5 8 |

| Changes to Ordering Guide                          |

### 7/10—Revision 0: Initial Version

| Regulatory Information8                                                     |

|-----------------------------------------------------------------------------|

| Insulation and Safety-Related Specifications8                               |

| DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12<br>Insulation Characteristics9 |

| Recommended Operating Conditions9                                           |

| Absolute Maximum Ratings 10                                                 |

| ESD Caution10                                                               |

| Pin Configuration and Function Descriptions11                               |

| Typical Performance Characteristics 12                                      |

| Outline Dimensions                                                          |

| Ordering Guide13                                                            |

## **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS—5 V OPERATION**

All voltages are relative to their respective ground;  $4.5 \text{ V} \le V_{DD1} \le 5.5 \text{ V}$ ,  $4.5 \text{ V} \le V_{DD2} \le 5.5 \text{ V}$ ; all minimum/maximum specifications apply over the entire recommended operating range, unless otherwise noted; all typical specifications are at  $T_A = 25^{\circ}\text{C}$ ,  $V_{DD1} = V_{DD2} = 5 \text{ V}$ .

| Parameter                                             | Symbol                              | Min                                           | Тур                                     | Max                                         | Unit  | Test Conditions                                                              |

|-------------------------------------------------------|-------------------------------------|-----------------------------------------------|-----------------------------------------|---------------------------------------------|-------|------------------------------------------------------------------------------|

| DC SPECIFICATIONS                                     |                                     |                                               | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 1110A                                       | •     |                                                                              |

| Input Supply Current per<br>Channel, Quiescent        | I <sub>DDI (Q)</sub>                |                                               | 0.50                                    | 0.60                                        | mA    |                                                                              |

| Output Supply Current per<br>Channel, Quiescent       | Iddo (Q)                            |                                               | 0.19                                    | 0.30                                        | mA    |                                                                              |

| Total Supply Current, Two<br>Channels <sup>1</sup>    |                                     |                                               |                                         |                                             |       |                                                                              |

| DC to 2 Mbps                                          |                                     |                                               |                                         |                                             |       |                                                                              |

| VDD1 Supply Current                                   | Iddi (Q)                            |                                               | 1.1                                     | 1.4                                         | mA    | DC to 1 MHz logic signal<br>frequency                                        |

| VDD2 Supply Current                                   | I <sub>DD2 (Q)</sub>                |                                               | 0.5                                     | 0.8                                         | mA    | DC to 1 MHz logic signal<br>frequency                                        |

| 10 Mbps                                               |                                     |                                               |                                         |                                             |       |                                                                              |

| VDD1 Supply Current                                   | I <sub>DD1 (Q)</sub>                |                                               | 4.3                                     | 5.5                                         | mA    | 5 MHz logic signal frequency                                                 |

| V <sub>DD2</sub> Supply Current<br>25 Mbps            | I <sub>DD2</sub> (Q)                |                                               | 1.3                                     | 2.0                                         | mA    | 5 MHz logic signal frequency                                                 |

| V <sub>DD1</sub> Supply Current                       | IDD1 (Q)                            |                                               | 10                                      | 13                                          | mA    | 12.5 MHz logic signal frequency                                              |

| V <sub>DD2</sub> Supply Current                       | IDD2 (Q)                            |                                               | 2.8                                     | 3.4                                         | mA    | 12.5 MHz logic signal frequency                                              |

| Input Currents                                        | I <sub>IA</sub> , I <sub>IB</sub>   | -10                                           | +0.01                                   | +10                                         | μΑ    |                                                                              |

| Logic High Input Threshold                            | VIH                                 | 0.7 (V <sub>DD1</sub> or V <sub>DD2</sub> )   |                                         |                                             | v     |                                                                              |

| Logic Low Input Threshold                             | VIL                                 |                                               |                                         | 0.3 (V <sub>DD1</sub> or V <sub>DD2</sub> ) | v     |                                                                              |

| Logic High Output<br>Voltages                         | Vоан, Vовн                          | (V <sub>DD1</sub> or V <sub>DD2</sub> ) – 0.1 | 5.0                                     |                                             | v     | $I_{0x} = -20 \ \mu A$ , $V_{1x} = V_{1xH}$                                  |

| -                                                     |                                     | (V <sub>DD1</sub> or V <sub>DD2</sub> ) – 0.5 | 4.8                                     |                                             | v     | $I_{0x} = -4 \text{ mA}, V_{1x} = V_{1xH}$                                   |

| Logic Low Output Voltages                             | VOAL, VOBL                          |                                               | 0.0                                     | 0.1                                         | V     | $I_{Ox} = 20 \ \mu A$ , $V_{Ix} = V_{IxL}$                                   |

|                                                       |                                     |                                               | 0.04                                    | 0.1                                         | V     | $I_{Ox} = 400 \ \mu A, V_{Ix} = V_{IxL}$                                     |

|                                                       |                                     |                                               | 0.2                                     | 0.4                                         | V     | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxL}$                                    |

| SWITCHING SPECIFICATIONS                              |                                     |                                               |                                         |                                             |       |                                                                              |

| Minimum Pulse Width <sup>2</sup>                      | PW                                  |                                               | 20                                      | 40                                          | ns    |                                                                              |

| Maximum Data Rate <sup>3</sup>                        |                                     | 25                                            | 50                                      |                                             | Mbps  |                                                                              |

| Propagation Delay <sup>4</sup>                        | t <sub>PHL</sub> , t <sub>PLH</sub> | 20                                            |                                         | 45                                          | ns    |                                                                              |

| Pulse Width Distortion,<br> tplh – tphl  <sup>4</sup> | PWD                                 |                                               |                                         | 3                                           | ns    |                                                                              |

| Propagation Delay Skew⁵                               | t <sub>PSK</sub>                    |                                               |                                         | 15                                          | ns    |                                                                              |

| Channel-to-Channel<br>Matching <sup>6</sup>           | tpskcd/tpskod                       |                                               |                                         | 3                                           | ns    |                                                                              |

| Output Rise/Fall Time<br>(10% to 90%)                 | t <sub>R</sub> ∕t <sub>F</sub>      |                                               | 2.5                                     |                                             | ns    |                                                                              |

| Common-Mode Transient<br>Immunity                     |                                     |                                               |                                         |                                             |       |                                                                              |

| Logic High Output <sup>7</sup>                        | CM <sub>H</sub>                     | 25                                            | 35                                      |                                             | kV/μs | $V_{lx} = V_{DD1}, V_{DD2}, V_{CM} = 1000 V,$<br>transient magnitude = 800 V |

| Logic Low Output <sup>7</sup>                         | CML                                 | 25                                            | 35                                      |                                             | kV/μs | $V_{lx} = 0 V, V_{CM} = 1000 V,$<br>transient magnitude = 800 V              |

| Refresh Rate                                          | fr                                  |                                               | 1.2                                     |                                             | Mbps  |                                                                              |

## ADuM1200-EP

| Parameter                                          | Symbol               | Min | Тур  | Max | Unit        | <b>Test Conditions</b> |

|----------------------------------------------------|----------------------|-----|------|-----|-------------|------------------------|

| Dynamic Supply Current per<br>Channel <sup>8</sup> |                      |     |      |     |             |                        |

| Input                                              | I <sub>DDI (D)</sub> |     | 0.19 |     | mA/<br>Mbps |                        |

| Output                                             | I <sub>DDO (D)</sub> |     | 0.05 |     | mA/<br>Mbps |                        |

<sup>1</sup> The supply current values are for both channels combined when running at identical data rates. Output supply current values are specified with no output load present. <sup>2</sup> The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed.

<sup>3</sup> The maximum data rate is the fastest data rate at which the specified pulse width distortion is guaranteed.

<sup>4</sup> t<sub>PHL</sub> propagation delay is measured from the 50% level of the falling edge of the V<sub>Ix</sub> signal to the 50% level of the falling edge of the V<sub>ox</sub> signal. t<sub>PLH</sub> propagation delay is measured from the 50% level of the rising edge of the V<sub>Ix</sub> signal to the 50% level of the rising edge of the V<sub>ox</sub> signal.

<sup>5</sup> t<sub>PSK</sub> is the magnitude of the worst-case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

<sup>6</sup> Codirectional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier. Opposing directional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on opposing sides of the isolation barrier.

<sup>7</sup> CM<sub>H</sub> is the maximum common-mode voltage slew rate that can be sustained while maintaining  $V_{0x} > 0.8 V_{DD2}$ . CM<sub>L</sub> is the maximum common-mode voltage slew rate that can be sustained while maintaining  $V_{0x} < 0.8 V$ . The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges. The transient magnitude is the range over which the common mode is slewed.

<sup>8</sup> Dynamic supply current is the incremental amount of supply current required for a 1 Mbps increase in the signal data rate.

### **ELECTRICAL CHARACTERISTICS—3 V OPERATION**

All voltages are relative to their respective ground;  $3.0 \text{ V} \le \text{V}_{\text{DD1}} \le 3.6 \text{ V}$ ,  $3.0 \text{ V} \le \text{V}_{\text{DD2}} \le 3.6 \text{ V}$ ; all minimum/maximum specifications apply over the entire recommended operating range, unless otherwise noted; all typical specifications are at  $T_A = 25^{\circ}\text{C}$ ,  $V_{\text{DD1}} = V_{\text{DD2}} = 3 \text{ V}$ .

| Parameter                                                       | Symbol                                 | Min                                           | Тур   | Max                                         | Unit        | Test Conditions                                                              |

|-----------------------------------------------------------------|----------------------------------------|-----------------------------------------------|-------|---------------------------------------------|-------------|------------------------------------------------------------------------------|

| DC SPECIFICATIONS                                               |                                        |                                               |       |                                             |             |                                                                              |

| Input Supply Current per Channel,<br>Quiescent                  | I <sub>DDI (Q)</sub>                   |                                               | 0.26  | 0.35                                        | mA          |                                                                              |

| Output Supply Current per Channel,<br>Quiescent                 | I <sub>DDO (Q)</sub>                   |                                               | 0.11  | 0.20                                        | mA          |                                                                              |

| Total Supply Current, Two Channels <sup>1</sup><br>DC to 2 Mbps |                                        |                                               |       |                                             |             |                                                                              |

| V <sub>DD1</sub> Supply Current                                 | IDD1 (0)                               |                                               | 0.6   | 1.0                                         | mA          | DC to 1 MHz logic signal frequency                                           |

| V <sub>DD2</sub> Supply Current                                 | IDD2 (Q)                               |                                               | 0.2   | 0.6                                         | mA          | DC to 1 MHz logic signal frequency                                           |

| 10 Mbps                                                         |                                        |                                               |       |                                             |             | 5 5 1 7                                                                      |

| V <sub>DD1</sub> Supply Current                                 | IDD1 (Q)                               |                                               | 2.2   | 3.4                                         | mA          | 5 MHz logic signal frequency                                                 |

| V <sub>DD2</sub> Supply Current                                 | IDD2 (Q)                               |                                               | 0.7   | 1.1                                         | mA          | 5 MHz logic signal frequency                                                 |

| 25 Mbps                                                         | (3)                                    |                                               |       |                                             |             |                                                                              |

| V <sub>DD1</sub> Supply Current                                 | IDD1 (Q)                               |                                               | 5.2   | 7.7                                         | mA          | 12.5 MHz logic signal frequency                                              |

| V <sub>DD2</sub> Supply Current                                 | IDD2 (Q)                               |                                               | 1.5   | 2.0                                         | mA          | 12.5 MHz logic signal frequency                                              |

| Input Currents                                                  | IIA, IIB                               | -10                                           | +0.01 | +10                                         | μA          | 5 5 1 7                                                                      |

| Logic High Input Threshold                                      | VIH                                    | 0.7 (V <sub>DD1</sub> or V <sub>DD2</sub> )   |       |                                             | v           |                                                                              |

| Logic Low Input Threshold                                       | VIL                                    |                                               |       | 0.3 (V <sub>DD1</sub> or V <sub>DD2</sub> ) | v           |                                                                              |

| Logic High Output Voltages                                      | VOAH, VOBH                             | (V <sub>DD1</sub> or V <sub>DD2</sub> ) – 0.1 | 3.0   |                                             | v           | $I_{Ox} = -20 \ \mu A$ , $V_{Ix} = V_{IxH}$                                  |

|                                                                 | -                                      | (V <sub>DD1</sub> or V <sub>DD2</sub> ) – 0.5 | 2.8   |                                             | V           | $I_{Ox} = -4 \text{ mA}, V_{Ix} = V_{IxH}$                                   |

| Logic Low Output Voltages                                       | VOAL, VOBL                             |                                               | 0.0   | 0.1                                         | V           | $I_{Ox} = 20 \ \mu A, V_{Ix} = V_{IxL}$                                      |

|                                                                 |                                        |                                               | 0.04  | 0.1                                         | V           | $I_{Ox} = 400 \ \mu A, V_{Ix} = V_{IxL}$                                     |

|                                                                 |                                        |                                               | 0.2   | 0.4                                         | v           | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxL}$                                    |

| SWITCHING SPECIFICATIONS                                        |                                        |                                               |       |                                             |             |                                                                              |

| Minimum Pulse Width <sup>2</sup>                                | PW                                     |                                               | 20    | 40                                          | ns          |                                                                              |

| Maximum Data Rate <sup>3</sup>                                  |                                        | 25                                            | 50    |                                             | Mbps        |                                                                              |

| Propagation Delay <sup>4</sup>                                  | tphl, tplh                             | 20                                            |       | 55                                          | ns          |                                                                              |

| Pulse Width Distortion, $ t_{PLH} - t_{PHL} ^4$                 | PWD                                    |                                               |       | 3                                           | ns          |                                                                              |

| Propagation Delay Skew <sup>5</sup>                             | t <sub>PSK</sub>                       |                                               |       | 16                                          | ns          |                                                                              |

| Channel-to-Channel Matching <sup>6</sup>                        | t <sub>PSKCD</sub> /t <sub>PSKOD</sub> |                                               |       | 3                                           | ns          |                                                                              |

| Output Rise/Fall Time (10% to 90%)                              | t <sub>R</sub> /t <sub>F</sub>         |                                               | 2.5   |                                             | ns          |                                                                              |

| Common-Mode Transient Immunity                                  |                                        |                                               |       |                                             |             |                                                                              |

| Logic High Output <sup>7</sup>                                  | CM <sub>H</sub>                        | 25                                            | 35    |                                             | kV/μs       | $V_{lx} = V_{DD1}, V_{DD2}, V_{CM} = 1000 V,$<br>transient magnitude = 800 V |

| Logic Low Output <sup>7</sup>                                   | CML                                    | 25                                            | 35    |                                             | kV/μs       | $V_{Ix} = 0 V$ , $V_{CM} = 1000 V$ ,<br>transient magnitude = 800 V          |

| Refresh Rate                                                    | fr                                     |                                               | 1.1   |                                             | Mbps        | -                                                                            |

| Dynamic Supply Current per Channel <sup>8</sup>                 |                                        |                                               |       |                                             |             |                                                                              |

| Input                                                           | I <sub>DDI (D)</sub>                   |                                               | 0.10  |                                             | mA/<br>Mbps |                                                                              |

| Output                                                          | I <sub>DDO (D)</sub>                   |                                               | 0.03  |                                             | mA/<br>Mbps |                                                                              |

<sup>1</sup> The supply current values are for both channels combined when running at identical data rates. Output supply current values are specified with no output load present.

<sup>2</sup> The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed.

<sup>3</sup> The maximum data rate is the fastest data rate at which the specified pulse width distortion is guaranteed.

<sup>4</sup> t<sub>PHL</sub> propagation delay is measured from the 50% level of the falling edge of the V<sub>Ix</sub> signal to the 50% level of the falling edge of the V<sub>ox</sub> signal. t<sub>PLH</sub> propagation delay is measured from the 50% level of the rising edge of the V<sub>ix</sub> signal to the 50% level of the rising edge of the V<sub>ox</sub> signal.

<sup>5</sup> t<sub>PSK</sub> is the magnitude of the worst-case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

<sup>6</sup> Codirectional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier. Opposing directional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on opposing sides of the isolation barrier.

$^{7}$  CM<sub>H</sub> is the maximum common-mode voltage slew rate that can be sustained while maintaining V<sub>0x</sub> > 0.8 V<sub>DD2</sub>. CM<sub>L</sub> is the maximum common-mode voltage slew rate that can be sustained while maintaining V<sub>0x</sub> > 0.8 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges. The transient magnitude is the range over which the common mode is slewed.

<sup>8</sup> Dynamic supply current is the incremental amount of supply current required for a 1 Mbps increase in the signal data rate.

### ELECTRICAL CHARACTERISTICS—MIXED 5 V/3 V OR 3 V/5 V OPERATION

All voltages are relative to their respective ground; 5 V/3 V operation:  $4.5 \text{ V} \le V_{DD1} \le 5.5 \text{ V}$ ,  $3.0 \text{ V} \le V_{DD2} \le 3.6 \text{ V}$ . 3 V/5 V operation:  $3.0 \text{ V} \le V_{DD1} \le 3.6 \text{ V}$ ,  $4.5 \text{ V} \le V_{DD2} \le 5.5 \text{ V}$ ; all minimum/maximum specifications apply over the entire recommended operating range, unless otherwise noted; all typical specifications are at  $T_A = 25^{\circ}\text{C}$ ,  $V_{DD1} = 3.0 \text{ V}$ ,  $V_{DD2} = 5.0 \text{ V}$ ; or  $V_{DD1} = 5.0 \text{ V}$ ,  $V_{DD2} = 3.0 \text{ V}$ .

| Parameter                                       | Symbol                              | Min                                           | Тур   | Max                                         | Unit | Test Conditions                                                               |

|-------------------------------------------------|-------------------------------------|-----------------------------------------------|-------|---------------------------------------------|------|-------------------------------------------------------------------------------|

| DC SPECIFICATIONS                               |                                     |                                               |       |                                             |      |                                                                               |

| Input Supply Current per Channel,<br>Quiescent  | Iddi (Q)                            |                                               |       |                                             |      |                                                                               |

| 5 V/3 V Operation                               |                                     |                                               | 0.50  | 0.6                                         | mA   |                                                                               |

| 3 V/5 V Operation                               |                                     |                                               | 0.26  | 0.35                                        | mA   |                                                                               |

| Output Supply Current per Channel,<br>Quiescent | I <sub>DDO (Q)</sub>                |                                               |       |                                             |      |                                                                               |

| 5 V/3 V Operation                               |                                     |                                               | 0.11  | 0.20                                        | mA   |                                                                               |

| 3 V/5 V Operation                               |                                     |                                               | 0.19  | 0.25                                        | mA   |                                                                               |

| Total Supply Current, Two Channels <sup>1</sup> |                                     |                                               |       |                                             |      |                                                                               |

| DC to 2 Mbps                                    |                                     |                                               |       |                                             |      |                                                                               |

| V <sub>DD1</sub> Supply Current                 | IDD1 (Q)                            |                                               |       |                                             |      |                                                                               |

| 5 V/3 V Operation                               |                                     |                                               | 1.1   | 1.4                                         | mA   | DC to 1 MHz logic signal frequency                                            |

| 3 V/5 V Operation                               |                                     |                                               | 0.6   | 1.0                                         | mA   | DC to 1 MHz logic signal frequency                                            |

| V <sub>DD2</sub> Supply Current                 | I <sub>DD2 (Q)</sub>                |                                               |       |                                             |      |                                                                               |

| 5 V/3 V Operation                               |                                     |                                               | 0.2   | 0.6                                         | mA   | DC to 1 MHz logic signal frequency                                            |

| 3 V/5 V Operation                               |                                     |                                               | 0.5   | 0.8                                         | mA   | DC to 1 MHz logic signal frequency                                            |

| 10 Mbps                                         |                                     |                                               |       |                                             |      |                                                                               |

| VDD1 Supply Current                             | IDD1 (Q)                            |                                               |       |                                             |      |                                                                               |

| 5 V/3 V Operation                               |                                     |                                               | 4.3   | 5.5                                         | mA   | 5 MHz logic signal frequency                                                  |

| 3 V/5 V Operation                               |                                     |                                               | 2.2   | 3.4                                         | mA   | 5 MHz logic signal frequency                                                  |

| V <sub>DD2</sub> Supply Current                 | IDD2 (Q)                            |                                               |       |                                             |      |                                                                               |

| 5 V/3 V Operation                               |                                     |                                               | 0.7   | 1.1                                         | mA   | 5 MHz logic signal frequency                                                  |

| 3 V/5 V Operation                               |                                     |                                               | 1.3   | 2.0                                         | mA   | 5 MHz logic signal frequency                                                  |

| 25 Mbps                                         |                                     |                                               |       |                                             |      |                                                                               |

| V <sub>DD1</sub> Supply Current                 | I <sub>DD1 (Q)</sub>                |                                               |       |                                             |      |                                                                               |

| 5 V/3 V Operation                               |                                     |                                               | 10    | 13                                          | mA   | 12.5 MHz logic signal frequency                                               |

| 3 V/5 V Operation                               |                                     |                                               | 5.2   | 7.7                                         | mA   | 12.5 MHz logic signal frequency                                               |

| V <sub>DD2</sub> Supply Current                 | IDD2 (Q)                            |                                               |       |                                             |      |                                                                               |

| 5 V/3 V Operation                               |                                     |                                               | 1.5   | 2.0                                         | mA   | 12.5 MHz logic signal frequency                                               |

| 3 V/5 V Operation                               |                                     |                                               | 2.8   | 3.4                                         | mA   | 12.5 MHz logic signal frequency                                               |

| Input Currents                                  | Iia ,Iib                            | -10                                           | +0.01 | +10                                         | μΑ   |                                                                               |

| Logic High Input Threshold                      | VIH                                 | 0.7 (V <sub>DD1</sub> or V <sub>DD2</sub> )   |       |                                             | V    |                                                                               |

| Logic Low Input Threshold                       | VIL                                 |                                               |       | 0.3 (V <sub>DD1</sub> or V <sub>DD2</sub> ) | V    |                                                                               |

| Logic High Output Voltages                      | Voah, Vobh                          | (V <sub>DD1</sub> or V <sub>DD2</sub> ) – 0.1 | 3.0   |                                             | V    | $I_{\text{Ox}} = -20 \; \mu\text{A} \text{, } V_{\text{Ix}} = V_{\text{IxH}}$ |

|                                                 |                                     | (V <sub>DD1</sub> or V <sub>DD2</sub> ) – 0.5 | 2.8   |                                             | V    | $I_{Ox} = -4 \text{ mA}, V_{Ix} = V_{IxH}$                                    |

| Logic Low Output Voltages                       | V <sub>OAL</sub> , V <sub>OBL</sub> |                                               | 0.0   | 0.1                                         | V    | $I_{\text{Ox}} = 20 \; \mu\text{A},  V_{\text{Ix}} = V_{\text{IxL}}$          |

|                                                 |                                     |                                               | 0.04  | 0.1                                         | V    | $I_{\text{Ox}} = 400 \; \mu\text{A},  V_{\text{Ix}} = V_{\text{IxL}}$         |

|                                                 |                                     |                                               | 0.2   | 0.4                                         | V    | $I_{Ox} = 4 \text{ mA}, V_{Ix} = V_{IxL}$                                     |

| SWITCHING SPECIFICATIONS                        |                                     |                                               |       |                                             |      |                                                                               |

| Minimum Pulse Width <sup>2</sup>                | PW                                  |                                               | 20    | 40                                          | ns   |                                                                               |

| Maximum Data Rate <sup>3</sup>                  |                                     | 25                                            | 50    |                                             | Mbps |                                                                               |

| Propagation Delay <sup>4</sup>                  | tphl, tplh                          | 20                                            |       | 50                                          | ns   |                                                                               |

| Pulse Width Distortion, $ t_{PLH} - t_{PHL} ^4$ | PWD                                 |                                               |       | 3                                           | ns   |                                                                               |

| Propagation Delay Skew⁵                         | t <sub>PSK</sub>                    |                                               |       | 15                                          | ns   |                                                                               |

| Channel-to-Channel Matching <sup>6</sup>        | tpskcd/tpskod                       |                                               |       | 3                                           | ns   |                                                                               |

| Output Rise/Fall Time (10% to 90%)              | t <sub>R</sub> /t <sub>F</sub>      |                                               |       |                                             |      |                                                                               |

| 5 V/3 V Operation                               |                                     |                                               | 3.0   |                                             | ns   |                                                                               |

| 3 V/5 V Operation                               |                                     |                                               | 2.5   |                                             | ns   |                                                                               |

### **Data Sheet**

## ADuM1200-EP

| Parameter                                                 | Symbol               | Min | Тур Мах | Unit        | Test Conditions                                                              |

|-----------------------------------------------------------|----------------------|-----|---------|-------------|------------------------------------------------------------------------------|

| Common-Mode Transient Immunity                            |                      |     |         |             |                                                                              |

| Logic High Output <sup>7</sup>                            | CM <sub>H</sub>      | 25  | 35      | kV/μs       | $V_{lx} = V_{DD1}, V_{DD2}, V_{CM} = 1000 V,$<br>transient magnitude = 800 V |

| Logic Low Output <sup>7</sup>                             | CM∟                  | 25  | 35      | kV/μs       | $V_{Ix} = 0 V$ , $V_{CM} = 1000 V$ ,<br>transient magnitude = 800 V          |

| Refresh Rate                                              | fr                   |     |         |             |                                                                              |

| 5 V/3 V Operation                                         |                      |     | 1.2     | Mbps        |                                                                              |

| 3 V/5 V Operation                                         |                      |     | 1.1     | Mbps        |                                                                              |

| Input Dynamic Supply Current per<br>Channel <sup>8</sup>  | I <sub>DDI (D)</sub> |     |         |             |                                                                              |

| 5 V/3 V Operation                                         |                      |     | 0.19    | mA/<br>Mbps |                                                                              |

| 3 V/5 V Operation                                         |                      |     | 0.10    | mA/<br>Mbps |                                                                              |

| Output Dynamic Supply Current per<br>Channel <sup>8</sup> | I <sub>DDO(D)</sub>  |     |         |             |                                                                              |

| 5 V/3 V Operation                                         |                      |     | 0.03    | mA/<br>Mbps |                                                                              |

| 3 V/5 V Operation                                         |                      |     | 0.05    | mA/<br>Mbps |                                                                              |

<sup>1</sup> The supply current values are for both channels combined when running at identical data rates. Output supply current values are specified with no output load present. <sup>2</sup> The minimum pulse width is the shortest pulse width at which the specified pulse width distortion is guaranteed.

<sup>3</sup> The maximum data rate is the fastest data rate at which the specified pulse width distortion is guaranteed.

$^{4}$  t<sub>PHL</sub> propagation delay is measured from the 50% level of the falling edge of the V<sub>ix</sub> signal to the 50% level of the falling edge of the V<sub>ox</sub> signal. t<sub>PLH</sub> propagation delay is measured from the 50% level of the rising edge of the V<sub>ix</sub> signal to the 50% level of the rising edge of the V<sub>ox</sub> signal.

<sup>5</sup> t<sub>PSK</sub> is the magnitude of the worst-case difference in t<sub>PHL</sub> and/or t<sub>PLH</sub> that is measured between units at the same operating temperature, supply voltages, and output load within the recommended operating conditions.

<sup>6</sup> Codirectional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on the same side of the isolation barrier. Opposing directional channel-to-channel matching is the absolute value of the difference in propagation delays between any two channels with inputs on opposing sides of the isolation barrier.

$^{7}$  CM<sub>H</sub> is the maximum common-mode voltage slew rate that can be sustained while maintaining V<sub>ox</sub> > 0.8 V<sub>DD2</sub>. CM<sub>L</sub> is the maximum common-mode voltage slew rate that can be sustained while maintaining V<sub>ox</sub> > 0.8 V. The common-mode voltage slew rates apply to both rising and falling common-mode voltage edges. The transient magnitude is the range over which the common mode is slewed.

<sup>8</sup> Dynamic supply current is the incremental amount of supply current required for a 1 Mbps increase in the signal data rate.

### PACKAGE CHARACTERISTICS

#### Table 4.

| Parameter                                      | Symbol           | Min Typ          | Max | Unit | Test Conditions                                        |

|------------------------------------------------|------------------|------------------|-----|------|--------------------------------------------------------|

| Resistance (Input-to-Output) <sup>1</sup>      | Ri-o             | 10 <sup>12</sup> |     | Ω    |                                                        |

| Capacitance (Input-to-Output) <sup>1</sup>     | CI-O             | 1.0              |     | pF   | f = 1 MHz                                              |

| Input Capacitance                              | Cı               | 4.0              |     | pF   |                                                        |

| IC Junction-to-Case Thermal Resistance, Side 1 | θ <sub>JCI</sub> | 46               |     | °C/W | Thermocouple located at<br>center of package underside |

| IC Junction-to-Case Thermal Resistance, Side 2 | θιςο             | 41               |     | °C/W |                                                        |

<sup>1</sup> The device is considered a 2-terminal device; Pin 1, Pin, 2, Pin 3, and Pin 4 are shorted together, and Pin 5, Pin 6, Pin 7, and Pin 8 are shorted together.

### **REGULATORY INFORMATION**

The ADuM1200-EP is approved by the organizations listed in Table 5. See Table 10 for details regarding recommended maximum working voltages for specific cross-isolation waveforms and insulation levels.

#### Table 5.

| UL                                                                  | CSA                                                                                                                                                                                                                        | VDE                                                                                 |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Recognized Under 1577 Component<br>Recognition Program <sup>1</sup> | Approved under CSA Component Acceptance<br>Notice #5A                                                                                                                                                                      | Certified according to DIN V VDE<br>V 0884-10 (VDE V 0884-10): 2006-12 <sup>2</sup> |

| Single/Basic 2500 V rms Isolation Voltage                           | Basic insulation per CSA 60950-1-03 and<br>IEC 60950-1, 400 V rms (566 peak) maximum<br>working voltage<br>Functional insulation per CSA 60950-1-03 and<br>IEC 60950-1, 800 V rms (1131 V peak) maximum<br>working voltage | Reinforced insulation, 560 V peak                                                   |

| File E214100                                                        | File 205078                                                                                                                                                                                                                | File 2471900-4880-0001                                                              |

<sup>1</sup> In accordance with UL 1577, each ADuM1200UR-EP is proof tested by applying an insulation test voltage  $\geq$  3000 V rms for 1 second (current leakage detection limit = 5  $\mu$ A).

<sup>2</sup> In accordance with DIN V VDE V 0884-10, each ADuM1200UR-EP is proof tested by applying an insulation test voltage ≥1050 V peak for 1 second (partial discharge detection limit = 5 pC). The \* marking branded on the component designates DIN V VDE V 0884-10 approval.

### INSULATION AND SAFETY-RELATED SPECIFICATIONS

#### Table 6.

| Parameter                                        | Symbol            | Value | Unit   | Conditions                                                                                                                   |

|--------------------------------------------------|-------------------|-------|--------|------------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage              |                   | 2500  | V rms  | 1 minute duration                                                                                                            |

| Clearance in the Plane of the PCB                | CL <sub>PCB</sub> | 4.5   | mm min | Measured from input terminals to output terminals,<br>shortest line of sight distance through air in the<br>plane of the PCB |

| Minimum External Air Gap (Clearance)             | L(I01)            | 4.0   | mm min | Measured from input terminals to output terminals, shortest distance through air                                             |

| Minimum External Tracking (Creepage)             | L(I02)            | 4.0   | mm min | Measured from input terminals to output terminals, shortest distance path along body                                         |

| Minimum Internal Gap (Internal Clearance)        |                   | 0.017 | mm min | Insulation distance through insulation                                                                                       |

| Tracking Resistance (Comparative Tracking Index) | CTI               | >400  | V      | DIN IEC 112/VDE 0303 Part 1                                                                                                  |

| Isolation Group                                  |                   | П     |        | Material Group (DIN VDE 0110, 1/89, Table 1)                                                                                 |

### DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12 INSULATION CHARACTERISTICS

This isolator is suitable for reinforced isolation within the safety limit data only. Maintenance of the safety data is ensured by protective circuits. Note that the \* marking on the package denotes DIN V VDE V 0884-10 approval for a 560 V peak working voltage.

| Table 7.                                                    |                                                                                                                 |                 | _              |        |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|----------------|--------|

| Description                                                 | Conditions                                                                                                      | Symbol          | Characteristic | Unit   |

| Installation Classification per DIN VDE 0110                |                                                                                                                 |                 |                |        |

| For Rated Mains Voltage ≤ 150 V rms                         |                                                                                                                 |                 | I to IV        |        |

| For Rated Mains Voltage ≤ 300 V rms                         |                                                                                                                 |                 | l to III       |        |

| For Rated Mains Voltage ≤ 400 V rms                         |                                                                                                                 |                 | l to ll        |        |

| Climatic Classification                                     |                                                                                                                 |                 | 40/125/21      |        |

| Pollution Degree per DIN VDE 0110, Table 1                  |                                                                                                                 |                 | 2              |        |

| Maximum Working Insulation Voltage                          |                                                                                                                 | VIORM           | 560            | V peak |

| Input-to-Output Test Voltage, Method B1                     | $V_{IORM} \times 1.875 = V_{PR}$ , 100% production test,<br>t <sub>m</sub> = 1 second, partial discharge < 5 pC | V <sub>PR</sub> | 1050           | V peak |

| Input-to-Output Test Voltage, Method A                      | $V_{IORM} \times 1.6 = V_{PR}$ , $t_m = 60$ seconds, partial discharge < 5 pC                                   | V <sub>PR</sub> |                |        |

| After Environmental Tests Subgroup 1                        |                                                                                                                 |                 | 896            | V peak |

| After Input and/or Safety Test Subgroup 2<br>and Subgroup 3 | $V_{IORM} \times 1.2 = V_{PR}$ , $t_m = 60$ seconds, partial discharge < 5 pC                                   |                 | 672            | V peak |

| Highest Allowable Overvoltage                               | Transient overvoltage, $t_{TR} = 10$ seconds                                                                    | VTR             | 4000           | V peak |

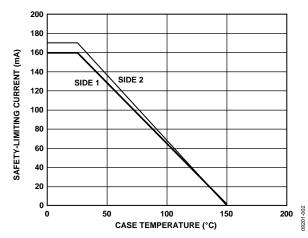

| Safety-Limiting Values                                      | Maximum value allowed in the event of a failure (see Figure 2)                                                  |                 |                |        |

| Case Temperature                                            |                                                                                                                 | Ts              | 150            | °C     |

| Side 1 Current                                              |                                                                                                                 | I <sub>S1</sub> | 160            | mA     |

| Side 2 Current                                              |                                                                                                                 | I <sub>S2</sub> | 170            | mA     |

| Insulation Resistance at Ts                                 | $V_{10} = 500 V$                                                                                                | Rs              | >109           | Ω      |

Figure 2. Thermal Derating Curve, Dependence of Safety-Limiting Values on Case Temperature per DIN V VDE V 0884-10

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                                           | Rating          |

|---------------------------------------------------------------------|-----------------|

| Operating Temperature (T <sub>A</sub> )                             | -55°C to +125°C |

| Supply Voltages (V <sub>DD1</sub> , V <sub>DD2</sub> ) <sup>1</sup> | 3.0 V to 5.5 V  |

| Input Signal Rise and Fall Times                                    | 1.0 ms          |

<sup>1</sup> All voltages are relative to their respective ground.

## **ABSOLUTE MAXIMUM RATINGS**

Ambient temperature = 25°C, unless otherwise noted.

#### Table 9.

| Parameter                                                           | Rating                             |  |  |

|---------------------------------------------------------------------|------------------------------------|--|--|

| Storage Temperature (T <sub>ST</sub> )                              | –55°C to +150°C                    |  |  |

| Ambient Operating Temperature (T <sub>A</sub> )                     | −55°C to +125°C                    |  |  |

| Supply Voltages (V <sub>DD1</sub> , V <sub>DD2</sub> ) <sup>1</sup> | –0.5 V to +7.0 V                   |  |  |

| Input Voltages (V <sub>IA</sub> , V <sub>IB</sub> ) <sup>1, 2</sup> | -0.5 V to V <sub>DDI</sub> + 0.5 V |  |  |

| Output Voltages (V <sub>OA</sub> , V <sub>OB</sub> ) <sup>1,2</sup> | -0.5 V to V <sub>DDO</sub> + 0.5 V |  |  |

| Average Output Current per Pin $(I_0)^3$                            | –11 mA to +11 mA                   |  |  |

| Common-Mode Transients (CML, CMH) <sup>4</sup>                      | –100 kV/µs to +100 kV/µs           |  |  |

<sup>1</sup> All voltages are relative to their respective ground.

$^2$   $V_{\text{DD}}$  and  $V_{\text{DD}}$  refer to the supply voltages on the input and output sides of a given channel, respectively.

<sup>3</sup> See Figure 2 for maximum rated current values for various temperatures.

<sup>4</sup> Refers to common-mode transients across the insulation barrier.

Common-mode transients exceeding the absolute maximum ratings

can cause latch-up or permanent damage.

10 14

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

| Table 10. Maximum Continuous Working Voltage |            |       |                          |  |  |  |

|----------------------------------------------|------------|-------|--------------------------|--|--|--|

| Parameter                                    | Constraint |       |                          |  |  |  |

| AC Voltage,                                  |            |       |                          |  |  |  |

| Bipolar Waveform                             | 565        | VPEAK | 50-year minimum lifetime |  |  |  |

| Unipolar Waveform                            | 1131       | VPEAK | 50-year minimum lifetime |  |  |  |

| DC Voltage                                   | 1131       | VPEAK | 50-year minimum lifetime |  |  |  |

<sup>1</sup>Refers to continuous voltage magnitude imposed across the isolation barrier.

#### Table 11. Truth Table (Positive Logic)

| VIA Input <sup>1</sup> | V <sub>IB</sub> Input <sup>1</sup> | V <sub>DD1</sub> State | V <sub>DD2</sub> State | Voa Output <sup>1</sup> | Vob Output <sup>1</sup> | Notes                                                                                     |

|------------------------|------------------------------------|------------------------|------------------------|-------------------------|-------------------------|-------------------------------------------------------------------------------------------|

| Н                      | Н                                  | Powered                | Powered                | Н                       | Н                       |                                                                                           |

| L                      | L                                  | Powered                | Powered                | L                       | L                       |                                                                                           |

| Н                      | L                                  | Powered                | Powered                | Н                       | L                       |                                                                                           |

| L                      | н                                  | Powered                | Powered                | L                       | н                       |                                                                                           |

| Х                      | Х                                  | Unpowered              | Powered                | н                       | Н                       | Outputs return to the input state within 1 $\mu$ s of V <sub>DDI</sub> power restoration. |

| Х                      | х                                  | Powered                | Unpowered              | Indeterminate           | Indeterminate           | Outputs return to the input state within 1 $\mu$ s of V <sub>DDO</sub> power restoration. |

$^{1}$  H = high, L = low, X = undetermined/not relevant.

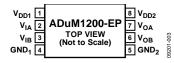

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 3. Pin Configuration

| Pin No. | Mnemonic         | Description                                     |

|---------|------------------|-------------------------------------------------|

| 1       | V <sub>DD1</sub> | Supply Voltage for Isolator Side 1.             |

| 2       | VIA              | Logic Input A.                                  |

| 3       | VIB              | Logic Input B.                                  |

| 4       | GND <sub>1</sub> | Ground 1. Ground reference for Isolator Side 1. |

| 5       | GND <sub>2</sub> | Ground 2. Ground reference for Isolator Side 2. |

| 6       | V <sub>OB</sub>  | Logic Output B.                                 |

| 7       | VOA              | Logic Output A.                                 |

| 8       | V <sub>DD2</sub> | Supply Voltage for Isolator Side 2.             |

#### Table 12. Pin Function Descriptions

## ADuM1200-EP

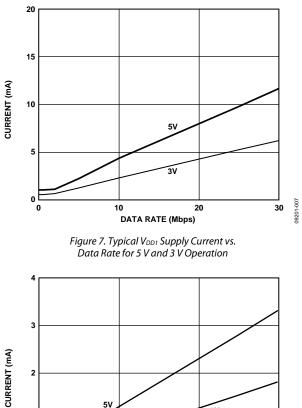

## **TYPICAL PERFORMANCE CHARACTERISTICS**

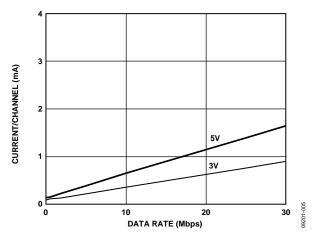

Figure 5. Typical Output Supply Current per Channel vs. Data Rate for 5 V and 3 V Operation (No Output Load)

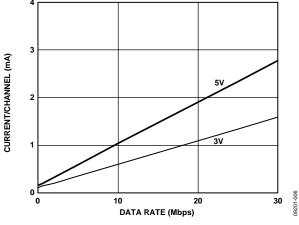

Figure 6. Typical Output Supply Current per Channel vs. Data Rate for 5 V and 3 V Operation (15 pF Output Load)

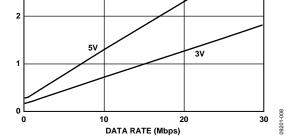

Figure 8. Typical V<sub>DD2</sub> Supply Current vs. Data Rate for 5 V and 3 V Operation

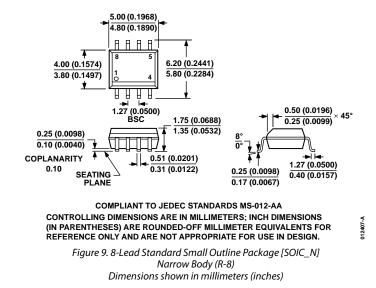

## **OUTLINE DIMENSIONS**

#### **ORDERING GUIDE**

| Model             | Number<br>of Inputs,<br>V <sub>DD1</sub> Side | Number<br>of Inputs,<br>V <sub>DD2</sub> Side | Maximum<br>Data Rate<br>(Mbps) | Maximum<br>Propagation<br>Delay, 5 V (ns) | Maximum<br>Pulse Width<br>Distortion (ns) | Temperature<br>Range | Package<br>Description | Package<br>Option |

|-------------------|-----------------------------------------------|-----------------------------------------------|--------------------------------|-------------------------------------------|-------------------------------------------|----------------------|------------------------|-------------------|

| ADuM1200UR-EP     | 2                                             | 0                                             | 25                             | 45                                        | 3                                         | –55°C to +125°C      | 8-Lead SOIC_N          | R-8               |

| ADuM1200UR-EP-RL7 | 2                                             | 0                                             | 25                             | 45                                        | 3                                         | –55°C to +125°C      | 8-Lead SOIC_N          | R-8               |

## NOTES

## NOTES

## ADuM1200-EP

## NOTES

www.analog.com

©2010–2014 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D09201-0-2/14(B)