# 8 GHz to 16 GHz, 4-Channel, X Band and Ku Band Beamformer

### **FEATURES**

- ▶ 8 GHz to 16 GHz frequency range

- ► Half-duplex for transmit and receive modes

- Single-pin transmit and receive control

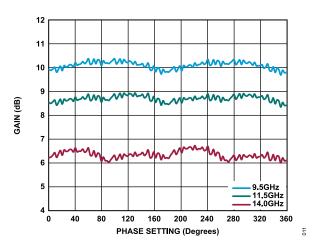

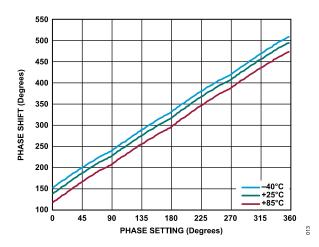

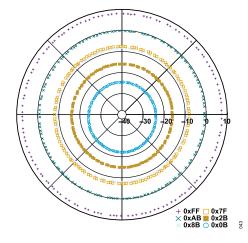

- ▶ 360° phase adjustment range

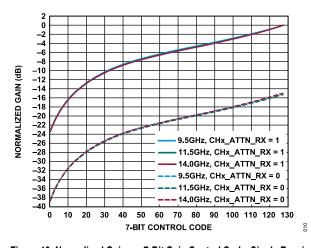

- ▶ 2.8° phase resolution

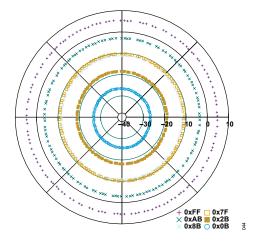

- ▶ ≥31 dB gain adjustment range

- ► ≤0.5 dB gain resolution

- ▶ Bias and control for external transmit and receive modules

- Memory for 121 prestored beam positions

- ► Four -20 dBm to +10 dBm power detectors

- Integrated temperature sensor

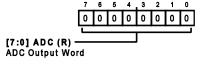

- Integrated 8-bit ADC for power detectors and temperature sensor

- Programmable bias modes

- ▶ 4-wire SPI interface

#### **APPLICATIONS**

- ▶ Phased array radar

- Satellite communications systems

## **GENERAL DESCRIPTION**

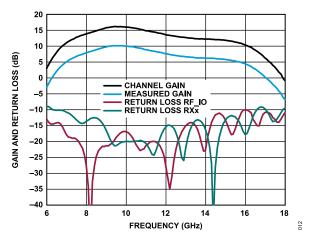

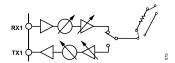

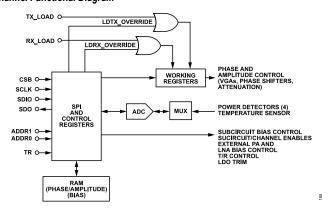

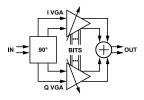

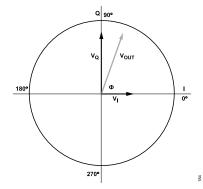

The ADAR1000 is a 4-channel, X and Ku frequency band, beamforming core chip for phased arrays. This device operates in half-duplex between receive and transmit modes. In receive mode, input signals pass through four receive channels and are combined and output at the common RF\_IO pin. In transmit mode, the RF\_IO input signal is split and passes through the four transmit channels. In both modes, the ADAR1000 provides a ≥31 dB gain adjustment range and a full 360° phase adjustment range in each radio frequency (RF) channel, with 6-bit resolution (less than ≤0.5 dB and 2.8°, respectively).

A simple 4-wire serial port interface (SPI) controls all of the on-chip registers. In addition, two address pins allow SPI control of up to four devices on the same serial lines. Dedicated transmit and receive load pins also provide synchronization of all ADAR1000 chips in the same array, and a single pin controls fast switching between the transmit and receive modes.

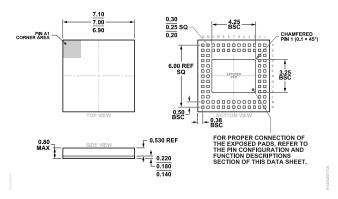

The ADAR1000 is fabricated in a silicon-germanium, bipolar CMOS (BiCMOS) process. The device is available in a compact, 88-terminal,  $7 \text{ mm} \times 7 \text{ mm}$ , LGA package and is specified from  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ .

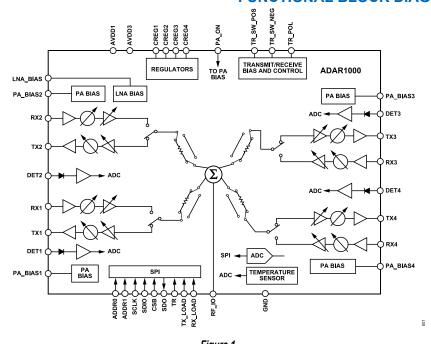

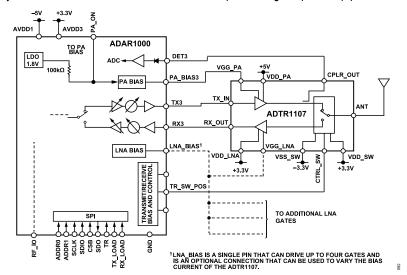

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **TABLE OF CONTENTS**

| Features                                    | 1            | Memory Access                               | 32       |

|---------------------------------------------|--------------|---------------------------------------------|----------|

| Applications                                | 1            | Calibration                                 |          |

| General Description                         | 1            | Memory Address Decoding                     | 34       |

| Functional Block Diagram                    | 1            | Memory Map                                  | 34       |

| Specifications                              | 5            | Applications Information                    | 35       |

| Timing Specifications                       |              | Gain Control Registers                      | 35       |

| Absolute Maximum Ratings                    |              | Switched Attenuator Control                 |          |

| Thermal Resistance                          |              | Phase Control Registers                     | 36       |

| ESD Caution                                 | 11           | Transmit and Receive Subcircuit Control     |          |

| Pin Configuration and Function Description  | s 12         | Transmit and Receive Switch Driver Control. | 38       |

| Typical Performance Characteristics         |              | PA Bias Output Control                      |          |

| Equivalent Circuits                         |              | LNA Bias Output Control                     |          |

| Theory of Operation                         |              | PA Bias, LNA Bias, and Switch Bias Setup    |          |

| RF Path                                     |              | Examples                                    | 41       |

| Digital Interface                           |              | Transmit/Receive Delay Control              |          |

| Phase and Gain Control                      |              | ADAR1000 and ADTR1107                       |          |

| Receive Output Noise and Noise Figure       |              | Powering the ADAR1000                       |          |

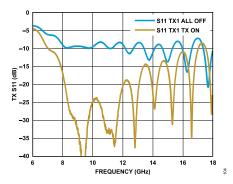

| Transmit and Receive Control                |              | Return Loss While Powered Down              |          |

| RF Subcircuit Bias Control                  |              | SPI Considerations                          |          |

| RF Subcircuit Enables and Disables          |              | SPI Programming Example                     |          |

| Power Detectors                             |              | Register Map                                |          |

| External Amplifier Bias Drivers             |              | Register Descriptions                       |          |

| External Switch Control                     |              | Outline Dimensions                          |          |

| ADC Operation                               |              | Ordering Guide                              |          |

| Chip Addressing                             |              | Evaluation Boards                           |          |

| REVISION HISTORY 7/2022—Rev. A to Rev. B    |              |                                             |          |

|                                             |              |                                             | 1        |

|                                             |              |                                             |          |

|                                             |              | d Note 1, Table 2                           |          |

| ,,                                          |              | on, and Figure 4 Caption                    |          |

|                                             | -            |                                             |          |

| Changes to SPI Block Write Mode Section     |              |                                             | 10<br>10 |

|                                             |              | ad All Mode Section                         |          |

| <u> </u>                                    |              | ad All Mode Geoloff                         |          |

| •                                           |              |                                             |          |

|                                             |              |                                             |          |

|                                             |              |                                             |          |

| Changes to Typical Porformance Character    | rictics Soct | ion                                         | 12       |

|                                             |              |                                             |          |

| •                                           |              |                                             |          |

|                                             |              |                                             |          |

|                                             |              |                                             |          |

|                                             |              |                                             |          |

|                                             |              | ın                                          |          |

|                                             |              |                                             |          |

|                                             |              |                                             |          |

| Added IVI Odbollodik Eliables alid Disables | , OCCIOII    |                                             | JU       |

# **TABLE OF CONTENTS**

|                                                                                          | 30             |

|------------------------------------------------------------------------------------------|----------------|

| Added Figure 93 and Figure 94                                                            | 30             |

| Changes to Power Detectors Section                                                       | 31             |

| Moved Figure 94                                                                          |                |

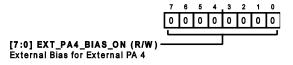

| Changed External Amplifier Bias DACs Section to External Amplifier Bias Drivers Section  | 31             |

| Changes to External Amplifier Bias Drivers Section                                       | 31             |

| Moved Figure 95                                                                          | 31             |

| Changes to External Switch Control Section                                               |                |

| Moved Figure 96 and Figure 97                                                            |                |

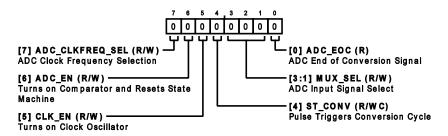

| Changes to ADC Operation Section                                                         | 32             |

| Added Table 7, Renumbered Sequentially                                                   | 32             |

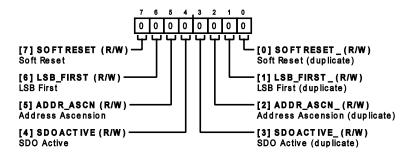

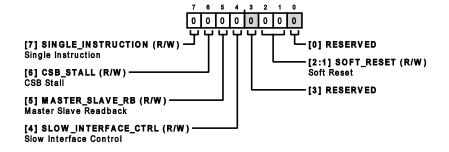

| Changes to Chip Addressing Section                                                       |                |

| Changes to Memory Access Section                                                         |                |

| Added Single Memory Fetch Section                                                        |                |

| Added Bias Setting Memory Fetch Section                                                  |                |

| Added Sequencing Through Memory Beam Positions Section                                   | 33             |

| Added Toggling Between RAM and Registers Section                                         |                |

| Added Memory Counter Attributes Section                                                  |                |

| Added Memory Address Decoding Section and Table 8                                        |                |

| Deleted Table 8 to Table 12                                                              |                |

| Added Memory Map Section                                                                 |                |

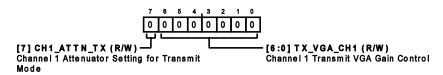

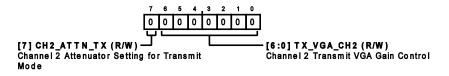

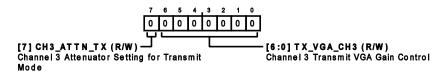

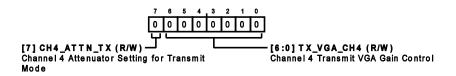

| Changes to Gain Control Registers Section                                                |                |

| Changes to Switched Attenuator Control Section and Table 8                               |                |

| Changes to Phase Control Registers Section and Table 9                                   |                |

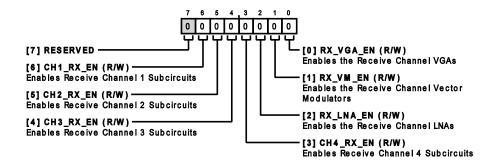

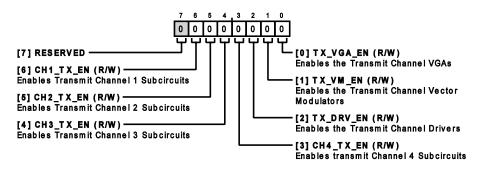

| Changes to Transmit and Receive Subcircuit Control Section                               |                |

| Changed TR_SOURCE = 0 (SPI Control) Section to SPI Control (TR_SOURCE = 0) Section       | 37             |

| Changed TR_SOURCE = 1 (TR Pin Control) Section to TR Pin Control (TR_SOURCE = 1) Section |                |

| Changes to Transmit and Receive Switch Driver Control Section and Table 13               |                |

| Changes to PA Bias Output Control Section                                                |                |

| Added Table 15                                                                           |                |

| Moved Table 16                                                                           |                |

| Changes to LNA Bias Output Control Section and Table 18  Added Table 17                  |                |

| Added PA Bias, LNA Bias, and Switch Bias Setup Examples Section                          |                |

| Added PA Bias Setup for TR Pin Control Example Section and Table 19                      |                |

|                                                                                          |                |

| Added PA Bias Setup for SPI Control Example Section and Table 20                         |                |

| Added LNA Bias Setup for TR Pin Control Example Section and Table 21                     |                |

| Added Allowable PA and LNA States While in SPI Control Section and Table 23              |                |

| Added Switch Bias Setup for TR Control Example Section and Table 24                      |                |

| Added Switch Bias Setup for SPI Control Example Section and Table 25                     |                |

| Changes to Transmit/Receive Delay Control Section                                        |                |

|                                                                                          |                |

| Added PA Rias Silicon Error When Using Delay Section                                     |                |

| Added PA Bias Silicon Error When Using Delay Section                                     | 41             |

| Added ADAR1000 and ADTR1107 Section                                                      |                |

| Added ADAR1000 and ADTR1107 SectionAdded Interfacing Section                             | 44             |

| Added ADAR1000 and ADTR1107 SectionAdded Interfacing Section                             | 44<br>44       |

| Added ADAR1000 and ADTR1107 SectionAdded Interfacing Section                             | 44<br>44<br>45 |

**Data Sheet**

# **TABLE OF CONTENTS**

| Moved Powering the ADAR1000 Section                                       | 45 |

|---------------------------------------------------------------------------|----|

| Changes to Figure 98 Caption to Figure 101 Caption                        | 45 |

| Added Return Loss While Powered Down Section and Figure 103 to Figure 105 | 47 |

| Added SPI Considerations Section and Table 27                             | 47 |

| Added Register 0x00 Section                                               | 47 |

| Added SDO Readback Problem and Solution Section, Table 28, and Table 29   | 48 |

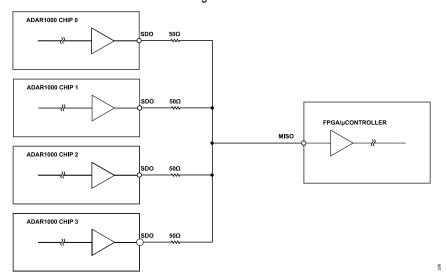

| Added SDO Bus Connections Section and Figure 106                          | 49 |

| Changes to Table 30 and Note 1, Table 31                                  | 50 |

| Changes to Table 32                                                       |    |

| Changes to Register Descriptions Section                                  | 57 |

| Deleted Table 26                                                          |    |

| Changes to Table 43 to Table 46                                           | 60 |

| Changes to Table 55 to Table 58                                           | 63 |

| Changes to Table 67                                                       | 66 |

| Changes to Table 76 and Table 77                                          | 69 |

| Changes to Table 83                                                       | 72 |

| Changes to Table 108                                                      | 78 |

# **SPECIFICATIONS**

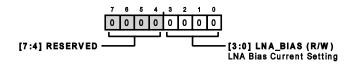

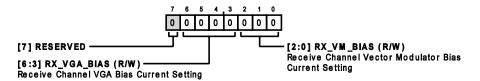

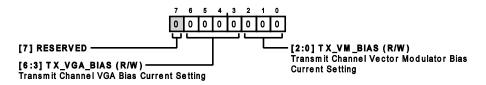

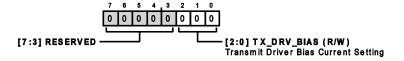

AVDD1 = -5 V, AVDD3 = +3.3 V,  $T_A$  = 25°C, and the device is programmed to the maximum channel gain and the nominal bias conditions on all channels, unless otherwise noted. Nominal bias register settings: Register 0x034 = 0x08, Register 0x035 = 0x55, Register 0x036 = 0x2D, and Register 0x37 = 0x06. Low power bias register settings: Register 0x034 = 0x05, Register 0x035 = 0x1A, Register 0x036 = 0x2A, and Register 0x37 = 0x03.

Table 1.

| Parameter                                | Test Conditions/Comments             | Min Typ | Max | Unit    |

|------------------------------------------|--------------------------------------|---------|-----|---------|

| OPERATING CONDITIONS                     |                                      |         |     |         |

| RF Range                                 |                                      | 8       | 16  | GHz     |

| Operating Temperature                    |                                      | -40     | +85 | °C      |

| TRANSMIT SECTION                         | RF_IO, TX1, TX2, TX3, and TX4 pins   |         |     |         |

| Maximum Single Channel Gain <sup>1</sup> |                                      |         |     |         |

| 9.5 GHz                                  |                                      | 21      |     | dB      |

| 11.5 GHz                                 |                                      | 19      |     | dB      |

| 14 GHz                                   |                                      | 16      |     | dB      |

| Gain Flatness vs. Frequency              | Across any 1 GHz bandwidth           |         |     | dB      |

| ,                                        | From 9 GHz to 14 GHz                 | ±1.0    |     | dB      |

|                                          | From 8 GHz to 15 GHz                 | ±1.7    |     | dB      |

| Gain Variation vs. Temperature           | 11.5 GHz                             | ±2.5    |     | dB      |

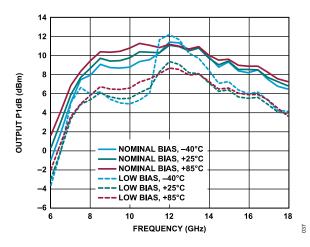

| Output 1 dB Compression (P1dB)           | Maximum gain setting                 |         |     |         |

| Nominal Bias Setting                     | 39                                   |         |     |         |

| 9.5 GHz                                  |                                      | 10      |     | dBm     |

| 11.5 GHz                                 |                                      | 10      |     | dBm     |

| 14 GHz                                   |                                      | 10      |     | dBm     |

| Low Bias Setting                         |                                      |         |     |         |

| 9.5 GHz                                  |                                      | 6       |     | dBm     |

| 11.5 GHz                                 |                                      | 8       |     | dBm     |

| 14 GHz                                   |                                      | 7       |     | dBm     |

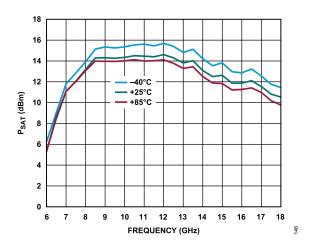

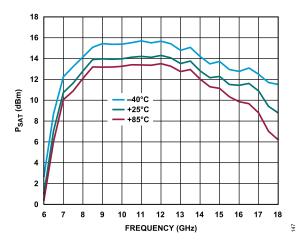

| Saturated Power (P <sub>SAT</sub> )      | Maximum gain setting                 |         |     |         |

| Nominal Bias Setting                     |                                      |         |     |         |

| 9.5 GHz                                  |                                      | 14      |     | dBm     |

| 11.5 GHz                                 |                                      | 14      |     | dBm     |

| 14 GHz                                   |                                      | 13      |     | dBm     |

| Low Bias Setting                         |                                      |         |     | u Diii  |

| 9.5 GHz                                  |                                      | 14      |     | dBm     |

| 11.5 GHz                                 |                                      | 14      |     | dBm     |

| 14 GHz                                   |                                      | 13      |     | dBm     |

| Gain Resolution                          |                                      | ≤0.5    |     | dB      |

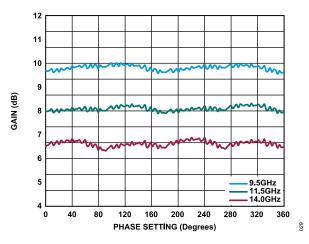

| Root Mean Square (RMS) Gain Error        | Over phase settings and frequencies  | 0.2     |     | dB      |

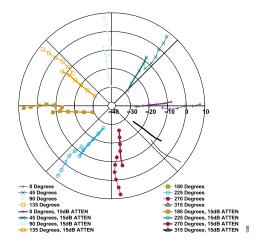

| Phase Adjustment Range                   | Over pridee countings and mequenoise | 360     |     | Degrees |

| Phase Resolution                         |                                      | 2.8     |     | Degrees |

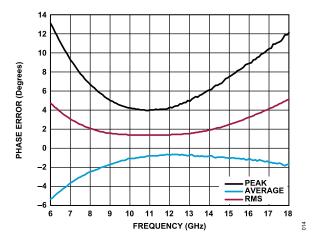

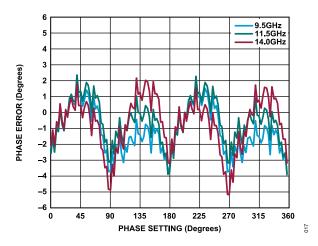

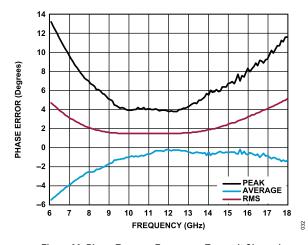

| RMS Phase Error                          | Over phase settings and frequencies  | 2       |     | Degrees |

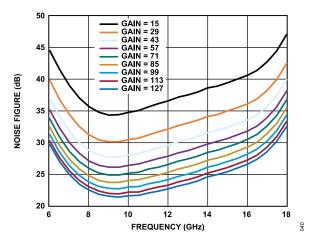

| Noise Figure                             | Maximum gain setting                 | _       |     | Dogroot |

| Nominal Bias Setting                     | Maximum gain coaling                 |         |     |         |

| 9.5 GHz                                  |                                      | 22      |     | dB      |

| 11.5 GHz                                 |                                      | 23      |     | dB      |

| 14 GHz                                   |                                      | 25      |     | dB      |

| Low Bias Setting                         |                                      | 25      |     | uD      |

| 9.5 GHz                                  |                                      | 22      |     | dB      |

| 11.5 GHz                                 |                                      | 23      |     | dB      |

| 11.0 0112                                |                                      | 20      |     | uD      |

analog.com Rev. B | 5 of 79

# **SPECIFICATIONS**

Table 1.

| Parameter                                 | Test Conditions/Comments                                                                              | Min Typ    | Max Unit |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------|------------|----------|

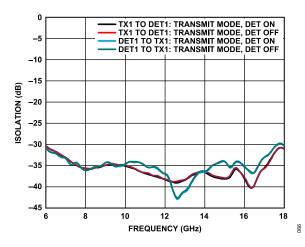

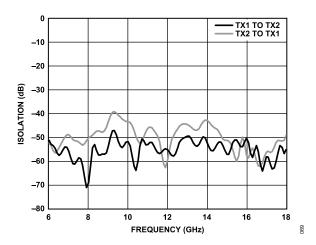

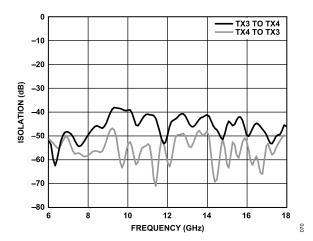

| Channel to Channel Isolation <sup>2</sup> |                                                                                                       | -40        | dB       |

| Transmit Output to RF_IO                  | Maximum gain setting, 9.5 GHz                                                                         | -60        | dB       |

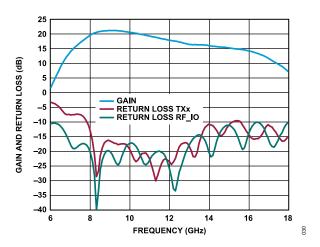

| Output Return Loss                        | TX1, TX2, TX3, or TX4 pin                                                                             | -10        | dB       |

| Input Return Loss                         | RF_IO pin                                                                                             | -12        | dB       |

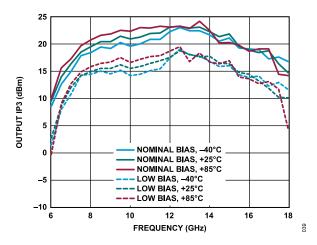

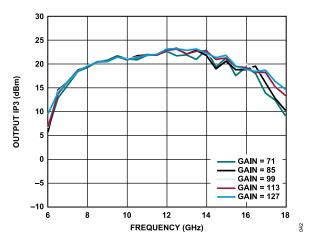

| Output Third-Order Intercept (IP3)        | Maximum gain setting, 1 MHz carrier spacing                                                           |            |          |

| Nominal Bias Setting                      |                                                                                                       |            |          |

| 9.5 GHz                                   |                                                                                                       | 20         | dBm      |

| 11.5 GHz                                  |                                                                                                       | 21         | dBm      |

| 14 GHz                                    |                                                                                                       | 22         | dBm      |

| Low Bias Setting                          |                                                                                                       |            | abiii    |

| 9.5 GHz                                   |                                                                                                       | 15         | dBm      |

| 11.5 GHz                                  |                                                                                                       | 16         | dBm      |

| 14 GHz                                    |                                                                                                       | 16         | dBm      |

|                                           |                                                                                                       | 10         | UDIII    |

| RECEIVE SECTION                           | Manada a I kina a a Kina                                                                              |            |          |

| Maximum Single Channel Gain <sup>3</sup>  | Nominal bias setting                                                                                  | 40         |          |

| 9.5 GHz                                   |                                                                                                       | 10         | dB       |

| 11.5 GHz                                  |                                                                                                       | 9          | dB       |

| 14 GHz                                    |                                                                                                       | 7          | dB       |

| Maximum Electronic Gain <sup>4</sup>      | Nominal bias setting                                                                                  |            |          |

| 9.5 GHz                                   |                                                                                                       | 16         | dB       |

| 11.5 GHz                                  |                                                                                                       | 15         | dB       |

| 14 GHz                                    |                                                                                                       | 13         | dB       |

| Maximum Coherent Gain <sup>5</sup>        | Nominal bias setting                                                                                  |            |          |

| 9.5 GHz                                   |                                                                                                       | 22         | dB       |

| 11.5 GHz                                  |                                                                                                       | 21         | dB       |

| 14 GHz                                    |                                                                                                       | 19         | dB       |

| Gain Flatness                             | Across any 1 GHz bandwidth                                                                            |            |          |

|                                           | From 9 GHz to 14 GHz                                                                                  | ±1.0       | dB       |

|                                           | From 8 GHz to 15 GHz                                                                                  | ±1.7       | dB       |

| Gain Variation vs. Temperature            | 11.5 GHz                                                                                              | ±3         | dB       |

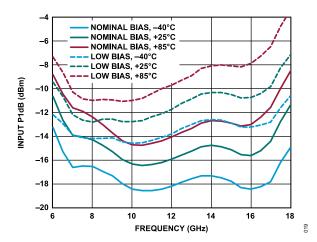

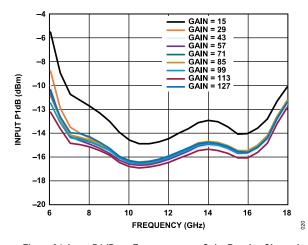

| Input P1dB                                | Unmeasured paths enabled and terminated with                                                          |            | 45       |

| input 145                                 | 50 Ω                                                                                                  |            |          |

| Nominal Bias Setting                      |                                                                                                       |            |          |

| 9.5 GHz                                   |                                                                                                       | -16        | dBm      |

| 11.5 GHz                                  |                                                                                                       | -16        | dBm      |

| 14 GHz                                    |                                                                                                       | -15        | dBm      |

| Low Bias Setting                          |                                                                                                       | 10         | d Dill   |

| 9.5 GHz                                   |                                                                                                       | -13        | dBm      |

| 11.5 GHz                                  |                                                                                                       | -12        | dBm      |

| 14 GHz                                    |                                                                                                       | -12<br>-10 | dBm      |

|                                           | Maximum gain cotting corrier appains 4 MUz.                                                           | -10        | UDIII    |

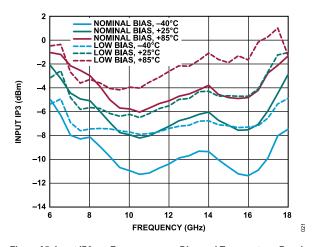

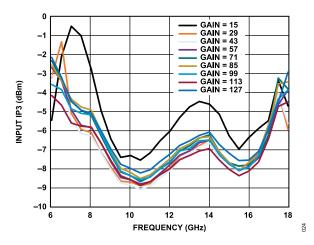

| Input IP3                                 | Maximum gain setting, carrier spacing 1 MHz; unmeasured paths enabled and terminated with 50 $\Omega$ |            |          |

| Nominal Bias Setting                      |                                                                                                       |            |          |

| 9.5 GHz                                   |                                                                                                       | <b>-</b> 7 | dBm      |

| 11.5 GHz                                  |                                                                                                       | -7         | dBm      |

| 14 GHz                                    |                                                                                                       | <b>-</b> 6 | dBm      |

| Low Bias Setting                          |                                                                                                       | U          | UDIII    |

| 9.5 GHz                                   |                                                                                                       | <b>-</b> 7 | dBm      |

analog.com Rev. B | 6 of 79

# **SPECIFICATIONS**

Table 1.

| Parameter                                                 | Test Conditions/Comments                                                                                     | Min  | Тур Мах | Unit    |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|---------|---------|

| 11.5 GHz                                                  |                                                                                                              | -6   |         | dBm     |

| 14 GHz                                                    |                                                                                                              | -5   |         | dBm     |

| Gain Adjustment Range                                     | Variable gain amplifier (VGA) and step attenuator                                                            | ≥31  |         | dB      |

| Gain Resolution                                           |                                                                                                              | ≤0.5 |         | dB      |

| RMS Gain Error                                            |                                                                                                              | 0.2  |         | dB      |

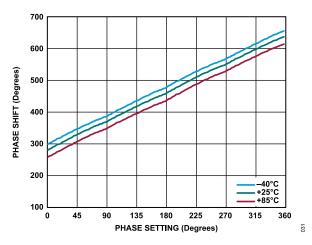

| Phase Adjustment Range                                    |                                                                                                              | 360  |         | Degrees |

| Phase Resolution                                          |                                                                                                              | 2.8  |         | Degrees |

| RMS Phase Error                                           |                                                                                                              | 2    |         | Degrees |

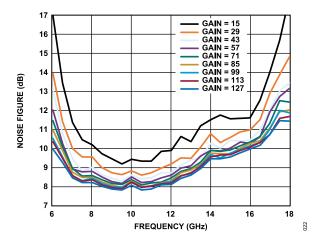

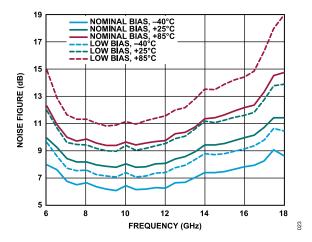

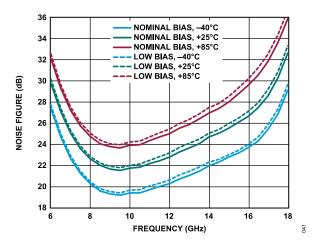

| Noise Figure                                              | Maximum gain setting; unmeasured paths disabled and terminated with 50 $\Omega$                              |      |         |         |

| Nominal Bias Setting                                      |                                                                                                              |      |         |         |

| 9.5 GHz                                                   |                                                                                                              | 8    |         | dB      |

| 11.5 GHz                                                  |                                                                                                              | 8    |         | dB      |

| 14 GHz                                                    |                                                                                                              | 9    |         | dB      |

| Low Bias Setting                                          |                                                                                                              |      |         |         |

| 9.5 GHz                                                   |                                                                                                              | 9    |         | dB      |

| 11.5 GHz                                                  |                                                                                                              | 10   |         | dB      |

| 14 GHz                                                    |                                                                                                              | 11   |         | dB      |

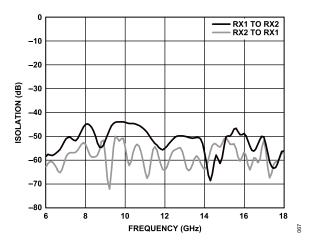

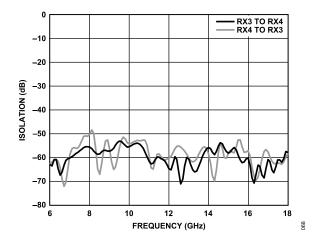

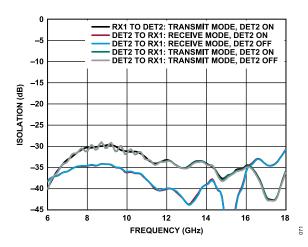

| Channel to Channel Isolation <sup>6</sup>                 |                                                                                                              | 40   |         | dB      |

| RF IO to Receive Isolation                                |                                                                                                              | 60   |         | dB      |

| Input Return Loss                                         |                                                                                                              | -10  |         | dB      |

| Output Return Loss                                        | RF_IO pin                                                                                                    | -12  |         | dB      |

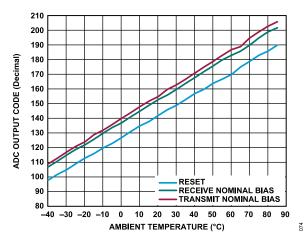

| FEMPERATURE SENSOR                                        | Τα _10 μπ                                                                                                    | 12   |         | ub      |

| Range                                                     |                                                                                                              | -40  | +85     | °C      |

| Slope                                                     |                                                                                                              | 0.8  | 100     | LSB/°C  |

| Nominal Analog-to-Digital Converter (ADC)                 | Power-on reset (POR) mode (transmit and                                                                      | 145  |         | Decimal |

| Output                                                    | receive not enabled), T <sub>A</sub> = 25°C                                                                  | 140  |         | Decimal |

| Resolution                                                |                                                                                                              | 8    |         | Bits    |

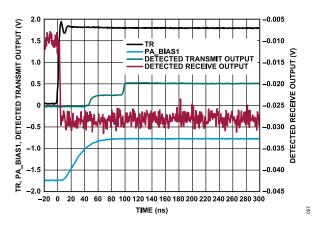

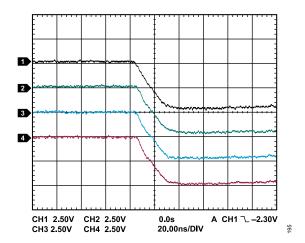

| FRANSMIT AND RECEIVE SWITCHING                            | TX_LOAD, RX_LOAD, and TR pins                                                                                |      |         |         |

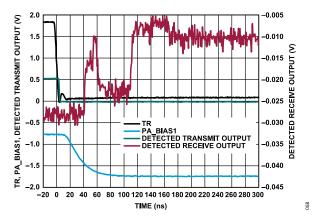

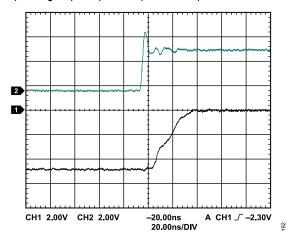

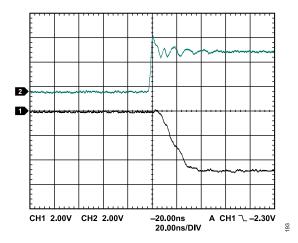

| Transmit and Receive Switching Time                       | From rising/falling edge of TR at 50% to RF at 90%                                                           | 180  |         | ns      |

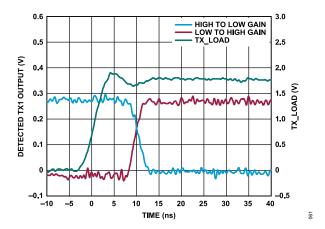

| Phase and Gain Switching Time                             | From rising edge of TX_LOAD or RX_LOAD at 50% to RF at 90%                                                   | 20   |         | ns      |

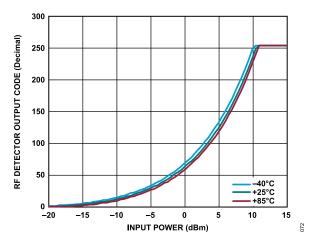

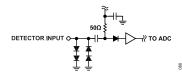

| POWER DETECTOR                                            | DET1, DET2, DET3, and DET4 pins                                                                              |      |         |         |

| RF Input Power Range                                      | 11.5 GHz                                                                                                     | -20  | +10     | dBm     |

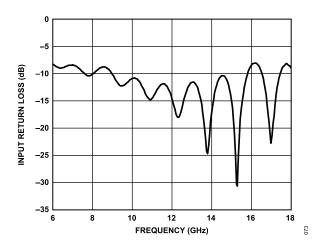

| Input Return Loss                                         |                                                                                                              | -10  |         | dB      |

| Nominal ADC Output Code                                   | Input power (P <sub>IN</sub> ) = 0 dBm, 11.5 GHz                                                             | 60   |         | Decimal |

| Resolution                                                |                                                                                                              | 8    |         | Bits    |

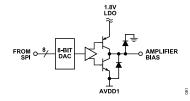

| POWER AMPLIFIER (PA) DIGITAL-TO-ANALOG<br>CONVERTER (DAC) | PA_BIAS1, PA_BIAS2, PA_BIAS3, and PA_BIAS4 pins                                                              |      |         |         |

| Resolution                                                | ·                                                                                                            | 8    |         | Bits    |

| Voltage Range                                             |                                                                                                              | -4.8 | to 0    | V       |

| Source and Sink Current                                   |                                                                                                              |      | to +10  | mA      |

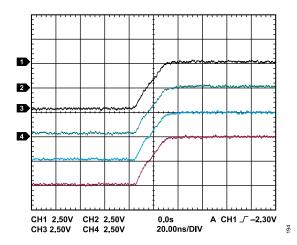

| Off to On Switching Time                                  | From TR or CSB at 50% to V <sub>OUT</sub> at 90%, V <sub>OUT</sub> from -1 V to -2 V, 1 nF C <sub>LOAD</sub> | 60   |         | ns      |

| On to Off Switching Time                                  | From TR or CSB at 50% to V <sub>OUT</sub> at 10%, V <sub>OUT</sub> from -1 V to -2 V, 1 nF C <sub>LOAD</sub> | 60   |         | ns      |

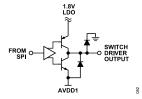

| LOW NOISE AMPLIFIER (LNA) DAC                             | LNA_BIAS pin                                                                                                 |      |         |         |

| Resolution                                                |                                                                                                              | 8    |         | Bits    |

analog.com Rev. B | 7 of 79

# **SPECIFICATIONS**

Table 1.

| Parameter                                                         | Test Conditions/Comments                                                                      | Min   | Тур        | Max   | Unit |

|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|------------|-------|------|

| Voltage Range                                                     |                                                                                               |       | -4.8 to 0  |       | V    |

| Source and Sink Current                                           |                                                                                               |       | -10 to+10  |       | mA   |

| Off to On Switching Time                                          | From TR or CSB at 50% to $V_{OUT}$ at 90%, $V_{OUT}$ from $-2$ V to $-1$ V, $1$ nF $C_{LOAD}$ |       | 60         |       | ns   |

| On to Off Switching Time                                          | From TR or CSB at 50% to $V_{OUT}$ at 10%, $V_{OUT}$ from -1 V to -2 V, 1 nF $C_{LOAD}$       |       | 60         |       | ns   |

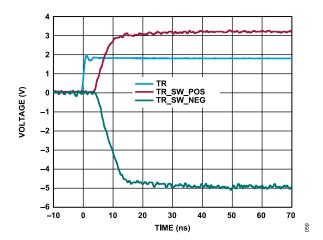

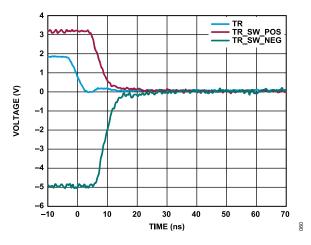

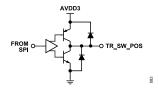

| TRANSMIT AND RECEIVE MODULE CONTROL                               | TR_SW_POS, TR_SW_NEG, TR_POL pins                                                             |       |            |       |      |

| Voltage Range                                                     | TR_SW_NEG, TR_POL                                                                             |       | -4.8 to 0  |       | V    |

|                                                                   | TR_SW_POS                                                                                     |       | 0 to 3.2   |       | V    |

| Off to On Switching Time                                          | From TR or CSB at 50% to V <sub>OUT</sub> at 90%                                              |       | 15         |       | ns   |

| On to Off Switching Time                                          | From TR or CSB at 50% to V <sub>OUT</sub> at 10%                                              |       | 15         |       | ns   |

| LOGIC INPUTS <sup>7</sup>                                         | TR, RX_LOAD, TX_LOAD, CSB, SCLK, and SDIO pins                                                |       |            |       |      |

| Input High Voltage (V <sub>IH</sub> )                             |                                                                                               | 1.0   |            |       | V    |

| Input Low Voltage (V <sub>IL</sub> )                              |                                                                                               |       |            | 0.4   | V    |

| High and Low Input Current (I <sub>INH</sub> , I <sub>INL</sub> ) |                                                                                               |       | ±1         |       | μA   |

| Input Capacitance (C <sub>IN</sub> )                              |                                                                                               |       | 1          |       | pF   |

| LOGIC OUTPUTS                                                     | SDO and SDIO pins                                                                             |       |            |       |      |

| Output High Voltage (V <sub>OH</sub> )                            | Output high current (I <sub>OH</sub> ) = 0 mA (open circuit)                                  |       | 1.8        |       | V    |

| Output Low Voltage (V <sub>OL</sub> )                             | Output low current (I <sub>OL</sub> ) = 0 mA (open circuit)                                   |       | 0          |       | V    |

| Output High Voltage (V <sub>OH</sub> )                            | Output high current (I <sub>OH</sub> ) = −10 mA                                               | 1.4   |            |       | V    |

| Output Low Voltage (V <sub>OL</sub> )                             | Output low current (I <sub>OL</sub> ) = 10 mA                                                 |       |            | 0.4   | V    |

| POWER SUPPLIES                                                    |                                                                                               |       |            |       |      |

| AVDD1                                                             |                                                                                               | -5.25 | <b>-</b> 5 | -4.75 | V    |

| AVDD3                                                             |                                                                                               | 3.1   | 3.3        | 3.5   | V    |

| I <sub>AVDD1</sub>                                                | Quiescent (reset state)                                                                       |       | -4         |       | mA   |

| I <sub>AVDD1</sub>                                                | PA bias outputs fully loaded                                                                  |       | -50        |       | mA   |

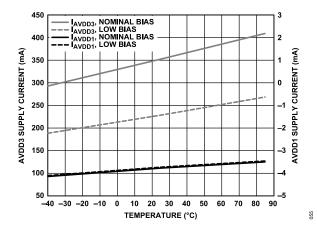

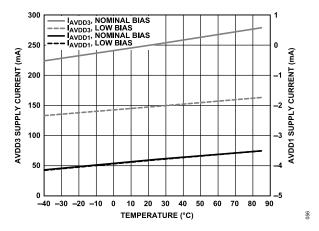

| I <sub>AVDD3</sub>                                                |                                                                                               |       |            |       |      |

| Reset Mode (Standby)                                              |                                                                                               |       | 23         |       | mA   |

| Transmit Mode                                                     | Four channels enabled, nominal bias                                                           |       | 350        |       | mA   |

|                                                                   | Four channels enabled, low bias setting                                                       |       | 240        |       | mA   |

| Receive Mode                                                      | Four channels enabled, nominal bias                                                           |       | 260        |       | mA   |

|                                                                   | Four channels enabled, low bias setting                                                       |       | 160        |       | mA   |

<sup>&</sup>lt;sup>1</sup> Single channel transmit gain defined as the ratio of output power at any Tx output port to the input power applied to the RF\_IO port.

### **TIMING SPECIFICATIONS**

AVDD1 = -5 V, AVDD3 = +3.3 V,  $T_A = 25$ °C, unless otherwise noted.

analog.com Rev. B | 8 of 79

<sup>&</sup>lt;sup>2</sup> From one transmit channel port to another, both channels must be set to the maximum gain.

<sup>&</sup>lt;sup>3</sup> Single channel receive gain is the ratio of the output power at RF\_IO to the input power applied to any single receive port, with the other three receive ports terminated in 50 Ω.

<sup>&</sup>lt;sup>4</sup> Electronic gain is the ratio of the output power at RF\_IO to the input power applied to any single receive port, with the other three receive ports driven and phased for coherent combining with 6 dB subtracted. The electronic gain is approximately 6 dB higher than the single path gain, and 6 dB lower than coherent gain.

<sup>&</sup>lt;sup>5</sup> Coherent gain is the ratio of output power at RF\_IO to the input power applied to any single receive port, with the other three receive ports driven and phased for coherent combining.

<sup>&</sup>lt;sup>6</sup> From one receive channel port to another, both channels must be set to the maximum gain.

<sup>&</sup>lt;sup>7</sup> Inputs have 100 mV (typical) of hysteresis.

# **SPECIFICATIONS**

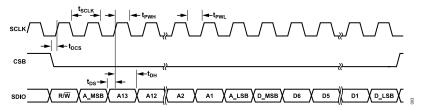

Table 2. SPI Timing

| Parameter                                                 | Min | Тур | Max | Unit | Test Conditions/Comments              |

|-----------------------------------------------------------|-----|-----|-----|------|---------------------------------------|

| Maximum Clock Rate (t <sub>SCLK</sub> )                   |     | 25  |     | MHz  |                                       |

| Minimum Clock Period (1/t <sub>SCLK</sub> ) <sup>1</sup>  |     | 40  |     | ns   |                                       |

| Minimum Pulse Width High (t <sub>PWH</sub> ) <sup>1</sup> |     | 10  |     | ns   |                                       |

| Minimum Pulse Width Low (t <sub>PWL</sub> ) <sup>1</sup>  |     | 10  |     | ns   |                                       |

| Setup Time, SDIO to SCLK (t <sub>DS</sub> )               |     | 5   |     | ns   |                                       |

| Hold Time, SDIO to SCLK (t <sub>DH</sub> )                |     | 5   |     | ns   |                                       |

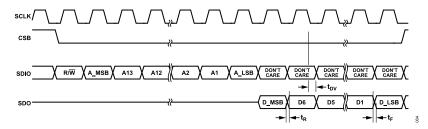

| Data Valid, SDO to SCLK (t <sub>DV</sub> )                |     | 5   |     | ns   |                                       |

| Setup Time, CSB to SCLK (t <sub>DCS</sub> )               |     | 10  |     | ns   |                                       |

| SDIO, SDO Rise Time (t <sub>R</sub> )                     |     | 4   |     | ns   | Outputs loaded with 80 pF, 10% to 90% |

| SDIO, SDO Fall Time (t <sub>F</sub> )                     |     | 4   |     | ns   | Outputs loaded with 80 pF, 10% to 90% |

<sup>1</sup> Clock Period = (Pulse Width High) + (Pulse Width Low); but (Minimum Clock Period) = (Minimum Pulse Width High) + (Minimum Pulse Width Low). The clock period allows SPI signals that are not 50% duty cycle. I Minimum Pulse Width High = 10 ns, then Minimum Pulse Width Low = 30 ns, or vice versa.

# **Timing Diagrams**

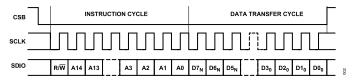

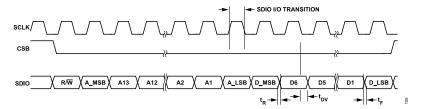

The standard Analog Devices, Inc., SPI transaction is 24 bits in length, although longer SPI transactions are possible. Figure 2 shows a generalized SPI transaction, that is either 24 bits or more (in additional 8-bit increments). See the SPI Block Write Mode section for more details on longer than 24-bit SPI transactions. All timing diagrams show MSB clocked in first. In a 24-bit SPI transaction, the data is latched into the ADAR1000 on the SCLK rising edge of the last data bit clocked in (D\_LSB).

Figure 2. Serial Port Interface Register Timing (MSB First)

Figure 3. Timing Diagram for 4-Wire or 3-Wire Serial Port Interface Register Write

Figure 4. Timing Diagram for 4-Wire Serial Port Interface Register Read

analog.com Rev. B | 9 of 79

### **SPECIFICATIONS**

Figure 5. Timing Diagram for 3-Wire Serial Port Interface Register Read

Note that in 3-wire mode, the SDIO pin becomes an output pin after receiving the instruction address header with a readback request. In this mode, the SDIO must be changed from an input to an output in the ½ cycle of SCLK between the last rising edge of SCLK of the instruction and the following falling edge.

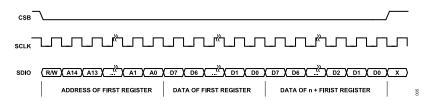

#### **SPI Block Write Mode**

Data can be written to the SPI registers in a block write mode, where the register address automatically increments, and data for consecutive registers can be written without sending new address bits. Data writing can be continued indefinitely until CSB is raised again, ending the write process. Data for each register is latched into the ADAR1000 on the SCLK rising edge of the last data bit, which is shown as D0 in Figure 6.

Figure 6. Timing Diagram for Block Write Mode

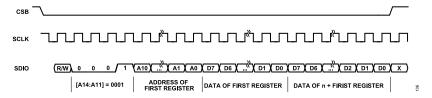

## SPI Write/Read All Mode

Data can be written to the SPI registers in a write all mode, where the data is written to all chips connected to the SPI bus with a single write command, regardless of the ADDR1 and ADDR0 values, by setting address Bits[A14:A11] = 0001. The write all mode allows the user to broadcast the same data, to all ADAR1000 devices sharing the SPI bus, with a single SPI write. If the user has dedicated SDO lines on the PCB, data can be simultaneously read from the SPI registers from several ADAR1000 devices in the read all mode. This mode is initiated by setting Bits[A14:A11] = 0001, and setting the R/W bit = 1 for a read all. Note that this write or read all capability is only applicable to the registers, and not applicable to the random access memory (RAM) space. The RAM space is accessed when Bit 12 = 1. The user must consider the chip ID bits, Bits[14:13], when writing data to the RAM.

Figure 7. SPI Write All Instruction and Timing Diagram

analog.com Rev. B | 10 of 79

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                              | Rating          |

|----------------------------------------|-----------------|

| AVDD1 to GND                           | −5.5 V          |

| AVDD3 to GND                           | 3.6 V           |

| Digital Input/Output Voltage to GND    | 2.0 V           |

| Maximum RF Input Power <sup>1</sup>    | 20 dBm          |

| Operating Temperature Range            | -40°C to +85°C  |

| Storage Temperature Range              | -65°C to +150°C |

| Reflow Soldering                       |                 |

| Peak Temperature                       | 260°C           |

| Junction Temperature (T <sub>J</sub> ) | 135°C           |

| Electrostatic Discharge (ESD)          |                 |

| Charged Device Model (CDM)             | ±500 V          |

| Human Body Model (HBM)                 | ±2500 V         |

<sup>&</sup>lt;sup>1</sup> Applicable to any receive or transmit input.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. The PCB thermal design requires careful attention.

$\theta_{JA}$  is the junction to the ambient with the exposed pad soldered down,  $\theta_{JC\text{-}TOP}$  is the junction to the top of the package, and  $\theta_{JC\text{-}BOTTOM}$  is the junction to the exposed pad on the bottom of the package.

Table 4. Thermal Resistance

| Package Type         | $\theta_{JA}$ | $\theta_{\text{JC-TOP}}$ | $\theta_{\text{JC-BOTTOM}}$ | Unit |

|----------------------|---------------|--------------------------|-----------------------------|------|

| CC-88-1 <sup>1</sup> | 18.7          | 9.7 <sup>2</sup>         | 10.1                        | °C/W |

<sup>&</sup>lt;sup>1</sup> Simulated based on PCB specified in JESD-51.

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

analog.com Rev. B | 11 of 79

Simulated with cold plate attached on top of the package using 100 µm of thermal interface material (3.6 W/mK).

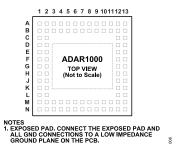

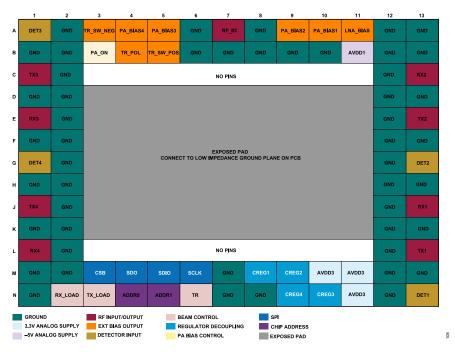

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 8. Pin Configuration (Top View)

Figure 9. Pin Configuration, Color Coded (Top View)

Table 5. Pin Function Descriptions

| Pin No.                                                                                                                                                                                                       | Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

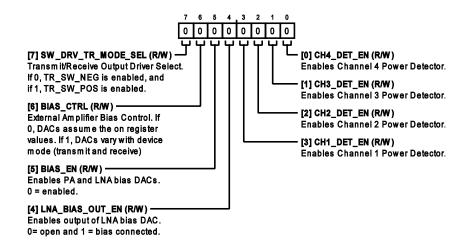

| A1                                                                                                                                                                                                            | DET3      | Channel 3 Power Detector Input. DET3 is internally ac-coupled and enabled by Register 0x030, Bit 1. The nominal operating input power range is $-20$ dBm to $+10$ dBm. If this pin is unused, it is recommended to leave the detector disabled and either provide a 50 $\Omega$ termination or ground the input.                                                |

| A2, A6, A8, A12, A13, B1, B2, B6 to B10, B12, B13, C2, C12, D1, D2, D12, D13, E2, E12, F1, F2, F12, F13, G2, G12, H1, H2, H12, H13, J2, J12, K1, K2, K12, K13, L2, L12, M1, M2, M7, M12, M13, N1, N7, N8, N12 | GND       | RF Ground. Tie all ground pins together to a low impedance plane on the PCB board.                                                                                                                                                                                                                                                                              |

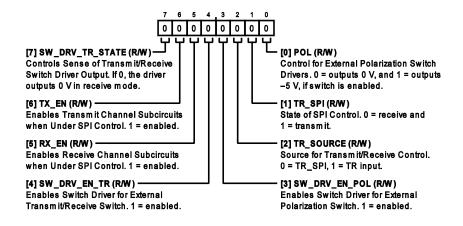

| A3                                                                                                                                                                                                            | TR_SW_NEG | Gate Control Output for External Transmit and Receive Switch (0 V or -5 V). Pin is floating upon power up or after a soft reset.                                                                                                                                                                                                                                |

| A4                                                                                                                                                                                                            | PA_BIAS4  | Gate Bias Output for Channel 4 External PA. Output ranges from 0 to -4.8 V, controlled by a combination of the PA_ON pin, Register 0x02C (CH4_PA_BIAS_ON value), and Register 0x049 (CH4_PA_BIAS_OFF value). Output is set to the CH4_PA_BIAS_OFF value if the PA_ON pin is at logic low. Pin assumes CH4_PA_BIAS_ON default value upon power up or soft reset. |

| A5                                                                                                                                                                                                            | PA_BIAS3  | Gate Bias Output for Channel 3 External PA. Output ranges from 0 to -4.8 V, controlled by a combination of the PA_ON pin, Register 0x02B (CH3_PA_BIAS_ON value), and Register 0x048 (CH3_PA_BIAS_OFF value).                                                                                                                                                    |

analog.com Rev. B | 12 of 79

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 5. Pin Function Descriptions

| Pin No. | Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |           | Output is set to the CH3_PA_BIAS_OFF value if the PA_ON pin is at logic low. Pin assumes CH3_PA_BIAS_ON default value upon power up or soft reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

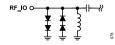

| A7      | RF_IO     | Common RF Pin for Input in Transmit Mode and Output in Receive Mode. The signal path is ac-coupled via an on-chip capacitor. The dc bias is 0 V due to the on-chip shunt inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| A9      | PA_BIAS2  | Gate Bias Output for Channel 2 External PA. Output ranges from 0 to -4.8 V, controlled by a combination of the PA_ON pin, Register 0x02A (CH2_PA_BIAS_ON value), and Register 0x047 (CH2_PA_BIAS_OFF value). Output is set to the CH2_PA_BIAS_OFF value if the PA_ON pin is at logic low. Pin assumes CH2_PA_BIAS_ON default value upon power up or soft reset.                                                                                                                                                                                                                                                                                                                                              |

| A10     | PA_BIAS1  | Gate Bias Output for Channel 1 External PA. Output ranges from 0 to -4.8 V, controlled by a combination of the PA_ON pin, Register 0x029 (CH1_PA_BIAS_ON value), and Register 0x046 (CH1_PA_BIAS_OFF value). Output is set to the CH1_PA_BIAS_OFF value if the PA_ON pin is at logic low. Pin assumes CH1_PA_BIAS_ON default value upon power up or soft reset.                                                                                                                                                                                                                                                                                                                                              |

| A11     | LNA_BIAS  | Gate Bias Output for External LNA. Output ranges from 0 to -4.8 V, controlled by a combination of Register 0x030 (Bit 4, LNA_BIAS_OUT_EN), Register 0x02D (LNA_BIAS_ON value), and Register 0x04A (LNA_BIAS_OFF value). Output floats if Register 0x030, Bit 4 is at logic low. Pin is floating upon power up or after a soft reset.                                                                                                                                                                                                                                                                                                                                                                         |

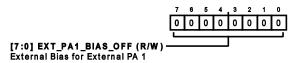

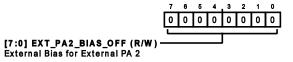

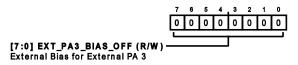

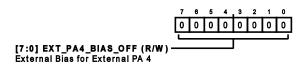

| B3      | PA_ON     | PA Enable Input. This pin is used when device transmit/receive operation is controlled via the TR pin. This pin is not used with SPI control. When BIAS_CTRL (Bit 6 in Register 0x30) = 1 and TR_SOURCE (Bit 2 in Register 0x31) = 1, set this pin to logic high for the PA bias voltage outputs to assume the values set by the EXT_PAx_BIAS_ON registers when the TR pin = 1, and EXT_PAx_BIAS_OFF registers when the TR pin = 0 (where x = 1 to 4). All PA bias voltage outputs assume the corresponding EXT_PAx_BIAS_OFF register values if the PA_ON pin is at logic low (see Table 16). This pin is internally pulled up to the 1.8 V low dropout (LDO) regulator bias voltage with a 100 kΩ resistor. |

| B4      | TR_POL    | Gate Control Output for External Polarization Switch (0 V or -5 V).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| B5      | TR_SW_POS | Gate Control Positive Output for External Transmit and Receive Switch (0 V or 3.3 V). Pin is floating upon power up or after a soft reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

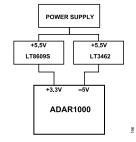

| B11     | AVDD1     | -5 V Power Supply. AVDD1 provides the negative currents for sinking the PA_BIASx and LNA_BIAS outputs. If the PA_BIASx and LNA_BIAS pins are not used, the user can connect AVDD1 to ground to reduce power consumption and to use a single voltage supply. It is recommended to power up the AVDD3 pins (3.3 V) before or at the same time as the AVDD1 pin (-5 V).                                                                                                                                                                                                                                                                                                                                         |

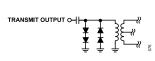

| C1      | TX3       | Channel 3 Output in Transmit Mode. This pin is ac-coupled via an on-chip balun and series capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

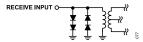

| C13     | RX2       | Channel 2 Input in Receive Mode. This pin is ac-coupled via an on-chip balun.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| E1      | RX3       | Channel 3 Input in Receive Mode. This pin is ac-coupled via an on-chip balun.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| E13     | TX2       | Channel 2 Output in Transmit Mode. This pin is ac-coupled via an on-chip balun and a series capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| G1      | DET4      | Channel 4 Power Detector Input. DET4 is internally ac-coupled and enabled by Register 0x030, Bit 0. The nominal operating input power range is $-20$ dBm to $+10$ dBm. If this pin is unused, it is recommended to leave the detector disabled and either provide a $50 \Omega$ termination or ground the input.                                                                                                                                                                                                                                                                                                                                                                                             |

| G13     | DET2      | Channel 2 Power Detector Input. DET2 is internally ac-coupled and enabled by Register 0x030, Bit 2. The nominal operating input power range is $-20$ dBm to +10 dBm. If this pin is unused, it is recommended to leave the detector disabled and either provide a 50 $\Omega$ termination or ground the input.                                                                                                                                                                                                                                                                                                                                                                                               |

| J1      | TX4       | Channel 4 Output in Transmit Mode. This pin is ac-coupled via an on-chip balun and a series capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| J13     | RX1       | Channel 1 Input in Receive Mode. This pin is ac-coupled via an on-chip balun.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| L1      | RX4       | Channel 4 Input in Receive Mode. This pin is ac-coupled via an on-chip balun.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| L13     | TX1       | Channel 1 Output in Transmit Mode. This pin is ac-coupled via an on-chip balun and a series capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| M3      | CSB       | SPI Chip Select Input (1.8 V CMOS Logic). Serial communication is enabled when CSB goes low. When CSB goes high, serial data is loaded into the register corresponding to the address in the instruction cycle (see Figure 2) in write mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| M4      | SDO       | SPI Serial Data Output (1.8 V CMOS Logic). Enabled when SDO ACTIVE Bit = 1. Used in 4-wire SPI protocol. Pin has a readback error when sharing a bus with other chips. See SDO Readback Problem and Solution.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| M5      | SDIO      | SPI Serial Data Input and Output (1.8 V CMOS Logic). 4-wire SPI protocol if SDO ACTIVE Bit = 1; 3-wire SPI protocol when SDO ACTIVE Bit = 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| M6      | SCLK      | SPI Serial Clock Input (1.8 V CMOS Logic). In write mode, data is sampled on the rising edge of SCLK. During a read cycle, output data changes at the falling edge of SCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

analog.com Rev. B | 13 of 79

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 5. Pin Function Descriptions

| Pin No.       | Mnemonic | Description                                                                                                                                                                                                                                                                                                        |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M8            | CREG1    | Decoupling Pin for 1.8 V LDO Reference. Connect a 1 µF capacitor through a low impedance path from this pin to a ground plane.                                                                                                                                                                                     |

| M9            | CREG2    | Decoupling Pin for 2.8 V LDO Output. Connect a 1 µF capacitor through a low impedance path from this pin to a ground plane.                                                                                                                                                                                        |

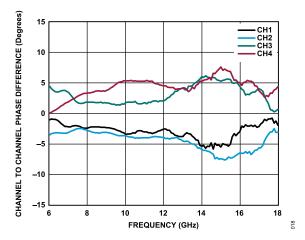

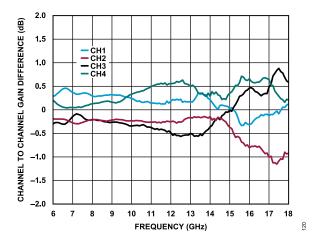

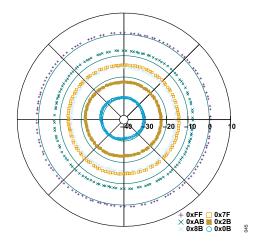

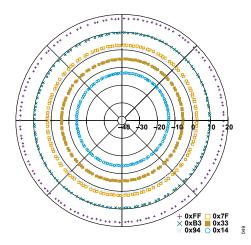

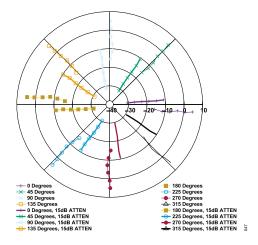

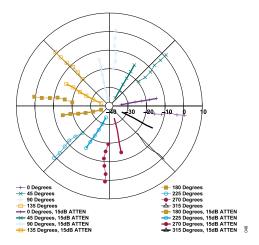

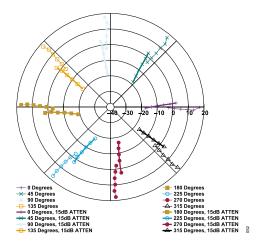

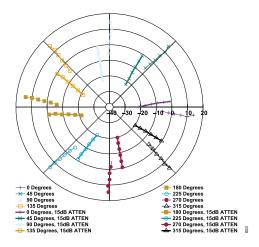

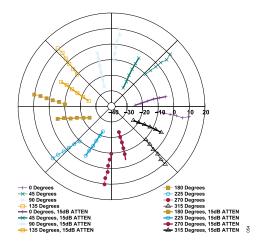

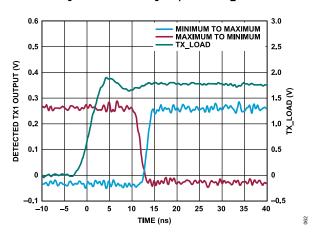

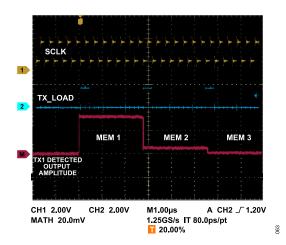

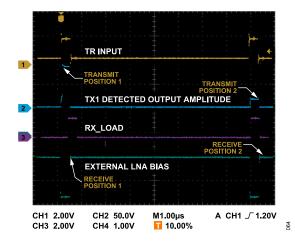

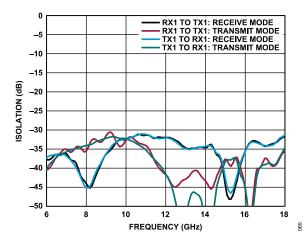

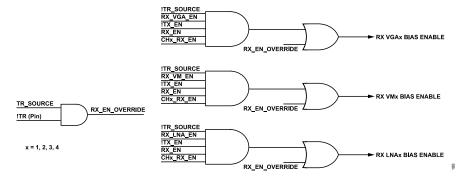

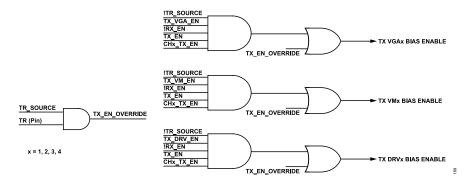

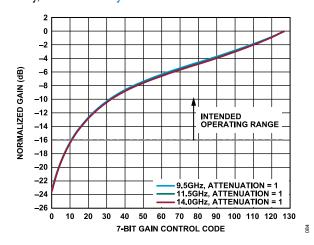

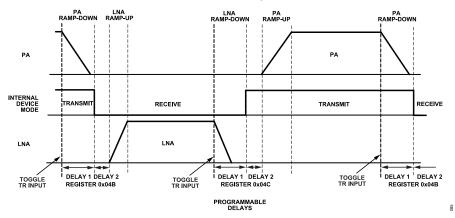

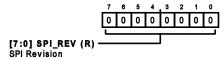

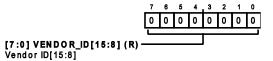

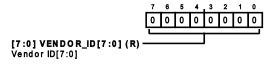

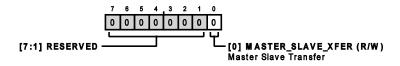

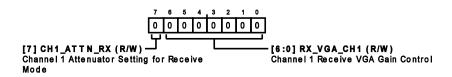

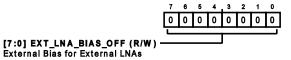

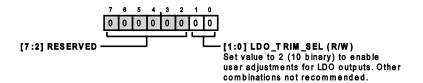

| M10, M11, N11 | AVDD3    | 3.3 V Voltage Power Supply Inputs. It is recommended to power-up these pins before or at the same time as the AVDD1 (-5 V) supply.                                                                                                                                                                                 |