# Low Cost, Triple **Video Amplifiers**

AD8073

#### **FEATURES**

**Very Low Cost** Good Video Specifications ( $R_1 = 150 \Omega$ ) Gain Flatness of 0.1 dB to 10 MHz 0.05% Differential Gain Error 0.1° Differential Phase Error Low Power

3.5 mA/Amplifier Supply Current Operates on Single 5 V to 12 V Supply **High Speed**

100 MHz, -3 dB Bandwidth (G = +2) 500 V/μs Slew Rate

Fast Settling Time of 25 ns (0.1%)

Easy to Use

30 mA Output Current

Output Swing to 1.3 V of Rails on Single 5 V Supply

## **APPLICATIONS**

Video Line Driver **Computer Video Plug-In Boards RGB or S-Video Amplifier in Component Systems**

## PRODUCT DESCRIPTION

The AD8072 (dual) and AD8073 (triple) are low cost, current feedback amplifiers intended for high volume, cost sensitive applications. In addition to being low cost, these amplifiers deliver solid video performance into a 150  $\Omega$  load while consuming only 3.5 mA per amplifier of supply current. Furthermore, the AD8073 is three amplifiers in a single 14-lead narrow-body SOIC package. This makes it ideal for applications where small size is essential. Each amplifier's inputs and output are accessible providing added gain setting flexibility.

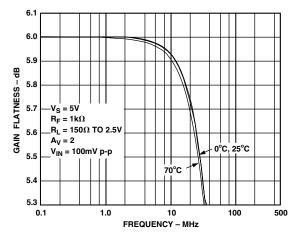

These devices provide 30 mA of output current per amplifier, and are optimized for driving one back terminated video load  $(150 \Omega)$  each. These current feedback amplifiers feature gain flatness of 0.1 dB to 10 MHz while offering differential gain and phase error of 0.05% and 0.1°. This makes the AD8072 and AD8073 ideal for business and consumer video electronics.

Both will operate from a single 5 V to 12 V power supply. The outputs of each amplifier swing to within 1.3 volts of either supply rail to accommodate video signals on a single 5 V supply.

The high bandwidth of 100 MHz, 500 V/µs of slew rate, along with settling to 0.1% in 25 ns, make the AD8072 and AD8073 useful in many general purpose, high speed applications where a single 5 V or dual power supplies up to  $\pm 6$  V are needed. The AD8072 is available in 8-lead plastic DIP, SOIC, and µSOIC packages while the AD8073 is available in 14-lead plastic DIP and SOIC packages. Both operate over the commercial temperature range of 0°C to 70°C. Additionally, the AD8072ARM operates over the industrial temperature range of -40°C to +85°C.

## REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

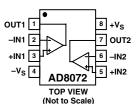

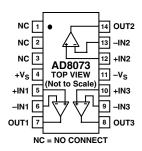

## PIN CONFIGURATIONS

8-Lead Plastic (N), SOIC (R), and µSOIC (RM) Packages

14-Lead Plastic (N), and SOIC (R) Packages

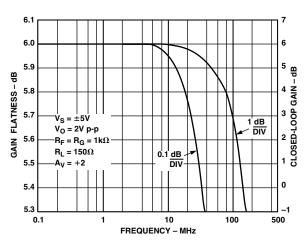

Figure 1. Large Signal Frequency Response

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2002

# AD8073—SPECIFICATIONS

## **ELECTRICAL CHARACTERISTICS** (@ $T_A = 25^{\circ}C$ , $V_S = \pm 5$ V, $R_L = 150~\Omega$ , unless otherwise noted.)

|                                                                                                                                          |                                                                                                                                       |           |                               | AD8072/AD8073 |                                        |  |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------|---------------|----------------------------------------|--|

| Parameter                                                                                                                                | Conditions                                                                                                                            | Min       | Typ                           | Max           | Unit                                   |  |

| DYNAMIC PERFORMANCE  -3 dB Bandwidth, Small Signal 0.1 dB Bandwidth, Small Signal Slew Rate Settling Time to 0.1%                        | $R_F = 1 \text{ k}\Omega$<br>No Peaking, $G = +2$<br>No Peaking, $G = +2$<br>$V_O = 4 \text{ V Step}$<br>$V_O = 2 \text{ V Step}$     | 80<br>8   | 100<br>10<br>500<br>25        |               | MHz<br>MHz<br>V/µs<br>ns               |  |

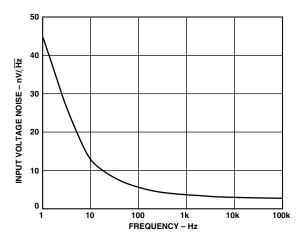

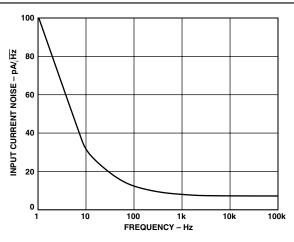

| DISTORTION/NOISE PERFORMANCE Differential Gain Differential Phase Crosstalk Input Voltage Noise Input Current Noise                      | $R_{\rm F} = 1 \; {\rm k}\Omega$ f = 3.58 MHz, G = +2 f = 3.58 MHz, G = +2 f = 5 MHz f = 10 kHz f = 10 kHz ( $\pm {\rm I}_{\rm IN}$ ) |           | 0.05<br>0.1<br>60<br>3<br>6   | 0.15<br>0.3   | % Degrees dB nV/√Hz pA/√Hz             |  |

| DC PERFORMANCE Transimpedance Input Offset Voltage  Offset Drift Input Bias Current (±) Input Bias Current Drift (±)                     | $ m T_{MIN}$ to $ m T_{MAX}$                                                                                                          |           | 0.3<br>2<br>11<br>4<br>12     | 6<br>8<br>12  | MΩ<br>mV<br>mV<br>μV/°C<br>μA<br>nA/°C |  |

| INPUT CHARACTERISTICS  -Input Resistance +Input Resistance Input Capacitance Common-Mode Rejection Ratio Input Common-Mode Voltage Range | $V_{CM} = -3.8 \text{ V to } +3.8 \text{ V}$                                                                                          |           | 120<br>1<br>1.6<br>56<br>±3.8 |               | Ω<br>MΩ<br>pF<br>dB<br>V               |  |

| OUTPUT CHARACTERISTICS +Output Voltage Swing -Output Voltage Swing Output Current Short Circuit Current                                  | $R_L = 10 \Omega$                                                                                                                     | 3<br>2.25 | 3.3<br>3<br>30<br>80          |               | V<br>V<br>mA<br>mA                     |  |

| POWER SUPPLY Operating Range Power Supply Rejection Ratio Quiescent Current per Amplifier                                                | $V_S = \pm 4 \text{ V to } \pm 6 \text{ V}$                                                                                           |           | ±2.5 to ±6<br>70<br>3.5       | 5             | V<br>dB<br>mA                          |  |

| OPERATING TEMPERATURE RANGE                                                                                                              |                                                                                                                                       | 0         |                               | 70            | °C                                     |  |

Specifications subject to change without notice.

## **ELECTRICAL CHARACTERISTICS** (@ $T_A = 25^{\circ}C$ , $V_S = 5$ V, $R_L = 150$ $\Omega$ to 2.5 V, unless otherwise noted.)

|                                                                                                                                          |                                                                                                                                                                                                                             | AD                       | 8072/AD8073                          |              |                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------|--------------|-------------------------------------------------------------------|

| Parameter                                                                                                                                | Conditions                                                                                                                                                                                                                  | Min                      | Typ                                  | Max          | Unit                                                              |

| DYNAMIC PERFORMANCE  -3 dB Bandwidth, Small Signal 0.1 dB Bandwidth, Small Signal Slew Rate Settling Time to 0.1%                        | $R_F = 1 \text{ k}\Omega$<br>No Peaking, $G = +2$<br>No Peaking, $G = +2$<br>$V_O = 2 \text{ V Step}$<br>$V_O = 2 \text{ V Step}$                                                                                           | 78<br>7.8                | 100<br>10<br>350<br>25               |              | MHz<br>MHz<br>V/µs<br>ns                                          |

| DISTORTION/NOISE PERFORMANCE Differential Gain Differential Phase Crosstalk Input Voltage Noise Input Current Noise                      | $\begin{array}{c} R_F = 1 \; k\Omega \\ f = 3.58 \; MHz,  G = +2,  R_L \; to \; 1.5 \; V \\ f = 3.58 \; MHz,  G = +2,  R_L \; to \; 1.5 \; V \\ f = 5 \; MHz \\ f = 10 \; kHz \\ f = 10 \; kHz \; (\pm I_{IN}) \end{array}$ |                          | 0.1<br>0.1<br>60<br>3<br>6           |              | % Degrees dB $nV/\sqrt{\overline{Hz}}$ $pA/\sqrt{\overline{Hz}}$  |

| DC PERFORMANCE Transimpedance Input Offset Voltage  Offset Drift Input Bias Current (±) Input Bias Current Drift (±)                     | $ m T_{MIN}$ to $ m T_{MAX}$                                                                                                                                                                                                |                          | 0.25<br>1.5<br>9<br>3<br>10          | 4<br>6<br>10 | MΩ<br>mV<br>mV<br>μV/°C<br>μA<br>nA/°C                            |

| INPUT CHARACTERISTICS  -Input Resistance +Input Resistance Input Capacitance Common-Mode Rejection Ratio Input Common-Mode Voltage Range | $V_{CM} = 1.2 \text{ V to } 3.8 \text{ V}$                                                                                                                                                                                  |                          | 120<br>1<br>1.6<br>54<br>1.2 to 3.8  |              | $\begin{array}{c} \Omega \\ M\Omega \\ pF \\ dB \\ V \end{array}$ |

| OUTPUT CHARACTERISTICS Output Voltage Swing Output Voltage Swing Output Current Short Circuit Current                                    | $R_{L} = 150 \ \Omega$ $R_{L} = 1 \ k\Omega \ T_{MIN} \ to \ T_{MAX}$ $R_{L} = 10 \ \Omega$                                                                                                                                 | 1.5 to 3.5<br>1.3 to 3.7 | 1.3 to 3.7<br>1.1 to 3.9<br>20<br>60 |              | V<br>V<br>mA<br>mA                                                |

| POWER SUPPLY Operating Range Power Supply Rejection Ratio Quiescent Current per Amplifier                                                | V <sub>S</sub> = 4 V to 6 V                                                                                                                                                                                                 |                          | ±2.5 to ±6 64 3                      | 4.5          | V<br>dB<br>mA                                                     |

| OPERATING TEMPERATURE RANGE                                                                                                              |                                                                                                                                                                                                                             | 0                        |                                      | 70           | °C                                                                |

Specifications subject to change without notice.

## ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage                                        |

|-------------------------------------------------------|

| Internal Power Dissipation <sup>2</sup>               |

| AD8072 8-Lead Plastic (N)                             |

| AD8072 8-Lead Small Outline (SO-8) 0.9 Watts          |

| AD8072 8-Lead µSOIC (RM) 0.6 Watts                    |

| AD8073 14-Lead Plastic (N) 1.6 Watts                  |

| AD8073 14-Lead Small Outline (R) 1.0 Watts            |

| Input Voltage (Common Mode) $\pm V_S$                 |

| Differential Input Voltage $\dots \pm 1.25 \text{ V}$ |

| Output Short Circuit Duration                         |

| Observe Power Derating Curves                         |

| Storage Temperature | Range |

|---------------------|-------|

| 17 D D17 D 1        |       |

## N, R, RM Packages . . . . . . . . . . . . -65°C to +125°C Lead Temperature Range (Soldering 10 sec) . . . . . . . . 300°C

<sup>1</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Specification is for device in free air: 8-Lead Plastic Package:  $\theta_{JA} = 90^{\circ}\text{C/W}$ 8-Lead SOIC Package:  $\theta_{JA} = 140^{\circ}\text{C/W}$ 8-Lead  $\mu SOIC$  Package:  $\theta_{JA} = 214^{\circ}C/W$ 14-Lead Plastic Package:  $\dot{\theta}_{JA} = 75^{\circ}C/W$ 14-Lead SOIC Package:  $\theta_{IA} = 120^{\circ}\text{C/W}$

## **ORDERING GUIDE**

| Model            | Temperature<br>Range | Package<br>Description | Package<br>Option |

|------------------|----------------------|------------------------|-------------------|

| *AD8072ARM       | −40°C to +85°C       | 8-Lead µSOIC           | RM-8              |

| *AD8072ARM-REEL  | −40°C to +85°C       | 13" Reel 8-Lead µSOIC  | RM-8              |

| *AD8072ARM-REEL7 | -40°C to +85°C       | 7" Reel 8-Lead µSOIC   | RM-8              |

| AD8072JN         | 0°C to 70°C          | 8-Lead Plastic DIP     | N-8               |

| AD8072JR         | 0°C to 70°C          | 8-Lead SOIC            | SO-8              |

| AD8072JR-REEL    | 0°C to 70°C          | 13" Reel 8-Lead SOIC   | SO-8              |

| AD8072JR-REEL7   | 0°C to 70°C          | 7" Reel 8-Lead SOIC    | SO-8              |

| AD8073JN         | 0°C to 70°C          | 14-Lead Plastic DIP    | N-14              |

| AD8073JR         | 0°C to 70°C          | 14-Lead Narrow SOIC    | R-14              |

| AD8073JR-REEL    | 0°C to 70°C          | 13" Reel 14-Lead SOIC  | R-14              |

| AD8073JR-REEL7   | 0°C to 70°C          | 7" Reel 14-Lead SOIC   | R-14              |

|                  |                      |                        |                   |

<sup>\*</sup>Brand Code: HLA

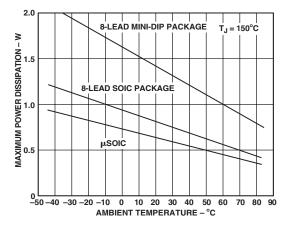

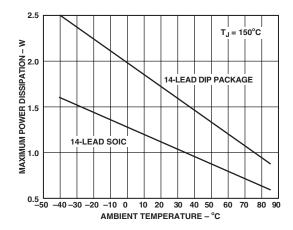

#### MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated by the AD8072 and AD8073 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Exceeding this limit temporarily may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of 175°C for an extended period can result in device failure.

While the AD8072 and AD8073 are internally short circuit protected, this may not be sufficient to guarantee that the maximum junction temperature (150°C) is not exceeded under all conditions. To ensure proper operation, it is necessary to observe the maximum power derating curves shown in Figures 2 and 3.

Figure 2. AD8072 Maximum Power Dissipation vs. Temperature

Figure 3. AD8073 Maximum Power Dissipation vs. Temperature

### CAUTION -

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8072/AD8073 feature proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

## **Typical Performance Characteristics— AD8073**

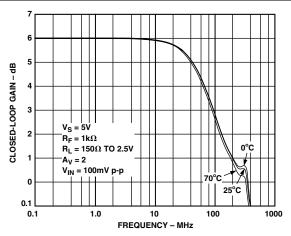

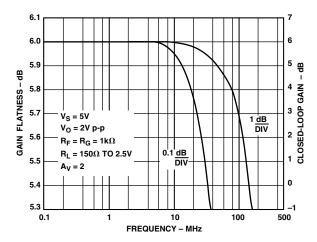

TPC 1. Frequency Response Over Temperature;  $V_S = 5 V$

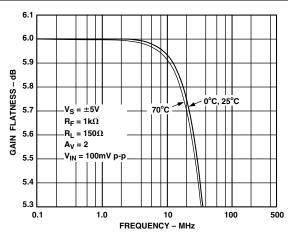

TPC 4. 0.1 dB Flatness vs. Frequency Over Temperature;  $V_S = \pm 5~V$

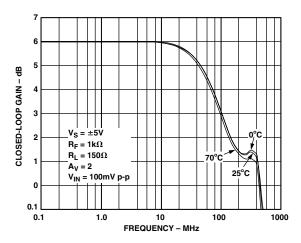

TPC 2. Frequency Response Over Temperature;  $V_S = \pm 5 \text{ V}$

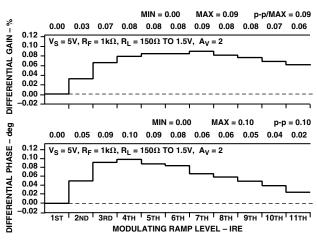

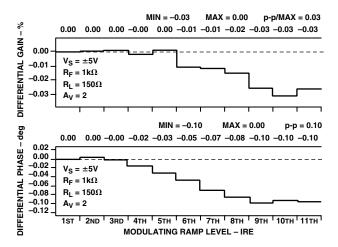

TPC 5. Differential Gain and Phase,  $V_S = 5 V$

TPC 3. 0.1 dB Flatness vs. Frequency Over Temperature;  $V_S = 5 V$

TPC 6. Differential Gain and Phase,  $V_S = \pm 5 \text{ V}$

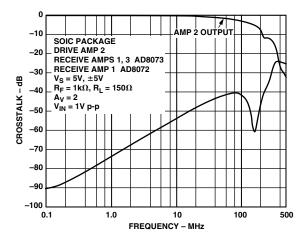

TPC 7. Crosstalk vs. Frequency

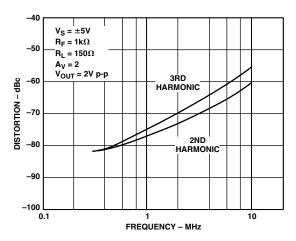

TPC 8. Distortion vs. Frequency;  $V_S = \pm 5 \text{ V}$

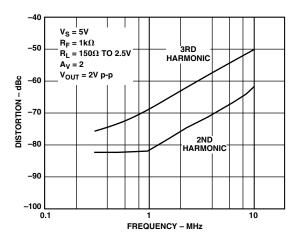

TPC 9. Distortion vs. Frequency;  $V_S = 5 V$

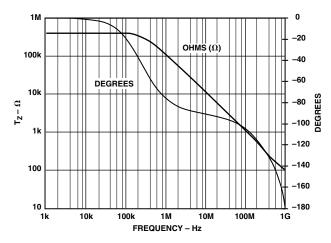

TPC 10. Open-Loop Transimpedance vs. Frequency

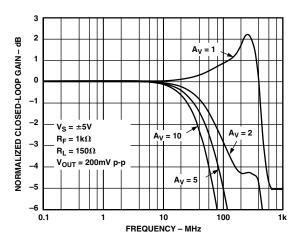

TPC 11. Normalized Frequency Response;  $V_S = \pm 5 V$

TPC 12. Large Signal Frequency Response

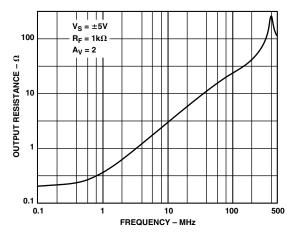

TPC 13. Output Resistance vs. Frequency;  $V_S = \pm 5 \text{ V}$

TPC 14. Noise vs. Frequency;  $V_S = \pm 5 \text{ V}$

TPC 15. Noise vs. Frequency;  $V_S = \pm 5 \text{ V}$

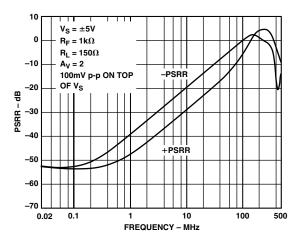

TPC 16. PSRR vs. Frequency

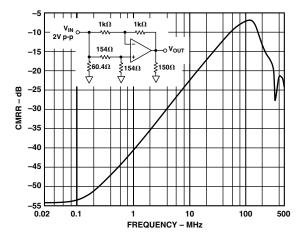

TPC 17. CMRR vs. Frequency;  $V_S = \pm 5 \text{ V}$

REV. D -7-

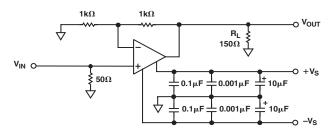

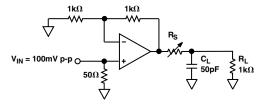

TPC 18. Test Circuit; Gain = +2

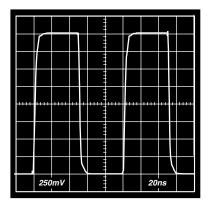

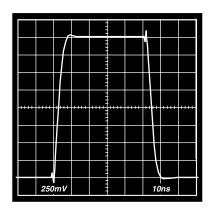

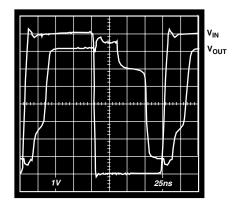

TPC 19. 2 V Step Response; G = +2,  $V_S = \pm 5$  V

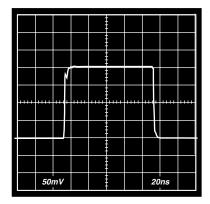

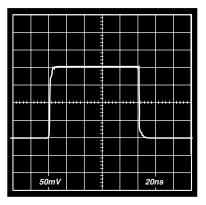

TPC 20. 200 mV Step Response; G = +2,  $V_S = \pm 5$  V

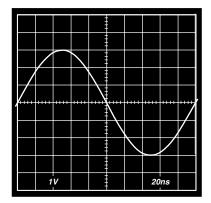

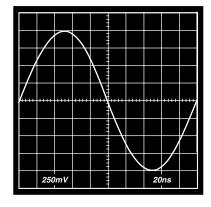

TPC 21. Sine Response; G = +2,  $V_S = \pm 5 V$

TPC 22. 2 V Step Response; G = +2,  $V_S = \pm 2.5 V^*$

TPC 23. 200 mV Step Response; G = +2,  $V_S = \pm 2.5 V^*$

TPC 24. Sine Response; G = +2,  $V_S = \pm 2.5 V^*$

<sup>\*</sup> $V_S$  =  $\pm 2.5$  V operation is identical to  $V_S$  = 5 V single supply operation.

## APPLICATIONS

## Overdrive Recovery

Overdrive of an amplifier occurs when the output and/or input range are exceeded. The amplifier must recover from this overdrive condition and resume normal operation. As shown in Figure 4, the AD8072 and AD8073 recover within 75 ns from positive overdrive and 30 ns from negative overdrive.

Figure 4. Overload Recovery;  $V_S = \pm 5$  V,  $V_{IN} = 8$  V p-p,  $R_F = 1$  k $\Omega$ ,  $R_L = 150$   $\Omega$ , G = +2

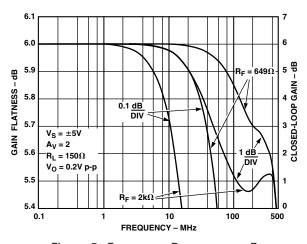

## Bandwidth vs. Feedback Resistor Value

The closed-loop frequency response of a current feedback amplifier is a function of the feedback resistor. A smaller feedback resistor will produce a wider bandwidth response. However, if the feedback resistance becomes too small, the gain flatness can be affected. As a practical consideration, the minimum value of feedback resistance for the AD8072/AD8073 was found to be 649  $\Omega$ . For resistances below this value, the gain flatness will be affected and more significant lot-to-lot variations in device performance will be noticed. Figure 5 shows a plot of the frequency response of an AD8072/AD8073 at a gain of two with both feedback and gain resistors equal to 649  $\Omega$ .

Figure 5. Frequency Response vs. R<sub>F</sub>

On the other hand, the bandwidth of a current feedback amplifier can be decreased by increasing the feedback resistance. This can sometimes be useful where it is desired to reduce the noise bandwidth of a system. As a practical matter, the maximum value of feedback resistor was found to be 2 k $\Omega$ . Figure 5 shows the frequency response of an AD8072/AD8073 at a gain of two with both feedback and gain resistors equal to 2 k $\Omega$ .

## **Capacitive Load Drive**

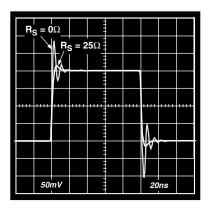

When an op amp output drives a capacitive load, extra phase shift due to the pole formed by the op amp's output impedance and the capacitor can cause peaking or even oscillation. The top trace of Figure 6,  $R_S = 0~\Omega$ , shows the output of one of the amplifiers of the AD8072/AD8073 when driving a 50 pF capacitor as shown in the schematic of Figure 7.

The amount of peaking can be significantly reduced by adding a resistor in series with the capacitor. The lower trace of Figure 6 shows the same capacitor being driven with a 25  $\Omega$  resistor in series with it. In general, the resistor value will have to be experimentally determined, but 10  $\Omega$  to 50  $\Omega$  is a practical range of values to experiment with for capacitive loads of up to a few hundred pF.

Figure 6. Capacitive Low Drive

Figure 7. Capacitive Load Drive Circuit

REV. D –9–

## Crosstalk

Crosstalk between internal amplifiers may vary depending on which amplifier is being driven and how many amplifiers are being driven. This variation typically stems from pin location on the package and the internal layout of the IC itself. Table I illustrates the typical crosstalk results for a combination of conditions.

Table I. AD8073JR Crosstalk Table (dB)

|           |             | Receive Amplifier |     |     |

|-----------|-------------|-------------------|-----|-----|

|           | AD8073JR    | 1                 | 2   | 3   |

|           | 1           | X                 | -60 | -56 |

| Drive     | 2           | -60               | X   | -60 |

| Amplifier | 3           | -54               | -60 | X   |

|           | All Hostile | -53               | -55 | -54 |

## **CONDITIONS**

$V_S = \pm 5 \text{ V}$

$R_F = 1 \text{ k}\Omega$ ,  $R_L = 150 \Omega$

$A_v = 2$

$V_{OUT} = 2 V p-p \text{ on Drive Amplifier}$

## **Layout Considerations**

The specified high speed performance of the AD8072 and AD8073 require careful attention to board layout and component selection. Proper RF design techniques and low parasitic component selection are mandatory.

The PCB should have a ground plane covering all unused portions of the component side of the board to provide a low impedance ground path. The ground plane should be removed from the area near the input pins to reduce stray capacitance.

Chip capacitors should be used for supply bypassing. One end of the capacitor should be connected to the ground plane and the other within 1/8 inches of each power pin. An additional large (4.7  $\mu\text{F}{-}10~\mu\text{F})$  tantalum electrolytic capacitor should be connected in parallel, but not necessarily as close to the supply pins, to provide current for fast large-signal changes at the device's output.

The feedback resistor should be located close to the inverting input pin in order to keep the stray capacitance at this node to a minimum. Capacitance variations of less than 1 pF at the inverting input will affect high speed performance.

Stripline design techniques should be used for long signal traces (greater than approximately 1 inch). These should be designed with a characteristic impedance of 50  $\Omega$  or 75  $\Omega$  and be properly terminated at each end.

–10– REV. D

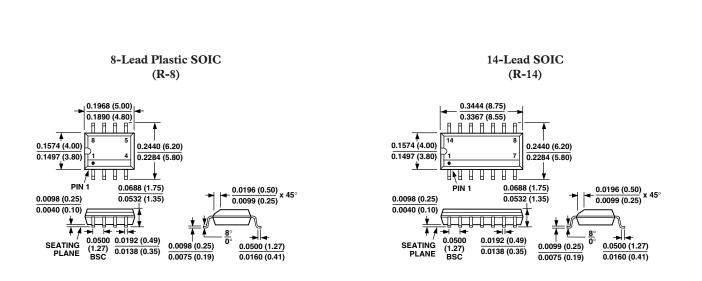

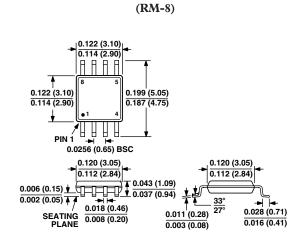

## **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 8-Lead Plastic DIP 14-Lead Plastic DIP (N-8)(N-14)0.430 (10.92) 0.795 (20.19) 0.348 (8.84) 0.725 (18.42) 0.280 (7.<u>11)</u> 0.280 (7.11) 0.240 (6.10) 0.325 (8.25) 0.240 (6.10) \_₩ 0.300 (7.62) 0.195 (4.95) 0.325 (8.25) PIN 1 0.300 (7.62) 0.060 (1.52) 0.115 (2.93) PIN 1 0.060 (1.52) 0.015 (0.38) 0.210 (5.33) MAX 0.015 (0.38) **▲** 0.195 (4.95) 0.210 (5.33) 0.130 (3.30) MIN мах↓∏ 0.115 (2.93) 0.130 (3.30) MIN 0.160 (4.06) 0.160 (4.06) 0.115 (2.93) 0.115 (2.93) 0.015 (0.381) 0.015 (0.381) SEATING PLANE 0.022 (0.558) 0.100 0.070 (1.77) SEATING PLANE 0.008 (0.204) 0.022 (0.558) 0.100 0.070 (1.77) 0.014 (0.356) (2.54) 0.045 (1.15) BSC 0.008 (0.204) (2.54) 0.045 (1.15) BSC 0.014 (0.356)

8-Lead µSOIC

REV. D –11–

# C01066-0-3/02(D)

# PRINTED IN U.S.A.

# **AD8073**

# **Revision History**

| Location                                        | Page |

|-------------------------------------------------|------|

| 3/02—Data Sheet changed from REV. C to REV. D.  |      |

| Edits to Package Outline                        | 1    |

| 10/01—Data Sheet changed from REV. B to REV. C. |      |

| Edits to ELECTRICAL CHARACTERISTICS             | 3    |

-12-