# 8-Channel, 10- and 12-Bit ADCs with I<sup>2</sup>C-Compatible Interface in 20-Lead TSSOP

# AD7997/AD7998

#### **FEATURES**

10- and 12-bit ADC with fast conversion time: 2  $\mu$ s typ 8 single-ended analog input channels Specified for  $V_{DD}$  of 2.7 V to 5.5 V Low power consumption

Fast throughput rate: up to 188 kSPS

Sequencer operation Automatic cycle mode

I<sup>2</sup>C°-compatible serial interface supports standard, fast, and high speed modes

Out-of-range indicator/alert function Pin-selectable addressing via AS Shutdown mode: 1 µA max

Temperature range: -40°C to +85°C

20-lead TSSOP package

See the AD7992 and AD7994 for 2-channel and 4-channel equivalent devices, respectively

#### **GENERAL DESCRIPTION**

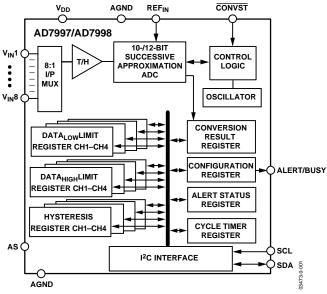

The AD7997/AD7998 are 8-channel, 10- and 12-bit, low power, successive approximation ADCs with an I²C-compatible interface. The parts operate from a single 2.7 V to 5.5 V power supply and feature a 2  $\mu s$  conversion time. The parts contain an 8-channel multiplexer and track-and-hold amplifier that can handle input frequencies up to 11 MHz.

The AD7997/AD7998 provide a 2-wire serial interface that is compatible with I $^2$ C interfaces. Each part comes in two versions, AD7997-0/AD7998-0 and AD7997-1/AD7998-1, and each version allows at least two different I $^2$ C addresses. The I $^2$ C interface on the AD7997-0/AD7998-0 supports standard and fast I $^2$ C interface modes. The I $^2$ C interface on the AD7997-1/AD7998-1 supports standard, fast, and high speed I $^2$ C interface modes.

The AD7997/AD7998 normally remain in a shutdown state while not converting, and power up only for conversions. The conversion process can be controlled using the  $\overline{\text{CONVST}}$  pin, by a command mode where conversions occur across  $I^2C$  write operations or an automatic conversion interval mode selected through software control.

The AD7997/AD7998 require an external reference that should be applied to the REF<sub>IN</sub> pin and can be in the range of 1.2 V to  $V_{\rm DD}$ . This allows the widest dynamic input range to the ADC.

#### Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

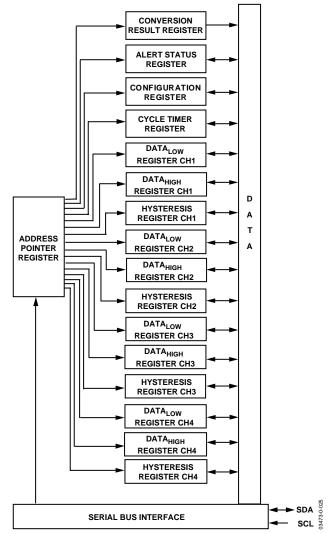

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

On-chip limit registers can be programmed with high and low limits for the conversion result, and an open-drain, out-of-range indicator output (ALERT) becomes active when the programmed high or low limits are violated by the conversion result. This output can be used as an interrupt.

### **PRODUCT HIGHLIGHTS**

- 1. 2 μs conversion time with low power consumption.

- 1<sup>2</sup>C-compatible serial interface with pin-selectable addresses. Two AD7997/AD7998 versions allow five AD7997/AD7998 devices to be connected to the same serial bus.

- 3. The parts feature automatic shutdown while not converting to maximize power efficiency. Current consumption is 1  $\mu$ A max when in shutdown mode at 3V.

- 4. Reference can be driven up to the power supply.

- Out-of-range indicator that can be software disabled or enabled.

- 6. One-shot and automatic conversion rates.

- Registers store minimum and maximum conversion results.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

# **TABLE OF CONTENTS**

| AD7997 Specifications                           | . 3 |

|-------------------------------------------------|-----|

| AD7998 Specifications                           | . 5 |

| I <sup>2</sup> C Timing Specifications          | . 7 |

| Absolute Maximum Ratings                        | . 9 |

| ESD Caution                                     | . 9 |

| Pin Configuration and Pin Function Descriptions | 10  |

| Terminology                                     | 11  |

| Typical Performance Characteristics             | 12  |

| Circuit Information                             | 15  |

| Converter Operation                             | 15  |

| Typical Connection Diagram                      | 16  |

| Analog Input                                    | 16  |

| Internal Register Structure                     | 18  |

| Address Pointer Register                        | 18  |

| Configuration Register                          | 19  |

| Conversion Result Register                      | 20  |

| Limit Registers                                 | 20  |

| Alert Status Register (CH1 to CH4)              | 21  |

| Cycle Timer Register                            | 22  |

| Sample Delay and Bit Trial Delay                | 22  |

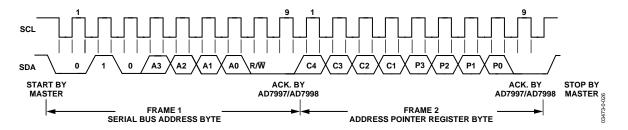

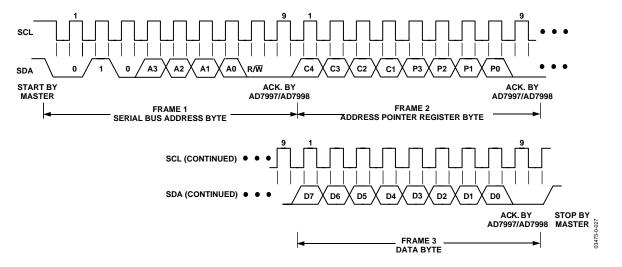

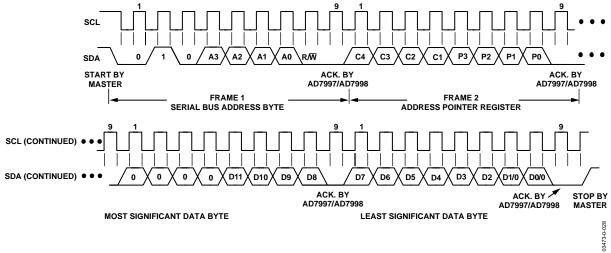

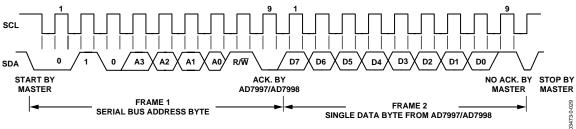

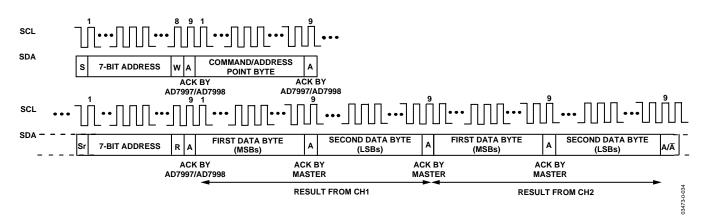

| Serial Interface                                | 23  |

| Serial Bus Address                                                           |

|------------------------------------------------------------------------------|

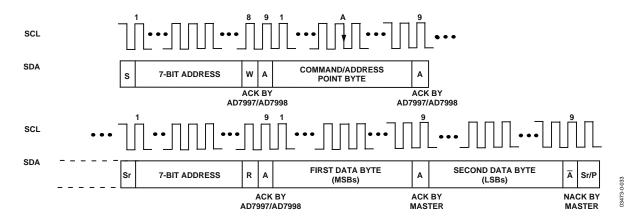

| Writing to the AD7997/AD7998                                                 |

| Writing to the Address Pointer Register for a Subsequent Read                |

| Writing a Single Byte of Data to the Alert Status Register or Cycle Register |

| Writing Two Bytes of Data to a Limit, Hysteresis, or Configuration Register  |

| Reading Data from the AD7997/AD7998                                          |

| ALERT/BUSY Pin                                                               |

| SMBus ALERT                                                                  |

| BUSY                                                                         |

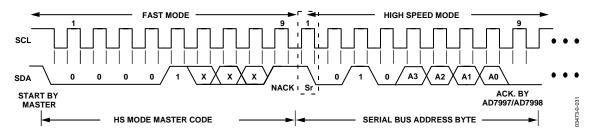

| Placing the AD7997-1/AD7998-1 into High Speed Mode 27                        |

| The Address Select (AS) Pin                                                  |

| Modes of Operation                                                           |

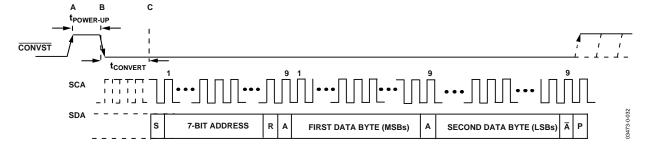

| Mode 1—Using the CONVST Pin                                                  |

| Mode 2 – COMMAND MODE29                                                      |

| Mode 3—Automatic Cycle Interval Mode 30                                      |

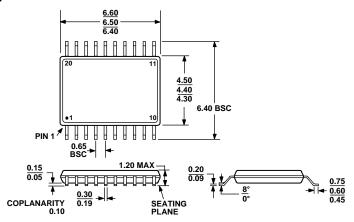

| Outline Dimensions                                                           |

| Ordering Guide31                                                             |

| Related Parts in I <sup>2</sup> C-Compatible ADC Product Family 31           |

### **REVISION HISTORY**

9/04—Revision 0: Initial Version

# **AD7997 SPECIFICATIONS**

Temperature range for B version is  $-40^{\circ}$ C to  $+85^{\circ}$ C. Unless otherwise noted,  $V_{DD} = 2.7 \text{ V}$  to 5.5 V; REF<sub>IN</sub> = 2.5 V; For the AD7997-0, all specifications apply for  $f_{SCL}$  up to 400 kHz; for the AD7997-1, all specifications apply for  $f_{SCL}$  up to 3.4 MHz, unless otherwise noted;  $T_A = T_{MIN}$  to  $T_{MAX}$ .

Table 1.

| Parameter                                           | B Version              | Unit        | Test Conditions/Comments                                                               |

|-----------------------------------------------------|------------------------|-------------|----------------------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE <sup>1</sup>                    |                        |             | $F_{IN} = 10$ kHz sine wave for $f_{SCL}$ from 1.7 MHz to                              |

|                                                     |                        |             | 3.4 MHz                                                                                |

| G. J. M. S. G. (00107)                              |                        |             | $F_{IN} = 1$ kHz sine wave for $f_{SCL}$ up to 400 kHz                                 |

| Signal to Noise + Distortion (SINAD) <sup>2</sup>   | 61                     | dB min      |                                                                                        |

| Total Harmonic Distortion (THD) <sup>2</sup>        | <b>-75</b>             | dB max      |                                                                                        |

| Peak Harmonic or Spurious Noise (SFDR) <sup>2</sup> | <b>-76</b>             | dB max      |                                                                                        |

| Intermodulation Distortion (IMD) <sup>2</sup>       |                        |             | $fa = 10.1 \text{ kHz}$ , $fb = 9.9 \text{ kHz}$ for $f_{SCL}$ from 1.7 MHz to 3.4 MHz |

|                                                     |                        |             | $fa = 1.1 \text{ kHz}$ , $fb = 0.9 \text{ kHz}$ for $f_{SCL}$ up to 400 kHz            |

| Second-Order Terms                                  | -86                    | dB typ      |                                                                                        |

| Third-Order Terms                                   | -86                    | dB typ      |                                                                                        |

| Aperture Delay <sup>2</sup>                         | 10                     | ns max      |                                                                                        |

| Aperture Jitter <sup>2</sup>                        | 50                     | ps typ      |                                                                                        |

| Channel-to-Channel Isolation <sup>2</sup>           | -90                    | dB typ      | $F_{IN} = 108$ Hz, see the Terminology section                                         |

| Full-Power Bandwidth <sup>2</sup>                   | 11                     | MHz typ     | @ 3 dB                                                                                 |

|                                                     | 2                      | MHz typ     | @ 0.1 dB                                                                               |

| DC ACCURACY                                         |                        |             |                                                                                        |

| Resolution                                          | 10                     | Bits        |                                                                                        |

| Integral Nonlinearity <sup>1, 2</sup>               | ±0.5                   | LSB max     |                                                                                        |

| Differential Nonlinearity <sup>1, 2</sup>           | ±0.5                   | LSB max     | Guaranteed no missed codes to 10 bits                                                  |

| Offset Error <sup>2</sup>                           | ±1.5                   | LSB max     | Mode 1 (CONVST Mode)                                                                   |

|                                                     | ±2.5                   | LSB max     | Mode 2 (Command Mode)                                                                  |

| Offset Error Match <sup>2</sup>                     | ±0.5                   | LSB max     |                                                                                        |

| Gain Error <sup>2</sup>                             | ±1.5                   | LSB max     |                                                                                        |

| Gain Error Match <sup>2</sup>                       | ±0.5                   | LSB max     |                                                                                        |

| ANALOG INPUT                                        |                        |             |                                                                                        |

| Input Voltage Range                                 | 0 to REF <sub>IN</sub> | V           |                                                                                        |

| DC Leakage Current                                  | ±1                     | μA max      |                                                                                        |

| Input Capacitance                                   | 30                     | pF typ      |                                                                                        |

| REFERENCE INPUT                                     |                        |             |                                                                                        |

| REF <sub>IN</sub> Input Voltage Range               | 1.2 to V <sub>DD</sub> | V min/V max |                                                                                        |

| DC Leakage Current                                  | ±1                     | μA max      |                                                                                        |

| Input Impedance                                     | 69                     | kΩ typ      | During a conversion                                                                    |

| LOGIC INPUTS (SDA, SCL)                             |                        |             |                                                                                        |

| Input High Voltage, V <sub>INH</sub>                | 0.7 (V <sub>DD</sub> ) | V min       |                                                                                        |

| Input Low Voltage, V <sub>INL</sub>                 | 0.3 (V <sub>DD</sub> ) | V max       |                                                                                        |

| Input Leakage Current, I <sub>IN</sub>              | ±1                     | μA max      | $V_{IN} = 0 \text{ V or } V_{DD}$                                                      |

| Input Capacitance, C <sub>IN</sub> <sup>3</sup>     | 10                     | pF max      |                                                                                        |

| Input Hysteresis, V <sub>HYST</sub>                 | 0.1 (V <sub>DD</sub> ) | V min       |                                                                                        |

| Parameter                                                     | B Version   | Unit           | Test Conditions/Comments                                                         |

|---------------------------------------------------------------|-------------|----------------|----------------------------------------------------------------------------------|

| LOGIC INPUTS (CONVST)                                         |             |                |                                                                                  |

| Input High Voltage, V <sub>INH</sub>                          | 2.4         | V min          | $V_{DD} = 5 \text{ V}$                                                           |

|                                                               | 2.0         | V min          | $V_{DD} = 3 \text{ V}$                                                           |

| Input Low Voltage, VINL                                       | 0.8         | V max          | $V_{DD} = 5 \text{ V}$                                                           |

|                                                               | 0.4         | V max          | $V_{DD} = 3 \text{ V}$                                                           |

| Input Leakage Current, I <sub>IN</sub>                        | ±1          | μA max         | $V_{IN} = 0 \text{ V or } V_{DD}$                                                |

| Input Capacitance, C <sub>IN</sub> <sup>3</sup>               | 10          | pF max         |                                                                                  |

| LOGIC OUTPUTS (OPEN-DRAIN)                                    |             | •              |                                                                                  |

| Output Low Voltage, V <sub>OL</sub>                           | 0.4         | V max          | $I_{SINK} = 3 \text{ mA}$                                                        |

|                                                               | 0.6         | V max          | $I_{SINK} = 6 \text{ mA}$                                                        |

| Floating-State Leakage Current                                | ± 1         | μA max         |                                                                                  |

| Floating-State Output Capacitance <sup>3</sup>                | 10          | pF max         |                                                                                  |

| Output Coding                                                 | Straight (N | atural) Binary |                                                                                  |

| CONVERSION RATE                                               |             | <u> </u>       | See the Modes of Operation section                                               |

| Conversion Time                                               | 2           | μs typ         | ·                                                                                |

| Throughput Rate                                               |             | , ,,           |                                                                                  |

| Mode 1 (Reading after the Conversion)                         | 5           | kSPS typ       | f <sub>SCL</sub> = 100 kHz                                                       |

| ,                                                             | 21          | kSPS typ       | $f_{SCL} = 400 \text{ kHz}$                                                      |

|                                                               | 121         | kSPS typ       | f <sub>SCL</sub> = 3.4 MHz                                                       |

| Mode 2                                                        | 5.5         | kSPS typ       | $f_{SCL} = 100 \text{ kHz}$                                                      |

|                                                               | 22          | kSPS typ       | $f_{SCL} = 400 \text{ kHz}$                                                      |

|                                                               | 147         | kSPS typ       | f <sub>SCL</sub> = 3.4 MHz, 188 kSPS typ @ 5 V                                   |

| POWER REQUIREMENTS                                            |             | , ,            |                                                                                  |

| $V_{DD}$                                                      | 2.7/5.5     | V min/max      |                                                                                  |

| loo                                                           |             |                | Digital inputs = $0 \text{ V or } V_{DD}$                                        |

| Power-Down Mode, Interface Inactive                           | 1/2         | μA max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}$                                           |

| Power-Down Mode, Interface Active                             | 0.07/0.3    | mA max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz f}_{SCL}$                  |

|                                                               | 0.3/0.6     | mA max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL}$                  |

| Operating, Interface Inactive                                 | 0.06/0.1    | mA max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz f}_{SCL}$                  |

|                                                               | 0.3/0.6     | mA max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL}$                  |

| Operating, Interface Active                                   | 0.15/0.4    | mA max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$                 |

| •                                                             | 0.6/1.1     | mA max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL} \text{ Mode 1}$   |

|                                                               | 0.7/1.4     | mA typ         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL} \text{ Mode 2}$   |

| Mode 3 (I <sup>2</sup> C Inactive, T <sub>CONVERT</sub> x 32) | 0.7/1.5     | mA max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}$                                           |

| Power Dissipation                                             |             |                |                                                                                  |

| Fully Operational                                             |             |                |                                                                                  |

| Operating, Interface Active                                   | 0.495/2.2   | mW max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$                 |

|                                                               | 1.98/6.05   | mW max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL} \text{ Mode 1}$   |

|                                                               | 2.31/7.7    | mW typ         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz } f_{SCL} \text{ Mode } 2$ |

| Power Down, Interface Inactive                                | 3.3/11      | μW max         | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}$                                           |

<sup>&</sup>lt;sup>1</sup> Max/min ac dynamic performance, INL and DNL specifications are typical specifications when operating in Mode 2 with I<sup>2</sup>C Hs-Mode SCL frequencies. Specifications outlined for Mode 2 apply to Mode 3 also. Sample delay and bit trial delay enabled.

<sup>2</sup> See the Terminology section.

<sup>3</sup> Guaranteed by initial characterization.

### **AD7998 SPECIFICATIONS**

Temperature range for B version is  $-40^{\circ}$ C to  $+85^{\circ}$ C. Unless otherwise noted,  $V_{DD} = 2.7 \text{ V}$  to 5.5 V; REF<sub>IN</sub> = 2.5 V; For the AD7998-0, all specifications apply for  $f_{SCL}$  up to 400 kHz; for the AD7998-1, all specifications apply for  $f_{SCL}$  up to 3.4 MHz, unless otherwise noted;  $T_A = T_{MIN}$  to  $T_{MAX}$ .

Table 2.

| 70.5                   |                                                                                                                             | $F_{IN}$ = 10 kHz sine wave for f <sub>SCL</sub> from 1.7 MHz to 3.4 MHz    |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|                        |                                                                                                                             | 3.4 MHz                                                                     |

|                        |                                                                                                                             |                                                                             |

|                        |                                                                                                                             | $F_{IN} = 1$ kHz sine wave for $f_{SCL}$ up to 400 kHz                      |

|                        | dB min                                                                                                                      |                                                                             |

|                        |                                                                                                                             |                                                                             |

|                        |                                                                                                                             |                                                                             |

| <del>-79</del>         | dB max                                                                                                                      |                                                                             |

|                        |                                                                                                                             | fa = 10.1 kHz, fb = 9.9 kHz f <sub>SCL</sub> from 1.7 MHz to 3.4 MHz        |

|                        |                                                                                                                             | $fa = 1.1 \text{ kHz}$ , $fb = 0.9 \text{ kHz}$ for $f_{SCL}$ up to 400 kHz |

| -90                    | dB typ                                                                                                                      |                                                                             |

| -90                    | dB typ                                                                                                                      |                                                                             |

| 10                     | ns max                                                                                                                      |                                                                             |

| 50                     | ps typ                                                                                                                      |                                                                             |

| -90                    | dB typ                                                                                                                      | $F_{IN} = 108$ Hz, see the Terminology section                              |

| 11                     | MHz typ                                                                                                                     | @ 3 dB                                                                      |

| 2                      | MHz typ                                                                                                                     | @ 0.1 dB                                                                    |

|                        |                                                                                                                             |                                                                             |

| 12                     | Bits                                                                                                                        |                                                                             |

| ±1                     | LSB max                                                                                                                     |                                                                             |

| ±0.2                   | LSB typ                                                                                                                     |                                                                             |

| +1/-0.9                | LSB max                                                                                                                     | Guaranteed no missed codes to 12 bits                                       |

| ±0.2                   | LSB typ                                                                                                                     |                                                                             |

| ±4                     | LSB max                                                                                                                     | Mode 1 (CONVST Mode)                                                        |

| ±6                     | LSB max                                                                                                                     | Mode 2 (Command Mode)                                                       |

| ±1                     | LSB max                                                                                                                     |                                                                             |

| ±2                     | LSB max                                                                                                                     |                                                                             |

| ±1                     | LSB max                                                                                                                     |                                                                             |

|                        |                                                                                                                             |                                                                             |

| 0 to REF <sub>IN</sub> | V                                                                                                                           |                                                                             |

|                        |                                                                                                                             |                                                                             |

|                        | •                                                                                                                           |                                                                             |

|                        | F. 515                                                                                                                      |                                                                             |

| 1.2 to V <sub>DD</sub> | V min/V max                                                                                                                 |                                                                             |

|                        | 1                                                                                                                           |                                                                             |

|                        | 1 _                                                                                                                         |                                                                             |

| 1                      |                                                                                                                             |                                                                             |

| 0.7 (Vpp)              | V min                                                                                                                       |                                                                             |

|                        |                                                                                                                             |                                                                             |

|                        |                                                                                                                             | $V_{IN} = 0 \text{ V or } V_{DD}$                                           |

|                        |                                                                                                                             |                                                                             |

| -                      | -                                                                                                                           |                                                                             |

|                        | 71<br>-78<br>-79<br>-90<br>-90<br>10<br>50<br>-90<br>11<br>2<br>12<br>±1<br>±0.2<br>+1/-0.9<br>±0.2<br>±4<br>±6<br>±1<br>±2 | 71 -78 -78 -79 -79 -79 -79 -79 -79 -79 -79 -79 -79                          |

| Parameter                                                     | B Version  | Unit            | Test Conditions/Comments                                                         |

|---------------------------------------------------------------|------------|-----------------|----------------------------------------------------------------------------------|

| LOGIC INPUTS (CONVST)                                         |            |                 |                                                                                  |

| Input High Voltage, V <sub>INH</sub>                          | 2.4        | V min           | $V_{DD} = 5 V$                                                                   |

|                                                               | 2.0        | V min           | $V_{DD} = 3 \text{ V}$                                                           |

| Input Low Voltage, V <sub>INL</sub>                           | 0.8        | V max           | $V_{DD} = 5 V$                                                                   |

| · · · · · · · · · · · · · · · · · · ·                         | 0.4        | V max           | $V_{DD} = 3 \text{ V}$                                                           |

| Input Leakage Current, I <sub>IN</sub>                        | ±1         | μA max          | $V_{IN} = 0 \text{ V or } V_{DD}$                                                |

| Input Capacitance, C <sub>IN</sub> <sup>3</sup>               | 10         | pF max          |                                                                                  |

| LOGIC OUTPUTS (OPEN-DRAIN)                                    |            |                 |                                                                                  |

| Output Low Voltage, Vol                                       | 0.4        | V max           | I <sub>SINK</sub> = 3 mA                                                         |

|                                                               | 0.6        | V max           | I <sub>SINK</sub> = 6 mA                                                         |

| Floating-State Leakage Current                                | ±1         | μA max          |                                                                                  |

| Floating-State Output Capacitance <sup>3</sup>                | 10         | pF max          |                                                                                  |

| Output Coding                                                 | Straight ( | Natural) Binary |                                                                                  |

| CONVERSION RATE                                               |            |                 | See the Modes of Operation section                                               |

| Conversion Time                                               | 2          | μs typ          | '                                                                                |

| Throughput Rate                                               |            | ' ''            |                                                                                  |

| Mode 1 (Reading after the Conversion)                         | 5          | kSPS typ        | f <sub>SCL</sub> = 100 kHz                                                       |

| , j                                                           | 21         | kSPS typ        | $f_{SCL} = 400 \text{ kHz}$                                                      |

|                                                               | 121        | kSPS typ        | f <sub>SCL</sub> = 3.4 MHz                                                       |

| Mode 2                                                        | 5.5        | kSPS typ        | $f_{SCL} = 100 \text{ kHz}$                                                      |

|                                                               | 22         | kSPS typ        | $f_{SCL} = 400 \text{ kHz}$                                                      |

|                                                               | 147        | kSPS typ        | $f_{SCL} = 3.4 \text{ MHz}$ , 188 kSPS typ @ 5 V                                 |

| POWER REQUIREMENTS                                            |            |                 |                                                                                  |

| $V_{DD}$                                                      | 2.7/5.5    | V min/max       |                                                                                  |

| IDD                                                           |            |                 | Digital inputs = $0 \text{ V or V}_{DD}$                                         |

| Power-Down Mode, Interface Inactive                           | 1/2        | μA max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}$                                           |

| Power-Down Mode, Interface Active                             | 0.07/0.3   | mA max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz f}_{SCL}$                  |

|                                                               | 0.3/0.6    | mA max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL}$                  |

| Operating, Interface Inactive                                 | 0.06/0.1   | mA max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz f}_{SCL}$                  |

|                                                               | 0.3/0.6    | mA max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz } f_{SCL}$                 |

| Operating, Interface Active                                   | 0.15/0.4   | mA max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz f}_{SCL}$                  |

|                                                               | 0.6/1.1    | mA max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz } f_{SCL} \text{ Mode } 1$ |

|                                                               | 0.7/1.4    | mA typ          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL} \text{ Mode 2}$   |

| Mode 3 (I <sup>2</sup> C Inactive, T <sub>CONVERT</sub> x 32) | 0.7/1.5    | mA max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}$                                           |

| Power Dissipation                                             |            |                 |                                                                                  |

| Fully Operational                                             |            |                 |                                                                                  |

| Operating, Interface Active                                   | 0.495/2.2  | mW max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 400 \text{ kHz } f_{SCL}$                 |

|                                                               | 1.98/6.05  | mW max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL} \text{ Mode 1}$   |

|                                                               | 2.31/7.7   | mW typ          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}, 3.4 \text{ MHz f}_{SCL} \text{ Mode 2}$   |

| Power Down, Interface Inactive                                | 3.3/11     | μW max          | $V_{DD} = 3.3 \text{ V}/5.5 \text{ V}$                                           |

<sup>&</sup>lt;sup>1</sup> Max/min ac dynamic performance, INL and DNL specifications are typical specifications when operating in Mode 2 with I<sup>2</sup>C Hs-Mode SCL frequencies. Specifications outlined for Mode 2 apply to Mode 3 also. Sample delay and bit trial delay enabled.

<sup>2</sup> See the Terminology section.

<sup>3</sup> Guaranteed by initial characterization.

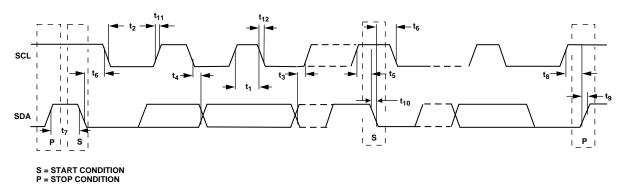

### I<sup>2</sup>C TIMING SPECIFICATIONS

Guaranteed by initial characterization. All values measured with input filtering enabled.  $C_B$  refers to capacitive load on the bus line.  $t_r$  and  $t_f$  measured between 0.3 VDD and 0.7 VDD.

High speed mode timing specifications apply to the AD7997-1/AD7998-1 only. Standard and fast mode timing specifications apply to both the AD7997-0/AD7998-0 and the AD7997-1/AD7998-1. See Figure 2. Unless otherwise noted,  $V_{DD} = 2.7 \text{ V}$  to 5.5 V; REF<sub>IN</sub> = 2.5 V;  $T_A = T_{MIN}$  to  $T_{MAX}$ .

Table 3.

|                             |                            | AD7997/AD7998 Limit at T <sub>MIN</sub> , T <sub>MAX</sub> |                 |      |                                                                       |  |  |

|-----------------------------|----------------------------|------------------------------------------------------------|-----------------|------|-----------------------------------------------------------------------|--|--|

| Parameter                   | Conditions                 | Min                                                        | Max             | Unit | Description                                                           |  |  |

| f <sub>SCL</sub>            | Standard mode              |                                                            | 100             | kHz  | Serial clock frequency                                                |  |  |

|                             | Fast mode                  |                                                            | 400             | kHz  |                                                                       |  |  |

|                             | High speed mode            |                                                            |                 |      |                                                                       |  |  |

|                             | $C_B = 100 \text{ pF max}$ |                                                            | 3.4             | MHz  |                                                                       |  |  |

|                             | $C_B = 400 \text{ pF max}$ |                                                            | 1.7             | MHz  |                                                                       |  |  |

| t <sub>1</sub>              | Standard mode              | 4                                                          |                 | μs   | t <sub>нібн</sub> , SCL high time                                     |  |  |

|                             | Fast mode                  | 0.6                                                        |                 | μs   |                                                                       |  |  |

|                             | High speed mode            |                                                            |                 |      |                                                                       |  |  |

|                             | $C_B = 100 pF max$         | 60                                                         |                 | ns   |                                                                       |  |  |

|                             | $C_B = 400 \text{ pF max}$ | 120                                                        |                 | ns   |                                                                       |  |  |

| t <sub>2</sub>              | Standard mode              | 4.7                                                        |                 | μs   | t <sub>LOW</sub> , SCL low time                                       |  |  |

|                             | Fast mode                  | 1.3                                                        |                 | μs   |                                                                       |  |  |

|                             | High speed mode            |                                                            |                 |      |                                                                       |  |  |

|                             | $C_B = 100 \text{ pF max}$ | 160                                                        |                 | ns   |                                                                       |  |  |

|                             | $C_B = 400 \text{ pF max}$ | 320                                                        |                 | ns   |                                                                       |  |  |

| t <sub>3</sub>              | Standard mode              | 250                                                        |                 | ns   | t <sub>SU;DAT</sub> , data setup time                                 |  |  |

|                             | Fast mode                  | 100                                                        |                 | ns   |                                                                       |  |  |

|                             | High speed mode            | 10                                                         |                 | ns   |                                                                       |  |  |

| t <sub>4</sub> <sup>1</sup> | Standard mode              | 0                                                          | 3.45            | μς   | t <sub>нд;рат</sub> , data hold time                                  |  |  |

|                             | Fast mode                  | 0                                                          | 0.9             | μs   |                                                                       |  |  |

|                             | High speed mode            |                                                            |                 |      |                                                                       |  |  |

|                             | $C_B = 100 \text{ pF max}$ | 0                                                          | 70 <sup>2</sup> | ns   |                                                                       |  |  |

|                             | $C_B = 400 \text{ pF max}$ | 0                                                          | 150             | ns   |                                                                       |  |  |

| <b>t</b> <sub>5</sub>       | Standard mode              | 4.7                                                        |                 | μs   | t <sub>SU;STA</sub> , setup time for a repeated start condition       |  |  |

|                             | Fast mode                  | 0.6                                                        |                 | μs   |                                                                       |  |  |

|                             | High speed mode            | 160                                                        |                 | ns   |                                                                       |  |  |

| <b>t</b> <sub>6</sub>       | Standard mode              | 4                                                          |                 | μς   | t <sub>HD;STA</sub> , hold time (repeated) start condition            |  |  |

|                             | Fast mode                  | 0.6                                                        |                 | μs   |                                                                       |  |  |

|                             | High speed mode            | 160                                                        |                 | ns   |                                                                       |  |  |

| t <sub>7</sub>              | Standard mode              | 4.7                                                        |                 | μς   | t <sub>BUF</sub> , bus free time between a stop and a start condition |  |  |

|                             | Fast mode                  | 1.3                                                        |                 | μs   |                                                                       |  |  |

| t <sub>8</sub>              | Standard mode              | 4                                                          |                 | μs   | t <sub>su;sto</sub> , setup time for stop condition                   |  |  |

|                             | Fast mode                  | 0.6                                                        |                 | μs   |                                                                       |  |  |

|                             | High speed mode            | 160                                                        |                 | ns   |                                                                       |  |  |

| <b>t</b> <sub>9</sub>       | Standard mode              |                                                            | 1000            | ns   | t <sub>RDA</sub> , rise time of SDA signal                            |  |  |

|                             | Fast mode                  | 20 + 0.1 C <sub>B</sub>                                    | 300             | ns   | ,                                                                     |  |  |

|                             | High speed mode            |                                                            |                 | 1    |                                                                       |  |  |

|                             | $C_B = 100 \text{ pF max}$ | 10                                                         | 80              | ns   |                                                                       |  |  |

|                             | $C_B = 400 \text{ pF max}$ | 20                                                         | 160             | ns   |                                                                       |  |  |

|                       |                            | AD7997/AD7998 Limit at T <sub>MIN</sub> , T <sub>MAX</sub> |      |        |                                                                                                           |  |  |

|-----------------------|----------------------------|------------------------------------------------------------|------|--------|-----------------------------------------------------------------------------------------------------------|--|--|

| Parameter             | Conditions                 | Min                                                        | Max  | Unit   | Description                                                                                               |  |  |

| t <sub>10</sub>       | Standard mode              |                                                            | 300  | ns     | t <sub>FDA</sub> , fall time of SDA signal                                                                |  |  |

|                       | Fast mode                  | 20 + 0.1 C <sub>B</sub>                                    | 300  | ns     |                                                                                                           |  |  |

|                       | High speed mode            |                                                            |      |        |                                                                                                           |  |  |

|                       | $C_B = 100 pF max$         | 10                                                         | 80   | ns     |                                                                                                           |  |  |

|                       | $C_B = 400 \text{ pF max}$ | 20                                                         | 160  | ns     |                                                                                                           |  |  |

| t <sub>11</sub>       | Standard mode              |                                                            | 1000 | ns     | t <sub>RCL</sub> , rise time of SCL signal                                                                |  |  |

|                       | Fast mode                  | 20 + 0.1 C <sub>B</sub>                                    | 300  | ns     |                                                                                                           |  |  |

|                       | High speed mode            |                                                            |      |        |                                                                                                           |  |  |

|                       | $C_B = 100 pF max$         | 10                                                         | 40   | ns     |                                                                                                           |  |  |

|                       | $C_B = 400 \text{ pF max}$ | 20                                                         | 80   | ns     |                                                                                                           |  |  |

| t <sub>11A</sub>      | Standard mode              |                                                            | 1000 | ns     | t <sub>RCL1</sub> , rise time of SCL signal after a repeated start condition and after an Acknowledge bit |  |  |

|                       | Fast mode                  | 20 + 0.1 C <sub>B</sub>                                    | 300  | ns     |                                                                                                           |  |  |

|                       | High speed mode            |                                                            |      |        |                                                                                                           |  |  |

|                       | $C_B = 100 pF max$         | 10                                                         | 80   | ns     |                                                                                                           |  |  |

|                       | $C_B = 400 \text{ pF max}$ | 20                                                         | 160  | ns     |                                                                                                           |  |  |

| t <sub>12</sub>       | Standard mode              |                                                            | 300  | ns     | t <sub>FCL</sub> , fall time of SCL signal                                                                |  |  |

|                       | Fast mode                  | 20 + 0.1 C <sub>B</sub>                                    | 300  | ns     |                                                                                                           |  |  |

|                       | High speed mode            |                                                            |      |        |                                                                                                           |  |  |

|                       | $C_B = 100 pF max$         | 10                                                         | 40   | ns     |                                                                                                           |  |  |

|                       | $C_B = 400 \text{ pF max}$ | 20                                                         | 80   | ns     |                                                                                                           |  |  |

| t <sub>SP</sub>       | Fast mode                  | 0                                                          | 50   | ns     | Pulse width of suppressed spike                                                                           |  |  |

|                       | High speed mode            | 0                                                          | 10   | ns     |                                                                                                           |  |  |

| t <sub>POWER-UP</sub> |                            | 1                                                          |      | typ μs | Power-up time                                                                                             |  |  |

$<sup>^1</sup>$  A device must provide a data hold time for SDA in order to bridge the undefined region of the SCL falling edge.  $^2$  For 3 V supplies, the maximum hold time with  $C_B = 100$  pF max is 100 ns max.

Figure 2. Timing Diagram for 2-Wire Serial Interface

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 4

| 1 able 4.                                             |                                            |

|-------------------------------------------------------|--------------------------------------------|

| Parameter                                             | Rating                                     |

| V <sub>DD</sub> to GND                                | –0.3 V to 7 V                              |

| Analog Input Voltage to GND                           | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Reference Input Voltage to GND                        | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Digital Input Voltage to GND                          | −0.3 V to +7 V                             |

| Digital Output Voltage to GND                         | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Input Current to Any Pin Except Supplies <sup>1</sup> | ±10 mA                                     |

| Operating Temperature Range                           |                                            |

| Commercial (B Version)                                | −40°C to +85°C                             |

| Storage Temperature Range                             | −65°C to +150°                             |

| Junction Temperature                                  | 150°C                                      |

| 20-Lead TSSOP                                         |                                            |

| $\theta_{JA}$ Thermal Impedance                       | 143°C/W                                    |

| $\theta_{JC}$ Thermal Impedance                       | 45°C/W                                     |

| Pb/SN Temperature, Soldering                          |                                            |

| Reflow (10 s to 30 s)                                 | 240 (+0/-5)°C                              |

| Pb-free Temperature, Soldering                        |                                            |

| Reflow                                                | 260 (+0)°C                                 |

| ESD                                                   | 1.5 kV                                     |

|                                                       |                                            |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>1</sup> Transient currents of up to 100 mA do not cause SCR latch-up.

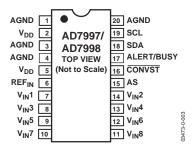

### PIN CONFIGURATION AND PIN FUNCTION DESCRIPTIONS

Figure 3. AD7998/AD7997 Pin Configuration

### **Table 5. Pin Function Descriptions**

| Pin No.        | Mnemonic          | Function                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3,<br>4, 20 | AGND              | Analog Ground. Ground reference point for all circuitry on the AD7997/AD7998. All analog input signals should be referred to this AGND voltage.                                                                                                                                                                                                                                                                                       |

| 2, 5           | $V_{DD}$          | Power Supply Input. The V <sub>DD</sub> range for the AD7997/AD7998 is from 2.7 V to 5.5 V.                                                                                                                                                                                                                                                                                                                                           |

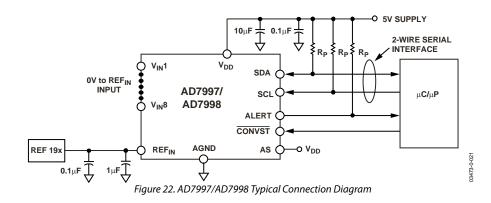

| 6              | REF <sub>IN</sub> | Voltage Reference Input. The external reference for the AD7997/AD7998 should be applied to this input pin. The voltage range for the external reference is 1.2 V to $V_{DD}$ . A 0.1 $\mu F$ and 1 $\mu F$ capacitors should be placed between REF <sub>IN</sub> and AGND. See Typical Connection Diagram.                                                                                                                            |

| 7              | V <sub>IN</sub> 1 | Analog Input 1. Single-ended analog input channel. The input range is 0 V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                      |

| 8              | V <sub>IN</sub> 3 | Analog Input 3. Single-ended analog input channel. The input range is 0 V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                      |

| 9              | V <sub>IN</sub> 5 | Analog Input 5. Single-ended analog input channel. The input range is 0 V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                      |

| 10             | V <sub>IN</sub> 7 | Analog Input 7. Single-ended analog input channel. The input range is 0 V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                      |

| 11             | V <sub>IN</sub> 8 | Analog Input 8. Single-ended analog input channel. The input range is 0 V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                      |

| 12             | V <sub>IN</sub> 6 | Analog Input 6. Single-ended analog input channel. The input range is 0 V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                      |

| 13             | V <sub>IN</sub> 4 | Analog Input 4. Single-ended analog input channel. The input range is 0 V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                      |

| 14             | V <sub>IN</sub> 2 | Analog Input 2. Single-ended analog input channel. The input range is 0 V to REF <sub>IN</sub> .                                                                                                                                                                                                                                                                                                                                      |

| 15             | AS                | Logic Input. Address select input that selects one of three I <sup>2</sup> C addresses for the AD7997/AD7998, as shown in Table 6. The device address depends on the voltage applied to this pin.                                                                                                                                                                                                                                     |

| 16             | CONVST            | Logic Input Signal. Convert start signal. This is an edge-triggered logic input. The rising edge of this signal powers up the part. The power-up time for the part is 1 µs. The falling edge of CONVST places the track/hold into hold mode and initiates a conversion. A power-up time of at least 1 µs must be allowed for the CONVST high pulse; otherwise, the conversion result is invalid (see the Modes of Operation section). |

| 17             | ALERT/BUSY        | Digital Output. Selectable as an ALERT or BUSY output function. When configured as an ALERT, this pin acts as an out-of-range indicator and, if enabled, becomes active when the conversion result violates the DATAHIGH or DATALOW register values. See the Limit Registers section. When configured as a BUSY output, this pin becomes active when a conversion is in progress. Open-drain output.                                  |

| 18             | SDA               | Digital I/O. Serial bus bidirectional data. Open-drain output. External pull-up resistor required.                                                                                                                                                                                                                                                                                                                                    |

| 19             | SCL               | Digital Input. Serial bus clock. Open-drain input. External pull-up resistor required.                                                                                                                                                                                                                                                                                                                                                |

### Table 6. I<sup>2</sup>C Address Selection

| Part Number           | AS Pin   | I <sup>2</sup> C Address |  |

|-----------------------|----------|--------------------------|--|

| AD7997-0              | AGND     | 010 0001                 |  |

| AD7997-0              | $V_{DD}$ | 010 0010                 |  |

| AD7997-1              | AGND     | 010 0011                 |  |

| AD7997-1              | $V_{DD}$ | 010 0100                 |  |

| AD7997-x1             | Float    | 010 0000                 |  |

| AD7998-0              | AGND     | 010 0001                 |  |

| AD7998-0              | $V_{DD}$ | 010 0010                 |  |

| AD7998-1              | AGND     | 010 0011                 |  |

| AD7998-1              | $V_{DD}$ | 010 0100                 |  |

| AD7998-x <sup>1</sup> | Float    | 010 0000                 |  |

$<sup>^{\</sup>rm 1}$  If the AS pin is left floating on any of the AD7997/AD7998 parts, the device address is 010 0000.

### **TERMINOLOGY**

### Signal-to-Noise and Distortion Ratio (SINAD)

The measured ratio of signal-to-noise and distortion at the output of the A/D converter. The signal is the rms amplitude of the fundamental. Noise is the sum of all nonfundamental signals up to half the sampling frequency (fs/2), excluding dc. The ratio is dependent on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal-to-noise and distortion ratio for an ideal N-bit converter with a sine wave input is given by

$$Signal-to-(Noise + Distortion) = (6.02 N + 1.76) dB$$

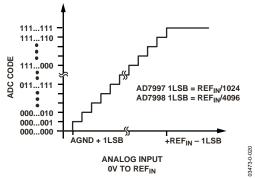

Thus, the SINAD is 61.96 dB for a 10-bit converter and 74 dB for a 12-bit converter.

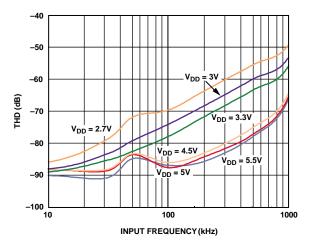

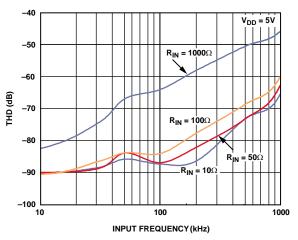

### **Total Harmonic Distortion (THD)**

The ratio of the rms sum of harmonics to the fundamental. For the AD7997/AD7998, it is defined as

THD (dB) =

$$20 \log \frac{\sqrt{V_2^2 + V_3^2 + V_4^2 + V_5^2 + V_6^2}}{V_1}$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$ , and  $V_6$  are the rms amplitudes of the second through sixth harmonics.

### Peak Harmonic or Spurious Noise

The ratio of the rms value of the next largest component in the ADC output spectrum (up to  $f_{\rm S}/2$  and excluding dc) to the rms value of the fundamental. Typically, the value of this specification is determined by the largest harmonic in the spectrum, but for ADCs where the harmonics are buried in the noise floor, it is a noise peak.

### **Intermodulation Distortion**

With inputs consisting of sine waves at two frequencies, fa and fb, any active device with nonlinearities creates distortion products at sum and difference frequencies of mfa  $\pm$  nfb, where m, n = 0, 1, 2, 3, and so on. Intermodulation distortion terms are those for which neither m nor n equal zero. For example, second-order terms include (fa + fb) and (fa - fb), while third-order terms include (2fa + fb), (2fa - fb),(fa + 2fb) and (fa - 2fb).

The AD7997/AD7998 is tested using the CCIF standard where two input frequencies near the top end of the input bandwidth are used. In this case, the second-order terms are usually distanced in frequency from the original sine waves while the third-order terms are usually at a frequency close to the input frequencies. As a result, the second and third-order terms are specified separately. The calculation of intermodulation distortion is, like the THD specification, the ratio of the rms sum of the individual distortion products to the rms amplitude of the sum of the fundamentals, expressed in dB.

#### **Channel-to-Channel Isolation**

A measure of the level of crosstalk between channels, taken by applying a full-scale sine wave signal to the unselected input channels, and determining how much the 108 Hz signal is attenuated in the selected channel. The sine wave signal applied to the unselected channels is then varied from 1 kHz up to 2 MHz, each time determining how much the 108 Hz signal in the selected channel is attenuated. This figure represents the worst-case level across all channels.

#### **Aperture Delay**

The measured interval between the sampling clock's leading edge and the point at which the ADC takes the sample.

#### **Aperture Jitter**

This is the sample-to-sample variation in the effective point in time at which the sample is taken.

#### **Full-Power Bandwidth**

The input frequency at which the amplitude of the reconstructed fundamental is reduced by 0.1 dB or 3 dB for a full-scale input.

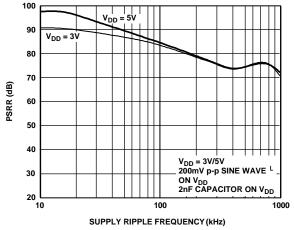

#### Power Supply Rejection Ratio (PSRR)

The ratio of the power in the ADC output at the full-scale frequency, *f*, to the power of a 200 mV p-p sine wave applied to the ADC V<sub>DD</sub> supply of frequency *f*s:

$$PSRR$$

(dB) =  $10 \log (Pf/Pf_S)$

where Pf is the power at frequency f in the ADC output;  $Pf_S$  is the power at frequency  $f_S$  coupled onto the ADC  $V_{DD}$  supply.

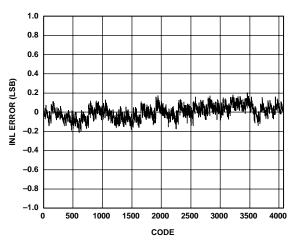

#### **Integral Nonlinearity**

The maximum deviation from a straight line passing through the endpoints of the ADC transfer function. The endpoints are zero scale, a point 1 LSB below the first code transition, and full scale, a point 1 LSB above the last code transition.

#### **Differential Nonlinearity**

The difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### Offset Error

The deviation of the first code transition (00...000) to (00...001) from the ideal—that is AGND + 1 LSB.

### Offset Error Match

The difference in offset error between any two channels.

#### **Gain Error**

The deviation of the last code transition (111...110) to (111...111) from the ideal (that is,  $REF_{IN}-1$  LSB) after the offset error has been adjusted out.

### **Gain Error Match**

The difference in gain error between any two channels.

### TYPICAL PERFORMANCE CHARACTERISTICS

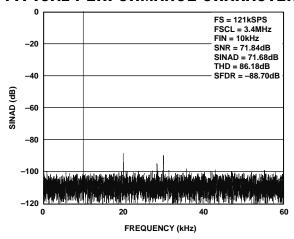

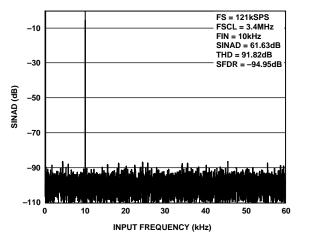

Figure 4. AD7998 Dynamic Performance with 5 V Supply and 2.5 V Reference, 121 kSPS, Mode 1

Figure 5. AD7997 Dynamic Performance with 5 V Supply and 2.5 V Reference, 121 kSPS, Mode 1

Figure 6. PSRR vs. Supply Ripple Frequency

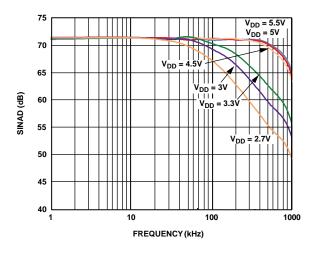

Figure 7. AD7998 SINAD vs. Analog Input Frequency for Various Supply Voltages, 3.4 MHz f<sub>SCL</sub>, 136 kSPS

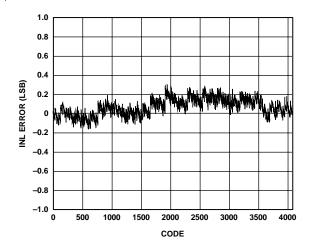

Figure 8. Typical INL,  $V_{DD} = 5.5 V$ , Mode 1, 3.4 MHz  $f_{SCL}$ , 121 kSPS

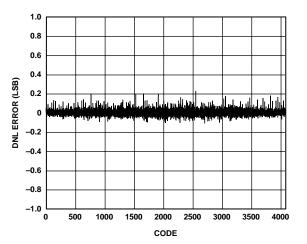

Figure 9. Typical DNL,  $V_{DD} = 5.5 V$ , Mode 1, 3.4 MHz  $f_{SCL}$ , 121 kSPS

Figure 10. Typical INL,  $V_{DD} = 2.7 \text{ V}$ , Mode 1, 3.4 MHz  $f_{SCL}$ , 121 kSPS

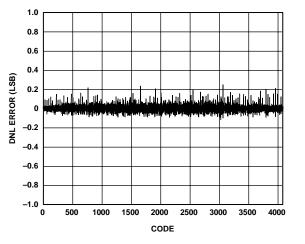

Figure 11. Typical DNL,  $V_{DD} = 2.7 \text{ V}$ , Mode 1, 3.4 MHz  $f_{SCL}$ , 121 kSPS

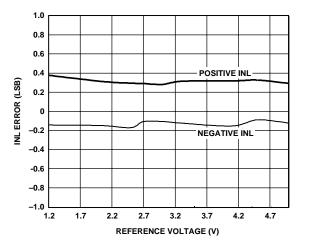

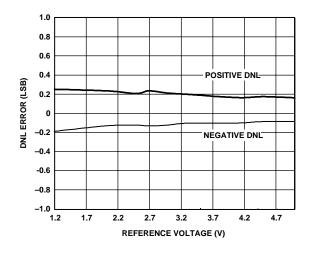

Figure 12. AD7998 Change in INL vs. Reference Voltage  $V_{DD} = 5 V$ , Mode 1, 121 kSPS

Figure 13. AD7998 Change in DNL vs. Reference Voltage  $V_{DD} = 5 V$ , Mode 1, 121 kSPS

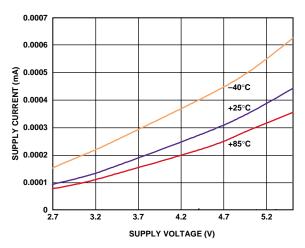

Figure 14. AD7998 Shutdown Current vs. Supply Voltage,  $-40^{\circ}$ C,  $+25^{\circ}$ C, and  $+85^{\circ}$ C

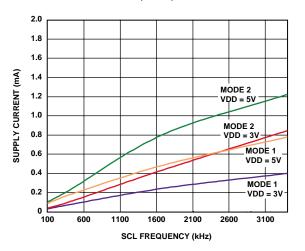

Figure 15. AD7998 Average Supply Current vs.  $l^2C$  Bus Rate for  $V_{DD} = 3 V$  and 5 V

03473-0-015

03473-0-011

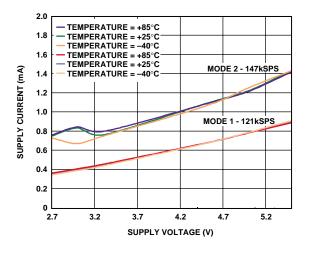

Figure 16. AD7998 Average Supply Current vs. Supply Voltage for Various Temperatures

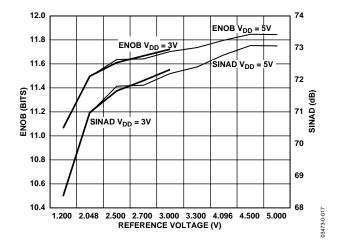

Figure 17. SINAD/ENOB vs. Reference Voltage, Mode 1, 121 kSPS

### CIRCUIT INFORMATION

The AD7997/AD7998 are low power, 10- and 12-bit, single-supply, 8-channel A/D converters. The parts can be operated from a 2.7 V to 5.5 V supply.

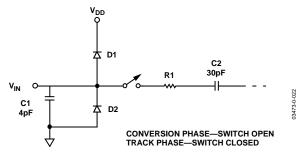

The AD7997/AD7998 have an 8-channel multiplexer, an onchip track-and-hold, an A/D converter, an on-chip oscillator, internal data registers, and an I $^2$ C-compatible serial interface, all housed in a 20-lead TSSOP. This package offers considerable space-saving advantages over alternative solutions. The AD7997/AD7998 require an external reference in the range of 1.2 V to  $V_{\rm DD}$ .