# 3 V/5 V, Rail-to-Rail Quad, 8-Bit DAC

## AD7304/AD7305

#### **FEATURES**

Four 8-bit DACs in one package +3 V, +5 V, and ±5 V operation Rail-to-rail REF input to voltage output swing 2.6 MHz reference multiplying bandwidth Internal power-on reset SPI serial interface-compatible—AD7304 Fast parallel interface—AD7305 40 µA power shutdown

#### **APPLICATIONS**

Automotive output span voltage Instrumentation, digitally controlled calibration Pin-compatible AD7226 replacement when  $V_{\rm DD} < 5.5~V$

#### **GENERAL DESCRIPTION**

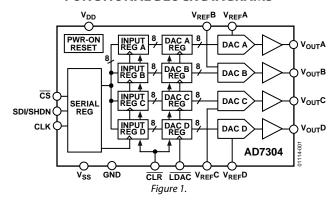

The AD7304/AD7305 $^1$  are quad, 8-bit DACs that operate from a single +3 V to +5 V supply, or  $\pm 5$  V supplies. The AD7304 has a serial interface, while the AD7305 has a parallel interface. Internal precision buffers swing rail-to-rail. The reference input range includes both supply rails, allowing for positive or negative full-scale output voltages. Operation is guaranteed over the supply voltage range of 2.7 V to 5.5 V, consuming less than 9 mW from a 3 V supply.

The full-scale voltage output is determined by the external reference input voltage applied. The rail-to-rail  $V_{\text{REF}}$  input to DAC  $V_{\text{OUT}}$  allows for a full-scale voltage set equal to the positive supply,  $V_{\text{DD}}$ , the negative supply,  $V_{\text{SS}}$ , or any value in between.

The AD7304's doubled-buffered serial data interface offers high speed, 3-wire, SPI\*-, and microcontroller-compatible inputs using data in (SDI), clock (CLK), and chip select  $(\overline{CS})$  pins. Additionally, an internal power-on reset sets the output to zero scale

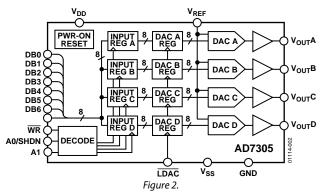

The parallel input AD7305 uses a standard address decode along with the  $\overline{WR}$  control line to load data into the input registers.

The double-buffered architecture allows all four input registers to be preloaded with new values, followed by an LDAC control strobe that copies all the new data into the DAC registers, thereby updating the analog output values.

#### Rev. C

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

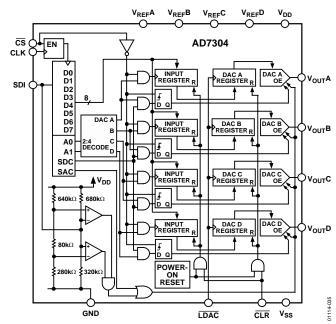

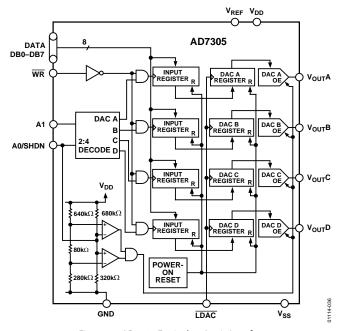

#### **FUNCTIONAL BLOCK DIAGRAMS**

When operating from less than 5.5 V, the AD7305 is pin-compatible with the popular industry-standard AD7226.

An internal power-on reset places both parts in the zero-scale state at turn-on. A 40  $\mu$ A power shutdown (SHDN) feature is activated on both parts by three-stating the SDI/SHDN pin on the AD7304 and three-stating the A0/SHDN address pin on the AD7305.

The AD7304/AD7305 are specified over the extended industrial –40°C to +85°C and the automotive –40°C to +125°C temperature ranges. AD7304s are available in a wide-body 16-lead SOIC (R-16) package. The parallel input AD7305 is available in the wide-body 20-lead SOIC (R-20) surface-mount package. For ultracompact applications, the thin 1.1 mm, 16-lead TSSOP (RU-16) package is available for the AD7304, while the 20-lead TSSOP (RU-20) houses the AD7305.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2004 Analog Devices, Inc. All rights reserved.

<sup>&</sup>lt;sup>1</sup> Protected under Patent No. 5684481.

## **TABLE OF CONTENTS**

2/98—Revision 0: Initial Version

| Specifications                                 | 3                    |

|------------------------------------------------|----------------------|

| Timing Specifications                          | 4                    |

| Absolute Maximum Ratings                       | 5                    |

| ESD Caution                                    | 5                    |

| Pin Configurations and Function Descriptions   | 8                    |

| Typical Performance Characteristics            | 10                   |

| Circuit Operation                              | 14                   |

| DAC Section                                    | 14                   |

| AD7304 Serial Data Interface                   | 15                   |

| AD7304 Hardware Shutdown SHDN                  | 15                   |

| Revision History                               |                      |

| nevision instory                               |                      |

| 11/04—Data Sheet Changed from Rev. B to Rev. C |                      |

| •                                              | 15<br>15<br>16<br>16 |

| Update Format                                  | 15<br>15<br>16<br>16 |

| AD7304/AD7305 Power-On Reset   | 15 |

|--------------------------------|----|

| Power up sequence              | 15 |

| AD7305 Parallel Data Interface | 16 |

| AD7226 Pin Compatibility       | 16 |

| AD7305 Hardware Shutdown SHDN  | 16 |

| ESD Protection Circuits        | 16 |

| Applications                   | 17 |

| Outline Dimensions             | 18 |

| Ordering Guide                 | 19 |

### **SPECIFICATIONS**

@  $V_{DD} = 3 \text{ V}$  or 5 V,  $V_{SS} = 0 \text{ V}$ ; or  $V_{DD} = +5 \text{ V}$  and  $V_{SS} = -5 \text{ V}$ ,  $V_{SS} \le V_{REF} \le V_{DD}$ ,  $-40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}/+125^{\circ}\text{C}$ , unless otherwise noted. Table 1.

| Parameter                                          | Symbol                             | Condition                                                               | 3 V ± 10%                        | 5 V ± 10%       | ±5 V ± 10%                       | Unit        |

|----------------------------------------------------|------------------------------------|-------------------------------------------------------------------------|----------------------------------|-----------------|----------------------------------|-------------|

| STATIC PERFORMANCE                                 |                                    |                                                                         |                                  |                 |                                  |             |

| Resolution <sup>1</sup>                            | N                                  |                                                                         | 8                                | 8               | 8                                | Bits        |

| Integral Nonlinearity <sup>2</sup>                 | INL                                |                                                                         | ±1                               | ±1              | ±1                               | LSB max     |

| Differential Nonlinearity                          | DNL                                | Monotonic, all codes 0 to 0xFF                                          | ±1                               | ±1              | ±1                               | LSB max     |

| Zero-Scale Error                                   | $V_{ZSE}$                          | Data = 0x00                                                             | 15                               | 15              | ±15                              | mV max      |

| Full-Scale Voltage Error                           | $V_{\text{FSE}}$                   | Data = 0xFF                                                             | ±4                               | ±4              | ±4                               | LSB max     |

| Full-Scale Temperature<br>Coefficient <sup>3</sup> | TCV <sub>FS</sub>                  |                                                                         | 5                                | 5               | 5                                | ppm/°C typ⁴ |

| REFERENCE INPUT                                    |                                    |                                                                         |                                  |                 |                                  |             |

| V <sub>REFIN</sub> Range                           | $V_{REFIN}$                        |                                                                         | V <sub>SS</sub> /V <sub>DD</sub> | $V_{SS}/V_{DD}$ | $V_{SS}/V_{DD}$                  | V min/max   |

| Input Resistance (AD7304)                          | R <sub>REFIN</sub>                 | Code = 0x55                                                             | 28                               | 28              | 28                               | kΩ typ      |

| Input Resistance (AD7305)                          | R <sub>REFIN</sub>                 | All DACs at code = 0x55                                                 | 7.5                              | 7.5             | 7.5                              | kΩ typ      |

| Input Capacitance <sup>3</sup>                     | C <sub>REFIN</sub>                 |                                                                         | 5                                | 5               | 5                                | pF typ      |

| ANALOG OUTPUTS                                     |                                    |                                                                         |                                  |                 |                                  |             |

| Output Voltage Range                               | V <sub>OUT</sub>                   |                                                                         | $V_{SS}/V_{DD}$                  | $V_{SS}/V_{DD}$ | V <sub>SS</sub> /V <sub>DD</sub> | V min/max   |

| Output Current Drive                               | Іоит                               | Code = $0x80$ , $\Delta V_{OUT} < 1$ LSB                                | ±3                               | ±3              | ±3                               | mA typ      |

| Shutdown Resistance                                | R <sub>оит</sub>                   | DAC outputs placed in shutdown state                                    | 120                              | 120             | 120                              | kΩ typ      |

| Capacitive Load <sup>3</sup>                       | $C_L$                              | No oscillation                                                          | 200                              | 200             | 200                              | pF typ      |

| LOGIC INPUTS                                       |                                    |                                                                         |                                  |                 |                                  |             |

| Logic Input Low Voltage                            | V <sub>IL</sub>                    |                                                                         | 0.6                              | 0.8             | 0.8                              | V min       |

| Logic Input High Voltage                           | V <sub>IH</sub>                    |                                                                         | 2.1                              | 2.4             | 2.4                              | V max       |

| Input Leakage Current⁵                             | I <sub>IL</sub>                    |                                                                         | ±10                              | ±10             | ±10                              | μA max      |

| Input Capacitance <sup>3</sup>                     | C <sub>IL</sub>                    |                                                                         | 8                                | 8               | 8                                | pF max      |

| AC CHARACTERISTICS <sup>3</sup>                    |                                    |                                                                         |                                  |                 |                                  |             |

| Output Slew Rate                                   | SR                                 | Code = 0x00  to  0xFF  to  0x00                                         | 1/2.7                            | 1/3.6           | 1.0/3.6                          | V/µs min/ty |

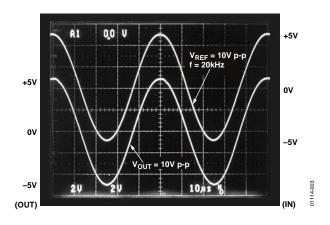

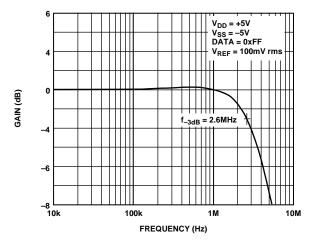

| Reference Multiplying                              | BW                                 | Small signal, $V_{SS} = -5 \text{ V}$                                   |                                  |                 | 2.6                              | MHz typ     |

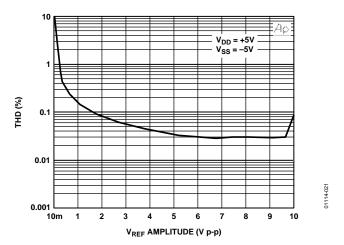

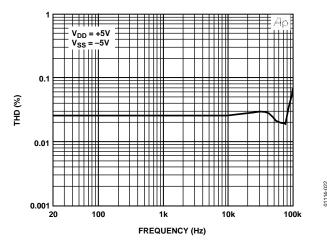

| Total Harmonic Distortion                          | THD                                | $V_{REF} = 4 \text{ V p-p, } V_{SS} = -5 \text{ V, } f = 1 \text{ kHz}$ |                                  |                 | 0.025                            | %           |

| Settling Time <sup>6</sup>                         | ts                                 | To ±0.1% of full scale                                                  | 1.1/2                            | 1.0/2           | 1.0/2                            | μs typ/max  |

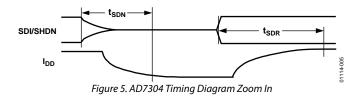

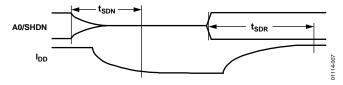

| Shutdown Recovery Time                             | t <sub>SDR</sub>                   | To ±0.1% of full scale                                                  | 2                                | 2               | 2                                | μs max      |

| Time to Shutdown                                   | t <sub>SDN</sub>                   |                                                                         | 15                               | 15              | 15                               | μs typ      |

| DAC Glitch                                         | Q                                  |                                                                         | 15                               | 15              | 15                               | nVs typ     |

| Digital Feedthrough                                | Q                                  |                                                                         | 2                                | 2               | 2                                | nVs typ     |

| Feedthrough                                        | V <sub>OUT</sub> /V <sub>REF</sub> | Code = $0x00$ , $V_{REF} = 1 \text{ V p-p}$ , $f = 100 \text{ kHz}$     |                                  |                 | -65                              | dB          |

| SUPPLY CHARACTERISTICS                             |                                    |                                                                         |                                  |                 |                                  |             |

| Positive Supply Current                            | I <sub>DD</sub>                    | $V_{LOGIC} = 0 \text{ V or } V_{DD}$ , no load                          | 6                                | 6               | 6                                | mA max      |

| Negative Supply Current                            | Iss                                | $V_{SS} = -5 \text{ V}$                                                 |                                  |                 | 6                                | mA max      |

| Power Dissipation                                  | P <sub>DISS</sub>                  | $V_{LOGIC} = 0 \text{ V or } V_{DD}$ , no load                          | 15                               | 30              | 60                               | mW max      |

| Power Down                                         | I <sub>DD_SD</sub>                 | SDI/SHDN = floating                                                     | 40                               | 40              | 40                               | μA typ      |

| Power Supply Sensitivity                           | PSS                                | $\Delta V_{DD} = \pm 10\%$                                              | 0.004                            | 0.004           | 0.004                            | %/%         |

$<sup>^{1}</sup>$  One LSB =  $V_{REF}/256$ .

$<sup>^2</sup>$  The first three codes (0x00, 0x01, 0x10) are excluded from the integral nonlinearity error measurement in single-supply operation 3 V or 5 V.

$<sup>^{\</sup>rm 3}$  These parameters are guaranteed by design and not subject to production testing.

<sup>&</sup>lt;sup>4</sup> Typical specifications represent average readings measured at 25°C.

$<sup>^5</sup>$  The SDI/SHDN and A0/SHDN pins have a 30  $\mu A$  maximum  $I_{\rm L}$  input leakage current.

<sup>&</sup>lt;sup>6</sup> The settling time specification does not apply for negative going transitions within the last three LSBs of ground in single-supply operation.

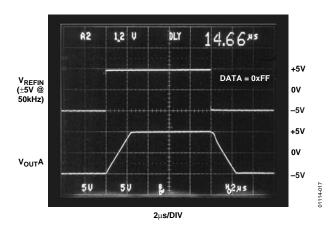

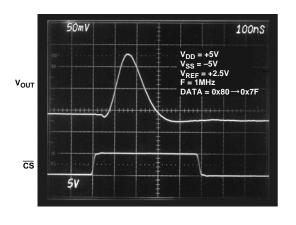

Figure 3. Rail-to-Rail Reference Input to Output at 20 kHz

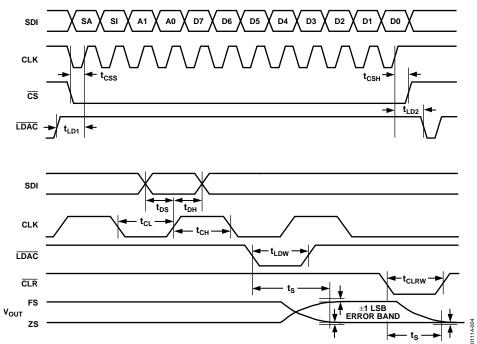

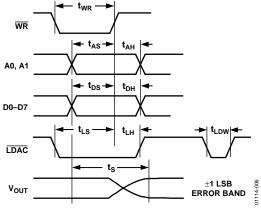

### **TIMING SPECIFICATIONS**

@  $V_{DD} = 3 \text{ V or 5 V}$ ,  $V_{SS} = 0 \text{ V}$ ; or  $V_{DD} = +5 \text{ V}$  and  $V_{SS} = -5 \text{ V}$ ,  $V_{SS} \le V_{REF} \le V_{DD}$ ,  $-40^{\circ}C < T_A < +85^{\circ}C/+125^{\circ}C$ , unless otherwise noted.

Table 2.

| Parameter                                       | Symbol            | 3 V ± 10% | 5 V ± 10% | ±5 V ± 10% | Unit   |

|-------------------------------------------------|-------------------|-----------|-----------|------------|--------|

| INTERFACE TIMING SPECIFICATIONS <sup>1, 2</sup> |                   |           |           |            |        |

| AD7304 Only                                     |                   |           |           |            |        |

| Clock Width High                                | tсн               | 70        | 55        | 55         | ns min |

| Clock Width Low                                 | t <sub>CL</sub>   | 70        | 55        | 55         | ns min |

| Data Setup                                      | t <sub>DS</sub>   | 50        | 40        | 40         | ns min |

| Data Hold                                       | t <sub>DH</sub>   | 30        | 20        | 20         | ns min |

| Load Pulse Width                                | t <sub>LDW</sub>  | 70        | 60        | 60         | ns min |

| Load Setup                                      | t <sub>LD1</sub>  | 40        | 30        | 30         | ns min |

| Load Hold                                       | t <sub>LD2</sub>  | 40        | 30        | 30         | ns min |

| Clear Pulse Width                               | t <sub>CLWR</sub> | 60        | 60        | 60         | ns min |

| Select                                          | t <sub>CSS</sub>  | 30        | 20        | 20         | ns min |

| Deselect                                        | t <sub>CSH</sub>  | 60        | 40        | 40         | ns min |

| AD7305 Only                                     |                   |           |           |            |        |

| Data Setup                                      | t <sub>DS</sub>   | 60        | 40        | 40         | ns min |

| Data Hold                                       | t <sub>DH</sub>   | 30        | 20        | 20         | ns min |

| Address Setup                                   | t <sub>AS</sub>   | 60        | 40        | 40         | ns min |

| Address Hold                                    | t <sub>AH</sub>   | 30        | 20        | 20         | ns min |

| Write Width                                     | twR               | 60        | 50        | 50         | ns min |

| Load Pulse Width                                | t <sub>LDW</sub>  | 60        | 50        | 50         | ns min |

| Load Setup                                      | t <sub>LS</sub>   | 60        | 40        | 40         | ns min |

| Load Hold                                       | t <sub>LH</sub>   | 30        | 20        | 20         | ns min |

$<sup>^1</sup>$  These parameters are guaranteed by design and not subject to production testing.  $^2$  All input control signals are specified with  $t_{\text{R}}=t_{\text{F}}=2$  ns (10% to 90% of  $V_{\text{DD}}$ ) and timed from a voltage level of 1.6 V.

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Table 3.                                           |                                          |

|----------------------------------------------------|------------------------------------------|

| Parameter                                          | Rating                                   |

| V <sub>DD</sub> to GND                             | −0.3 V, +8 V                             |

| V <sub>SS</sub> to GND                             | +0.3 V, -8 V                             |

| V <sub>REFX</sub> to GND                           | V <sub>SS</sub> , V <sub>DD</sub>        |

| Logic Inputs to GND                                | $-0.3 \text{ V, V}_{DD} + 0.3 \text{ V}$ |

| V <sub>OUTX</sub> to GND                           | $-0.3 \text{ V, V}_{DD} + 0.3 \text{ V}$ |

| I <sub>OUT</sub> Short-Circuit to GND              | 50 mA                                    |

| Package Power Dissipation                          | $(T_{J MAX} - T_{A})/\theta_{JA}$        |

| Thermal Resistance $\theta_{JA}$                   |                                          |

| 16-Lead SOIC Package (R-16)                        | 73°C/W                                   |

| 16-Lead TSSOP Package (RU-16)                      | 180°C/W                                  |

| 20-Lead SOIC Package (R-20)                        | 74°C/W                                   |

| 20-Lead TSSOP Package (RU-20)                      | 155°C/W                                  |

| Maximum Junction Temperature (T <sub>J MAX</sub> ) | 150°C                                    |

| Operating Temperature Range                        | −40°C to +85°C                           |

| Storage Temperature Range                          | −65°C to +150°C                          |

| Lead Temperature                                   |                                          |

| R-16, R-20, RU-16, RU-20 (Vapor Phase, 60 sec)     | 235°C                                    |

| R-16, R-20, RU-16, RU-20 (Infrared, 15 sec)        | 220°C                                    |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

Figure 4. AD7304 General Timing Diagram

Table 4. AD7304 Control Logic Truth Table

| CS 1 | CLK <sup>1</sup> | LDAC | CLR <sup>1</sup> | Serial Shift Register Function | Input REG Function                    | DAC Register Function                                |

|------|------------------|------|------------------|--------------------------------|---------------------------------------|------------------------------------------------------|

| Н    | Х                | Н    | Н                | No effect                      | No effect                             | No effect                                            |

| L    | <b>↑</b> +       | Н    | Н                | Data advanced 1 bit            | No effect                             | No effect                                            |

| ↑+   | L                | Н    | Н                | No effect                      | Updated with SR contents <sup>2</sup> | No effect                                            |

| Н    | Х                | L    | Н                | No effect                      | Latched with SR contents <sup>2</sup> | All input register contents transferred <sup>3</sup> |

| Н    | Х                | Н    | ↓-               | No effect                      | Loaded with 0x00                      | Loaded with 0x00                                     |

| Н    | Χ                | Н    | <b>↑</b> +       | No effect                      | Latched with 0x00                     | Latched with 0x00                                    |

$<sup>^1\</sup>uparrow +$  positive logic transition;  $\downarrow -$  negative logic transition; X Don't Care.

<sup>3</sup> LDAC is a level-sensitive input.

Table 5. AD7304 Serial Input Register Data Format, Data is Loaded in MSB-First Format

|        | MSB<br>B11 | B10 | В9 | B8 | B7 | В6 | B5 | B4 | В3 | B2 | B1 | LSB<br>B0 |

|--------|------------|-----|----|----|----|----|----|----|----|----|----|-----------|

| AD7304 | SAC        | SDC | A1 | A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0        |

If B11 (SAC), *Shutdown All Channels*, is set to logic low, all DACs are placed in a power shutdown mode, and all output voltages become high resistance. If B10 (SDC), *Shutdown Decoded Channel*, is set to logic low, only the DAC decoded by Address Bits A1 and A0 is placed in shutdown mode.

<sup>&</sup>lt;sup>2</sup> One input register receives the data bits D7-D0 decoded from the SR address bits (A1, A0), where REG A = (0, 0), B = (0, 1), C = (1, 0), and D = (1, 1).

Table 6. AD7305 Control Logic Truth Table

| WR 1       | <b>A1</b> | A0 | LDAC <sup>2</sup> | Input Register Function                    | DAC Register Function                                    |

|------------|-----------|----|-------------------|--------------------------------------------|----------------------------------------------------------|

| L          | L         | L  | Н                 | Register A loaded with DB0 to DB7          | Latched with previous contents, no change                |

| <b>↑</b> + | L         | L  | Н                 | Register A latched with DB0 to DB7         | Latched with previous contents, no change                |

| L          | L         | Н  | Н                 | Register B loaded with DB0 to DB7          | Latched with previous contents, no change                |

| <b>↑</b> + | L         | Н  | Н                 | Register B latched with DB0 to DB7         | Latched with previous contents, no change                |

| L          | Н         | L  | Н                 | Register C loaded with DB0 to DB7          | Latched with previous contents, no change                |

| <b>↑</b> + | Н         | L  | Н                 | Register C latched with DB0 to DB7         | Latched with previous contents, no change                |

| L          | Н         | Н  | Н                 | Register D loaded with DB0 to DB7          | Latched with previous contents, no change                |

| <b>†</b> + | Н         | Н  | Н                 | Register D latched with DB0 to DB7         | Latched with previous contents, no change                |

| Н          | Χ         | Χ  | L                 | No effect                                  | All input register contents loaded, register transparent |

| L          | Χ         | Χ  | L                 | Input register x transparent to DB0 to DB7 | Register transparent                                     |

| Н          | Χ         | Χ  | <b>↑</b> +        | No effect                                  | All input register contents latched                      |

| Н          | Χ         | Χ  | Н                 | No effect, device not selected             | No effect, device not selected                           |

Figure 6. AD7305 General Timing Diagram

Figure 7. AD7305 Timing Diagram Zoom In

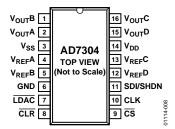

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 8. AD7304 Pin Configuration

**Table 7. AD7304 Pin Function Descriptions**

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                                         |

|---------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>оит</sub> В | Channel B Rail-to-Rail Buffered DAC Voltage Output. Full-scale set by reference voltage applied to VREFB pin. Output is open circuit when SHDN is enabled.                                                                                                          |

| 2       | V <sub>OUT</sub> A | Channel A Rail-to-Rail Buffered DAC Voltage Output. Full-scale set by reference voltage applied to V <sub>REF</sub> A pin. Output is open circuit when SHDN is enabled.                                                                                             |

| 3       | Vss                | Negative Power Supply Input. Specified range of operation is 0 V to −5.5 V.                                                                                                                                                                                         |

| 4       | $V_{REF}A$         | Channel A Reference Input. Establishes $V_{OUT}A$ full-scale voltage. Specified range of operation is $V_{SS} < V_{REF}A < V_{DD}$                                                                                                                                  |

| 5       | $V_{REF}B$         | Channel B Reference Input. Establishes $V_{OUT}B$ full-scale voltage. Specified range of operation is $V_{SS} < V_{REF}B < V_{DD}$ .                                                                                                                                |

| 6       | GND                | Common Analog and Digital Ground.                                                                                                                                                                                                                                   |

| 7       | LDAC               | Load DAC Register Strobe, Active Low. Simultaneously transfers data from all four input registers into the corresponding DAC registers. Asynchronous active low input. DAC register is transparent when LDAC = 0. See Table 4 for operation.                        |

| 8       | CLR                | Clears All Input and DAC Registers to the Zero Condition. Asynchronous active low input. The serial register is not effected.                                                                                                                                       |

| 9       | <u>cs</u>          | Chip Select, Active Low Input. Disables shift register loading when high. Transfers serial input register data to the decoded input register when CS returns high. Does not effect LDAC operation.                                                                  |

| 10      | CLK                | Clock Input, Positive Edge Clocks Data into Shift Register. Disabled by chip select CS.                                                                                                                                                                             |

| 11      | SDI/SHDN           | Serial Data Input Loads Directly into the Shift Register, MSB First. Hardware shutdown (SHDN) control input, active when pin is left floating by a three-state logic driver. Does not effect DAC register contents as long as power is present on V <sub>DD</sub> . |

| 12      | V <sub>REF</sub> D | Channel D Reference Input. Establishes $V_{OUT}D$ full-scale voltage. Specified range of operation is $V_{SS} < V_{REF}D < V_{DD}$                                                                                                                                  |

| 13      | V <sub>REF</sub> C | Channel C Reference Input. Establishes $V_{OUT}C$ full-scale voltage. Specified range of operation is $V_{SS}$ $V_{REF}C < V_{DD}$ .                                                                                                                                |

| 14      | $V_{DD}$           | Positive Power Supply Input. Specified range of operation is 2.7 V to 5.5 V.                                                                                                                                                                                        |

| 15      | V <sub>OUT</sub> D | Channel D Rail-to-Rail Buffered DAC Voltage Output. Full-scale set by reference voltage applied to VREFD pin. Output is open circuit when SHDN is enabled.                                                                                                          |

| 16      | V <sub>OUT</sub> C | Channel C Rail-to-Rail Buffered DAC Voltage Output. Full-scale set by reference voltage applied to VREFC pin. Output is open circuit when SHDN is enabled.                                                                                                          |

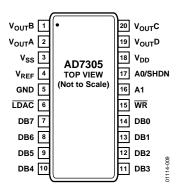

Figure 9. AD7305 Pin Configuration

**Table 8. AD7305 Pin Function Description**

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                                       |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>ОUТ</sub> В | Channel B Rail-to-Rail Buffered DAC Voltage Output. Full-scale set by reference voltage applied to VREFB pin. Output is open circuit when SHDN is enabled.                                                                                                        |

| 2       | V <sub>ОUТ</sub> A | Channel A Rail-to-Rail Buffered DAC Voltage Output. Full-scale set by reference voltage applied to VREFA pin. Output is open circuit when SHDN is enabled.                                                                                                        |

| 3       | V <sub>SS</sub>    | Negative Power Supply Input. Specified range of operation is 0 V to −5.5 V.                                                                                                                                                                                       |

| 4       | $V_{REF}$          | Channel B Reference Input. Establishes $V_{OUT}$ full-scale voltage. Specified range of operation is $V_{SS} < V_{REF} < V_{DD}$ .                                                                                                                                |

| 5       | GND                | Common Analog and Digital Ground.                                                                                                                                                                                                                                 |

| 6       | LDAC               | Load DAC Register Strobe, Active Low. Simultaneously transfers data from all four input registers into the corresponding DAC registers. Asynchronous active low input. DAC register is transparent when $\overline{\text{LDAC}} = 0$ . See Table 6 for operation. |

| 7       | DB7                | MSB Digital Input Data Bit.                                                                                                                                                                                                                                       |

| 8       | DB6                | Data Bit 6.                                                                                                                                                                                                                                                       |

| 9       | DB5                | Data Bit 5.                                                                                                                                                                                                                                                       |

| 10      | DB4                | Data Bit 4.                                                                                                                                                                                                                                                       |

| 11      | DB3                | Data Bit 3.                                                                                                                                                                                                                                                       |

| 12      | DB2                | Data Bit 2.                                                                                                                                                                                                                                                       |

| 13      | DB1                | Data Bit 1.                                                                                                                                                                                                                                                       |

| 14      | DB0                | LSB Digital Input Data Bit.                                                                                                                                                                                                                                       |

| 15      | WR                 | Write Data into Input Register Control Line, Active Low. See Table 6 for operation.                                                                                                                                                                               |

| 16      | A1                 | Address Bit 1.                                                                                                                                                                                                                                                    |

| 17      | A0/SHDN            | Address Bit 0/Hardware Shutdown (SHDN) Control Input, Active When Pin Is Left Floating by a Three-State Logic Driver. Does not effect DAC register contents as long as power is present on V <sub>DD</sub> .                                                      |

| 18      | $V_{DD}$           | Positive Power Supply Input. Specified range of operation is 2.7 V to 5.5 V.                                                                                                                                                                                      |

| 19      | V <sub>OUT</sub> D | Channel D Rail-to-Rail Buffered DAC Voltage Output. Full-scale set by reference voltage applied to VREFD pin. Output is open circuit when SHDN is enabled.                                                                                                        |

| 20      | V <sub>ОUТ</sub> С | Channel C Rail-to-Rail Buffered DAC Voltage Output. Full-scale set by reference voltage applied to VREFC pin. Output is open circuit when SHDN is enabled.                                                                                                        |

### TYPICAL PERFORMANCE CHARACTERISTICS

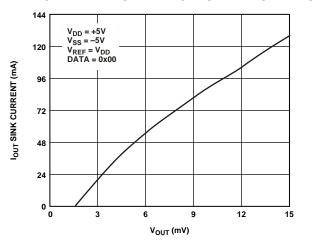

Figure 10. IOUT Sink vs. VOUT Rail-to-Rail Performance

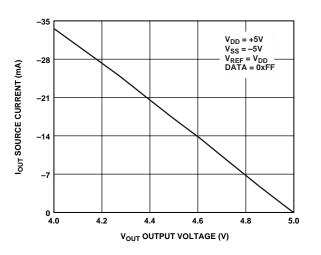

Figure 11. Iout SOURCE vs. Vout Rail-to-Rail Performance

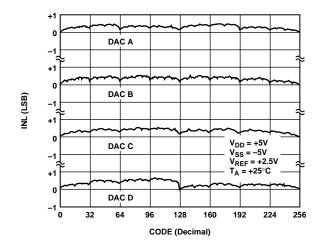

Figure 12. INL vs. Code, All DAC Channels

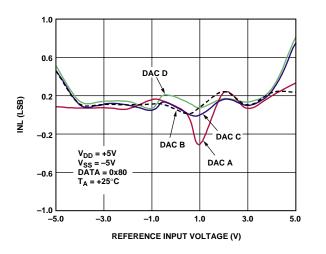

Figure 13. INL vs. Reference Input Voltage

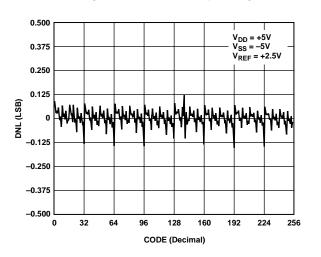

Figure 14. DNL vs. Code

01114-014

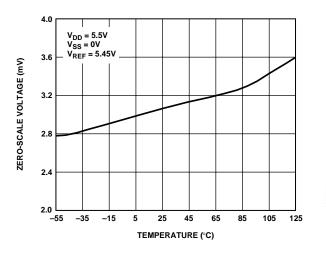

Figure 15. Zero-Scale Voltage vs. Temperature

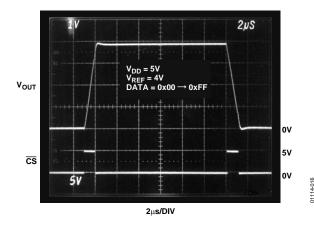

Figure 16. Large-Signal Settling Time

Figure 17. Multiplying Mode Step Response and Output Slew Rate

Figure 18. Multiplying Mode Gain vs. Frequency

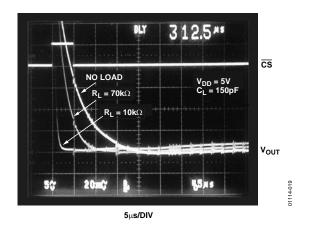

Figure 19. Time to Shutdown

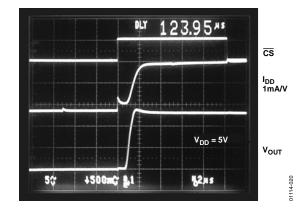

Figure 20. Shutdown Recovery Time (Wakeup)

Figure 21. THD vs. Reference Input Amplitude

Figure 22. THD vs. Frequency

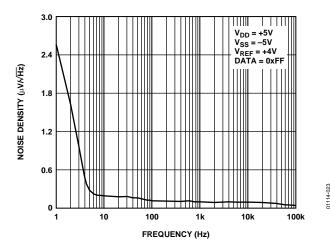

Figure 23. Output Noise Voltage Density vs. Frequency

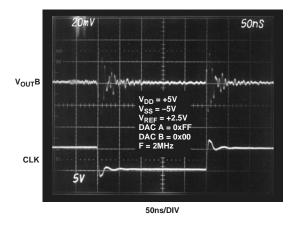

Figure 24. Digital Feedthrough

Figure 25. Midscale Transition Glitch

01114-025

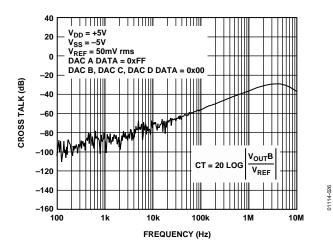

Figure 26. Crosstalk vs. Frequency

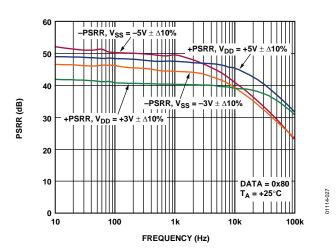

Figure 27. Power-Supply Rejection vs. Frequency

01114-032

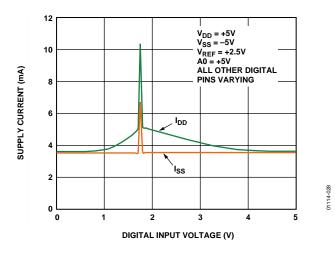

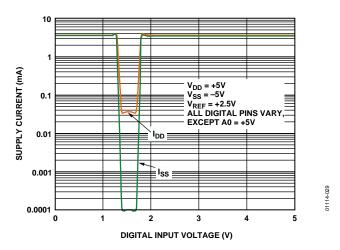

Figure 28. Supply Current vs. Digital Input Voltage

Figure 29. Shutdown Supply Current vs. Digital Input Voltage (A0 Only)

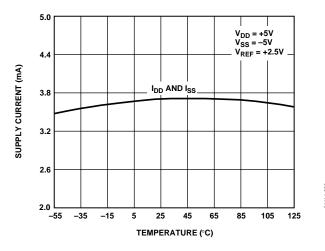

Figure 30. Supply Current vs. Temperature

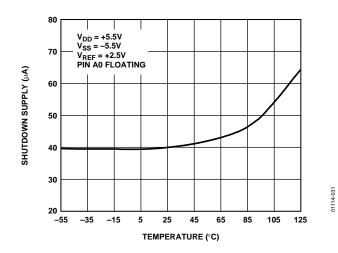

Figure 31. Shutdown Supply Current vs. Temperature

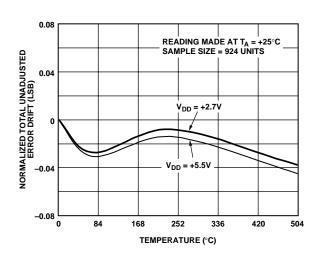

Figure 32. Normalized TUE Drift Accelerated by Burn-In Hours of Operation @ 150°C

### **CIRCUIT OPERATION**

The AD7304/AD7305 are 4-channel, 8-bit, voltage output DACs, differing primarily in digital logic interface and number of reference inputs. Both parts share the same internal DAC design and true rail-to-rail output buffers. The AD7304 contains four independent multiplying reference inputs, while the AD7305 has one common reference input. The AD7304 uses a 3-wire SPI-compatible serial data interface, while the AD7305 offers an 8-bit parallel data interface.

### **DAC SECTION**

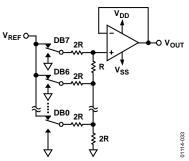

Each part contains four voltage-switched R-2R ladder DACs. Figure 33 shows a typical equivalent DAC. These DACs are designed to operate both single-supply or dual-supply, depending on whether the user supplies a negative voltage on the  $V_{SS}$  pin. In a single-supply application, the  $V_{SS}$  is tied to ground. In either mode, the DAC output voltage is determined by the  $V_{REF}$  input voltage and the digital data (D) loaded into the corresponding DAC register according to Equation 1.

$$V_{OUT} = V_{REF} D/256 \tag{1}$$

Note that the output full-scale polarity is the same as the  $V_{REF}$  polarity for dc reference voltages.

Figure 33. Typical Equivalent DAC Channel

These DACs are also designed to accommodate ac reference input signals. As long as the ac signals are maintained between  $V_{\text{SS}} < V_{\text{REF}} < V_{\text{DD}}$ , the user can expect 50 kHz of full power, multiplying bandwidth performance. In order to use negative input reference voltages, the  $V_{\text{SS}}$  pin must be biased with a negative voltage of equal or greater magnitude than the reference voltage.

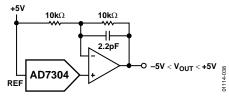

The reference inputs are code dependent, exhibiting worst-case minimum resistance values specified in the parametric specification table. The DAC outputs VoutA, VoutB, VoutC, and VoutD are each capable of driving 2 k $\Omega$  loads in parallel with up to 500 pF loads. Output sink current and source current are shown in Figure 10 and Figure 11, respectively. The output slew rate is nominally 3.6 V/µs while operating from ±5 V supplies. The low output impedance of the buffers minimizes crosstalk between analog input channels. At 100 kHz, 65 dB of channelto-channel isolation exists (Figure 26). Output voltage noise is plotted in Figure 23. In order to maintain good analog performance, power supply bypassing of 0.01 µF in parallel with 1 µF is recommended. The true rail-to-rail capability of the AD7304/AD7305 allows the user to connect the reference inputs directly to the same supply as the  $V_{DD}$  or  $V_{SS}$  pin (Figure 34). Under these conditions, clean power supply voltages (low ripple, avoid switching supplies) appropriate for the application should be used.

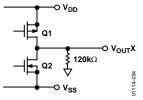

Figure 34. Equivalent DAC Amplifier Output Circuit

### **AD7304 SERIAL DATA INTERFACE**

The AD7304 uses a 3-wire ( $\overline{\text{CS}}$ , SDI, CLK) SPI-compatible serial data interface. New serial data is clocked into the serial input register in a 12-bit data-word format. MSB bits are loaded first.

Table 5 defines the 12 data-word bits. Data is placed on the SDI/SHDN pin and clocked into the register on the positive clock edge of CLK subject to the data setup and data hold time requirements specified in the Timing Specifications section. Data can only be clocked in while the  $\overline{\text{CS}}$  chip select pin is active low. Only the last 12-bits clocked into the serial register are interrogated when the  $\overline{\text{CS}}$  pin returns to the logic high state, extra data bits are ignored. Since most microcontrollers output serial data in 8-bit bytes, two right-justified data bytes can be written to the AD7304. Keeping the  $\overline{\text{CS}}$  line low between the first and second byte transfer results in a successful serial register update.

Once the data is properly aligned in the shift register, the positive edge of the CS initiates either the transfer of new data to the target DAC register, determined by the decoding of Address Bits A1 and A0, or the shutdown features is activated based on the SAC or SDC bits. When either SAC or SDC pins are set (Logic 0), the loading of new data determined by Bits B9 to B0 are still loaded, but the results do not appear on the buffer outputs until the device is brought out of the shutdown state. The selected DAC output voltages become high impedance with a nominal resistance of 120 k $\Omega$  to ground, see Figure 34. If both the SAC and SDC pins are set, all channels are still placed in shutdown mode. When the AD7304 has been programmed into the power shutdown state, the present DAC register data is maintained as long as  $V_{DD}$  remains greater than 2.7 V. The remaining characteristics of the software serial interface are defined by Table 4, Table 5, and Figure 5.

Two additional pins,  $\overline{CLR}$  and  $\overline{LDAC}$ , on the AD7304 provide hardware control over the clear function and the DAC register loading. If these functions are not needed, the  $\overline{CLR}$  pin can be tied to logic high, and the  $\overline{LDAC}$  pin can be tied to logic low. The asynchronous input  $\overline{CLR}$  pin forces all input and DAC registers to the zero-code state. The asynchronous  $\overline{LDAC}$  pin can be strobed to active low when all DAC registers need to be updated simultaneously from their respective input registers.

The LDAC pin places the DAC register in a transparent mode while in the logic low state.

Figure 35. AD7304 Equivalent Logic Interface

### **AD7304 HARDWARE SHUTDOWN SHDN**

If a three-state driver is used on the SDI/SHDN pin, the AD7304 can be placed into a power shutdown mode when the SDI/ SHDN pin is placed in a high impedance state. For proper operation, no other termination voltages should be present on this pin. An internal window comparator detects when the logic voltage on the SHDN pin is between 28% and 36% of  $V_{\rm DD}.$  A high impedance internal bias generator provides this voltage on the SHDN pin. The four DAC output voltages become high impedance with a nominal resistance of 120  $k\Omega$  to ground (see Figure 34 for an equivalent circuit).

#### AD7304/AD7305 POWER-ON RESET

When the  $V_{\rm DD}$  power supply is turned on, an internal reset strobe forces all the input and DAC registers to the zero-code state. The  $V_{\rm DD}$  power supply should have a monotonically increasing ramp in order to have consistent results, especially in the region of  $V_{\rm DD}=1.5~V$  to 2.3 V. The  $V_{SS}$  supply has no effect on the power-on reset performance. The DAC register data stays at zero until a valid serial register software load takes place. In the case of the double-buffered AD7305, the output DAC register can only be changed once the  $\overline{LDAC}$  strobe is initiated.

### **POWER-UP SEQUENCE**

It is recommended to power  $V_{\rm DD}/V_{\rm SS}$  first before applying any voltage to the reference terminals to avoid potential latch up. The ideal power-up sequence is in the following order: GND,  $V_{\rm DD}$ ,  $V_{\rm SS}$ , Digital Inputs, and  $V_{\rm REFx}$ . The order of powering digital inputs and reference inputs is not important as long as they are powered after  $V_{\rm DD}/V_{\rm SS}$ .

### AD7305 PARALLEL DATA INTERFACE

The AD7305 has an 8-bit parallel interface DB7 = MSB, DB0 = LSB. Two address bits, A1 and A0, are decoded when an active low write strobe is placed on the  $\overline{WR}$  pin, see Table 6. The  $\overline{WR}$  is a level-sensitive input pin, therefore, the data setup and data hold times defined in the Timing Specifications section need to be adhered to.

Figure 36. AD7305 Equivalent Logic Interface

The  $\overline{\text{LDAC}}$  pin provides the capability of simultaneously updating all DAC registers with new data from the input registers at the same time. This results in the analog outputs all changing to their new values at the same time. The  $\overline{\text{LDAC}}$  pin is a level-sensitive input. If the simultaneous update feature is not required, the  $\overline{\text{LDAC}}$  pin can be tied to logic low. When the

LDAC is tied to Logic Low, the DAC registers become transparent and the input register data determines the DAC output voltage (see Figure 36 for an equivalent interface logic diagram).

#### **AD7226 PIN COMPATIBILITY**

By tying the  $\overline{\text{LDAC}}$  pin to ground, the AD7305 has the same pin configuration and functionality as the AD7226, with the exception of a lower power supply operating voltage.

#### **AD7305 HARDWARE SHUTDOWN SHDN**

If a three-state driver is used on the A0/SHDN pin, the AD7305 can be placed into a power shutdown mode when the A0/SHDN pin is placed in a high impedance state. For proper operation, no other termination voltages should be present on this pin. An internal window comparator detects when the logic voltage on the SHDN pin is between 28% and 36% of  $V_{\rm DD}$ . A high impedance, internal-bias generator provides this voltage on the SHDN pin. The four DAC output voltages become high impedance with a nominal resistance of 120  $k\Omega$  to ground.

### **ESD PROTECTION CIRCUITS**

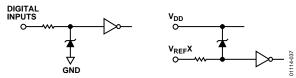

All logic input pins contain back-biased ESD protection Zeners connected to ground (GND). The  $V_{\text{REF}}$  pins also contain a back-biased ESD protection Zener connected to  $V_{\text{DD}}$  (see Figure 37).

Figure 37. Equivalent ESD Protection Circuits

### **APPLICATIONS**

The AD7304/AD7305 are inherently 2-quadrant multiplying DACs. That is, they can easily be set up for unipolar output operation. The full-scale output polarity is the same as the reference input voltage polarity.

In some applications, it may be necessary to generate the full 4-quadrant multiplying capability or a bipolar output swing. This is easily accomplished using an external true rail-to-rail op amp, such as the OP295. Connecting the external amplifier with two equal value resistors, as shown in Figure 38, results in a full 4-quadrant multiplying circuit. In this circuit, the amplifier provides a gain of two, which increases the output span magnitude to 10 V. The transfer equation of this circuit shows that both negative and positive output voltages are created as

the input data (D) is incremented from code zero ( $V_{\rm OUT}$  = -5 V) to midscale ( $V_{\rm OUT}$  = 0 V) to full scale ( $V_{\rm OUT}$  = +5 V).

$$V_{OUT} = \frac{D}{128 - 1} \times V_{REF} \tag{2}$$

Figure 38. 4-Quadrant Multiplying Application Circuit

### **OUTLINE DIMENSIONS**

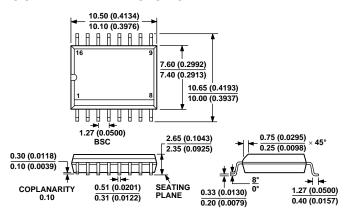

**COMPLIANT TO JEDEC STANDARDS MS-013AA** CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

Figure 39. 16-Lead Standard Small Outline Package [SOIC] Wide Body (R-16) Dimensions shown in millimeters and (inches)

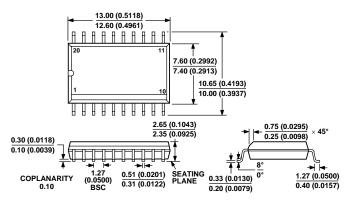

COMPLIANT TO JEDEC STANDARDS MS-013AC CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

Figure 40. 20-Lead Standard Small Outline Package [SOIC] Wide Body (R-20) Dimensions shown in millimeters and (inches)

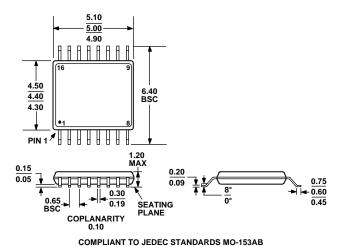

Figure 41. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters

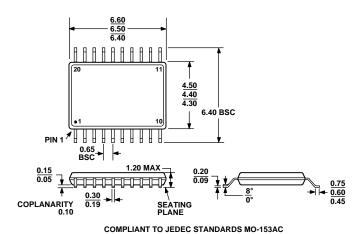

Figure 42. 20-Lead Thin Shrink Small Outline Package [TSSOP]

(RU-20) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                         | Temperature Range | Package Description | Package Options |

|-------------------------------|-------------------|---------------------|-----------------|

| AD7304BR                      | -40°C to +85°C    | 16-Lead SOIC        | R-16            |

| AD7304BR-REEL                 | -40°C to +85°C    | 16-Lead SOIC        | R-16            |

| AD7304BRZ <sup>1</sup>        | -40°C to +85°C    | 16-Lead SOIC        | R-16            |

| AD7304BRZ-REEL <sup>1</sup>   | -40°C to +85°C    | 16-Lead SOIC        | R-16            |

| AD7304YR                      | -40°C to +125°C   | 16-Lead SOIC        | R-16            |

| AD7304YRZ <sup>1</sup>        | -40°C to +125°C   | 16-Lead SOIC        | R-16            |

| AD7304BRU                     | -40°C to +85°C    | 16-Lead TSSOP       | RU-16           |

| AD7304BRU-REEL7               | -40°C to +85°C    | 16-Lead TSSOP       | RU-16           |

| AD7305BR                      | -40°C to +85°C    | 20-Lead SOIC        | R-20            |

| AD7305BR-REEL                 | -40°C to +85°C    | 20-Lead SOIC        | R-20            |

| AD7305YR                      | -40°C to +125°C   | 20-Lead SOIC        | R-20            |

| AD7305YR-REEL                 | -40°C to +125°C   | 20-Lead SOIC        | R-20            |

| AD7305BRU                     | -40°C to +85°C    | 20-Lead TSSOP       | RU-20           |

| AD7305BRU-REEL7               | -40°C to +85°C    | 20-Lead TSSOP       | RU-20           |

| AD7305BRUZ <sup>1</sup>       | -40°C to +85°C    | 20-Lead TSSOP       | RU-20           |

| AD7305BRUZ-REEL7 <sup>1</sup> | -40°C to +85°C    | 20-Lead TSSOP       | RU-20           |

$<sup>^{1}</sup>$  Z = Pb-free part.

| AD7304/AD7305 |  |  |

|---------------|--|--|

|---------------|--|--|

## **NOTES**