# Dual Picoampere Input Current Bipolar Op Amp

Data Sheet AD706

FEATURES

High DC Precision

100 μV Max Offset Voltage

1.5 μV/°C Max Offset Drift

200 pA Max Input Bias Current

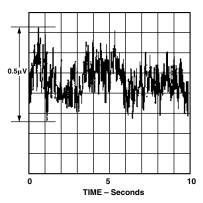

0.5 μV p-p Voltage Noise, 0.1 Hz to 10 Hz

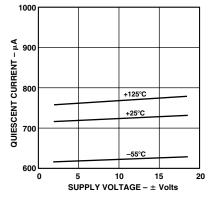

750 μA Supply Current

Available in 8-Lead PDIP

and Surface-Mount (SOIC) Packages

Available in Tape and Reel in Accordance with

EIA-481A Standard

Quad Version: AD704

APPLICATIONS

Low Frequency Active Filters

Precision Instrumentation

Precision Integrators

#### GENERAL DESCRIPTION

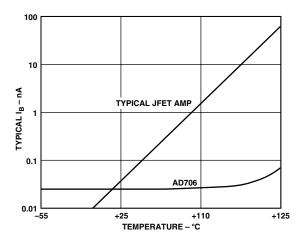

The AD706 is a dual, low power, bipolar op amp that has the low input bias current of a JFET amplifier, but which offers a significantly lower  $I_B$  drift over temperature. It utilizes superbeta bipolar input transistors to achieve picoampere input bias current levels (similar to FET input amplifiers at room temperature), while its  $I_B$  typically only increases by  $5\times$  at  $125^{\circ}$ C (unlike a JFET amp, for which  $I_B$  doubles every  $10^{\circ}$ C for a  $1000\times$  increase at  $125^{\circ}$ C). The AD706 also achieves the microvolt offset voltage and low noise characteristics of a precision bipolar input amplifier.

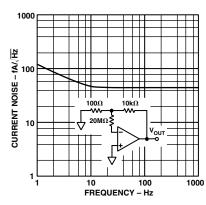

Since it has < 200 pA of bias current, the AD706 does not require the commonly used "balancing" resistor. Furthermore, the current noise is only 50 fA/ $\sqrt{\text{Hz}}$ , which makes this amplifier usable with very high source impedances. At 600  $\mu$ A max supply current (per amplifier), the AD706 is well suited for today's high density boards.

The AD706 is an excellent choice for use in low frequency active filters in 12-bit and 14-bit data acquisition systems, in precision instrumentation, and as a high quality integrator. The AD706 is internally compensated for unity gain and is available in five performance grades. The AD706J is rated over the commercial temperature range of 0°C to +70°C. The AD706A is rated for the extended industrial temperature range of -40°C to +85°C.

The AD706 is offered in two varieties of an 8-lead package: PDIP and surface-mount (SOIC).

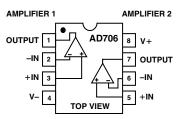

# CONNECTION DIAGRAM PDIP (N) and Plastic SOIC (R) Packages

#### PRODUCT HIGHLIGHTS

- 1. The AD706 is a dual low drift op amp that offers JFET level input bias currents, yet has the low  $I_B$  drift of a bipolar amplifier. It may be used in circuits using dual op amps such as the LT1024.

- 2. The AD706 provides both low drift and high dc precision.

- 3. The AD706 can be used in applications where a chopper amplifier would normally be required but without the chopper's inherent noise.

Figure 1. Input Bias Current vs. Temperature

Rev. G

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2002–2018 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# $\label{eq:AD706-SPECIFICATIONS} \textbf{(@ $T_A = +25^{\circ}$C$, $V_{CM} = 0$ V and $\pm 15$ V dc, unless otherwise noted.)}$

| Parameter                                                                                                                                                                                                             | Conditions                                                                                                                                                                                                                                 | s AD700<br>Min Typ       |                                      |                                                      | Unit                                                     |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------|------------------------------------------------------|----------------------------------------------------------|--|

| INPUT OFFSET VOLTAGE Initial Offset Offset vs. Temperature, Average TC vs. Supply (PSRR) T <sub>MIN</sub> to T <sub>MAX</sub> Long Term Stability                                                                     | $T_{MIN}$ to $T_{MAX}$<br>$V_S = \pm 2 \text{ V to } \pm 18 \text{ V}$<br>$V_S = \pm 2.5 \text{ V to } \pm 18 \text{ V}$                                                                                                                   | 110<br>106               | 30<br>40<br>0.2<br>132<br>126<br>0.3 | 100<br>150<br>1.5                                    | μV<br>μV<br>μV/°C<br>dB<br>dB<br>μV/Month                |  |

| INPUT BIAS CURRENT¹  vs. Temperature, Average TC $T_{MIN}$ to $T_{MAX}$ $T_{MIN}$ to $T_{MAX}$ INPUT OFFSET CURRENT  vs. Temperature, Average TC $T_{MIN}$ to $T_{MAX}$ $T_{MIN}$ to $T_{MAX}$ $T_{MIN}$ to $T_{MAX}$ | $V_{CM} = 0 \text{ V}$ $V_{CM} = \pm 13.5 \text{ V}$ $V_{CM} = 0 \text{ V}$ $V_{CM} = \pm 13.5 \text{ V}$ $V_{CM} = \pm 13.5 \text{ V}$ $V_{CM} = 0 \text{ V}$ $V_{CM} = 0 \text{ V}$ $V_{CM} = 0 \text{ V}$ $V_{CM} = \pm 13.5 \text{ V}$ |                          | 50<br>0.3<br>30<br>0.6<br>80<br>80   | 200<br>250<br>300<br>400<br>150<br>250<br>250<br>350 | pA<br>pA<br>pA/°C<br>pA<br>pA<br>pA<br>pA/°C<br>pA       |  |

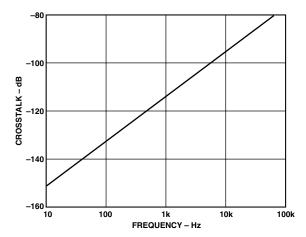

| MATCHING CHARACTERISTICS Offset Voltage Input Bias Current <sup>2</sup> Common-Mode Rejection Power Supply Rejection Crosstalk (Figure 2a)                                                                            | $T_{MIN}$ to $T_{MAX}$ $T_{MIN}$ to $T_{MAX}$ $T_{MIN}$ to $T_{MAX}$ $T_{MIN}$ to $T_{MAX}$ $@ f = 10 \text{ Hz}$ $R_L = 2 \text{ k}\Omega$                                                                                                | 106<br>106<br>106<br>104 | 150                                  | 150<br>250<br>300<br>500                             | μV<br>μV<br>pA<br>pA<br>dB<br>dB<br>dB<br>dB             |  |

| FREQUENCY RESPONSE Unity Gain Crossover Frequency Slew Rate                                                                                                                                                           | $G = -1$ $T_{MIN}$ to $T_{MAX}$                                                                                                                                                                                                            |                          | 0.8<br>0.15<br>0.15                  |                                                      | MHz<br>V/μs<br>V/μs                                      |  |

| INPUT IMPEDANCE Differential Common Mode                                                                                                                                                                              |                                                                                                                                                                                                                                            |                          | 40  2<br>300  2                      |                                                      | MΩ  pF<br>GΩ  pF                                         |  |

| INPUT VOLTAGE RANGE Common-Mode Voltage Common-Mode Rejection Ratio  INPUT CURRENT NOISE                                                                                                                              | $V_{CM} = \pm 13.5 \text{ V}$ $T_{MIN} \text{ to } T_{MAX}$ $0.1 \text{ Hz to } 10 \text{ Hz}$                                                                                                                                             | ±13.5<br>110<br>108      | ±14<br>132<br>128                    |                                                      | V<br>dB<br>dB                                            |  |

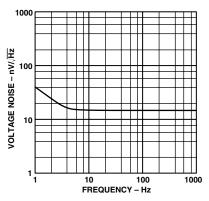

| INPUT VOLTAGE NOISE                                                                                                                                                                                                   | f = 10 Hz<br>0.1 Hz to 10 Hz<br>f = 10 Hz<br>f = 1 kHz                                                                                                                                                                                     |                          | 50<br>0.5<br>17<br>15                | 22                                                   | $fA/\sqrt{Hz}$ $\mu V p-p$ $nV/\sqrt{Hz}$ $nV/\sqrt{Hz}$ |  |

| OPEN-LOOP GAIN                                                                                                                                                                                                        | $V_{O} = \pm 12 \text{ V}$ $R_{LOAD} = 10 \text{ k}\Omega$ $T_{MIN} \text{ to } T_{MAX}$ $V_{O} = \pm 10 \text{ V}$ $R_{LOAD} = 2 \text{ k}\Omega$ $T_{MIN} \text{ to } T_{MAX}$                                                           | 200<br>150<br>200<br>150 | 2000<br>1500<br>1000<br>1000         |                                                      | V/mV<br>V/mV<br>V/mV<br>V/mV                             |  |

| OUTPUT CHARACTERISTICS Voltage Swing  Current Capacitive Load Drive Capability                                                                                                                                        | $R_{LOAD} = 10 \text{ k}\Omega$ $T_{MIN}$ to $T_{MAX}$ Short Circuit $Gain = +1$                                                                                                                                                           | ±13<br>±13               | ±14<br>±14<br>±15<br>10,000          |                                                      | V<br>V<br>mA<br>pF                                       |  |

-2- REV. G

# SPECIFICATIONS (continued)

| Parameter                                                               | Conditions                           | Min  | AD706J/A<br>Typ | Max               | Unit               |

|-------------------------------------------------------------------------|--------------------------------------|------|-----------------|-------------------|--------------------|

| POWER SUPPLY Rated Performance Operating Range Quiescent Current, Total | T <sub>MIN</sub> to T <sub>MAX</sub> | ±2.0 | ±15 0.75 0.8    | ±18<br>1.2<br>1.4 | V<br>V<br>mA<br>mA |

| TRANSISTOR COUNT                                                        | Number of Transistors                |      | 90              |                   |                    |

#### NOTES

<sup>1</sup>Bias current specifications are guaranteed maximum at either input.

$^2$ Input bias current match is the difference between corresponding inputs (I $_B$  of –IN of Amplifier 1 minus I $_B$  of –IN of Amplifier 2).

CMRR match is the difference between  $\frac{\Delta V_{OS1}}{\Delta V_{CM}}$  for Amplifier 1 and  $\frac{\Delta V_{OS2}}{\Delta V_{CM}}$  for Amplifier 2, expressed in dB.

PSRR match is the difference between  $\frac{\Delta V_{OSI}}{\Delta V_{SUPPLY}}$  for Amplifier 1 and  $\frac{\Delta V_{OS2}}{\Delta V_{SUPPLY}}$  for Amplifier 2, expressed in dB.

All min and max specifications are guaranteed. Specifications subject to change without notice.

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| Supply Voltage                                 |

|------------------------------------------------|

| Internal Power Dissipation                     |

| (Total: Both Amplifiers) <sup>2</sup> 650 mW   |

| Input Voltage                                  |

| Differential Input Voltage <sup>3</sup> +0.7 V |

| Output Short Circuit Duration Indefinite       |

| Storage Temperature Range (N, R)65°C to +125°C |

| Operating Temperature Range                    |

| AD706J 0°C to +70°C                            |

| AD706A                                         |

| Lead Temperature (Soldering 10 secs) 300°C     |

#### NOTES

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

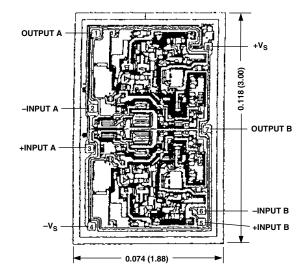

#### METALIZATION PHOTOGRAPH

Dimensions shown in inches and (mm). Contact factory for latest dimensions.

REV. G -3-

<sup>&</sup>lt;sup>2</sup>Specification is for device in free air:

<sup>8-</sup>Lead PDIP Package:  $\theta_{JA} = 100^{\circ}$ C/W

<sup>8-</sup>Lead Small Outline Package:  $\theta_{JA} = 155^{\circ}\text{C/W}$

$<sup>^3</sup>$ The input pins of this amplifier are protected by back-to-back diodes. If the differential voltage exceeds  $\pm 0.7$  V, external series protection resistors should be added to limit the input current to less than 25 mA.

# **AD706—Typical Performance Characteristics**

(Default Conditions:  $\pm 5$  V,  $C_L = 5$  pF, G = 2,  $R_g = R_f = 1$  k $\Omega$ ,  $R_L = 2$  k $\Omega$ ,  $V_O = 2$  V p-p, Frequency = 1 MHz,  $T_A = 25^{\circ}$ C)

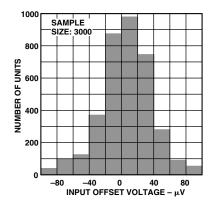

TPC 1. Typical Distribution of Input Offset Voltage

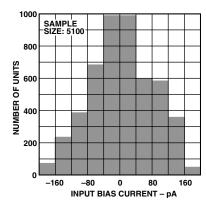

TPC 2. Typical Distribution of Input Bias Current

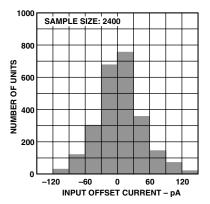

TPC 3. Typical Distribution of Input Offset Current

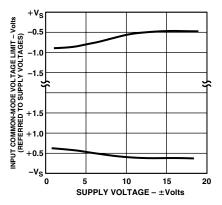

TPC 4. Input Common-Mode Voltage Range vs. Supply Voltage

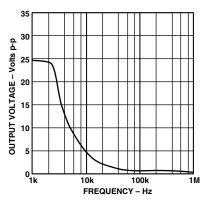

TPC 5. Large Signal Frequency Response

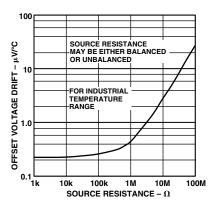

TPC 6. Offset Voltage Drift vs. Source Resistance

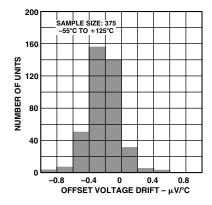

TPC 7. Typical Distribution of Offset Voltage Drift

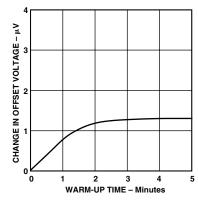

TPC 8. Change in Input Offset Voltage vs. Warm-Up Time

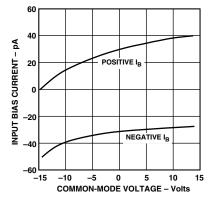

TPC 9. Input Bias Current vs. Common-Mode Voltage

-4- REV. G

### **AD706**

TPC 10. Input Noise Voltage Spectral Density

TPC 11. Input Noise Current Spectral Density

TPC 12. 0.1 Hz to 10 Hz Noise Voltage

TPC 13. Quiescent Supply Current vs. Supply Voltage

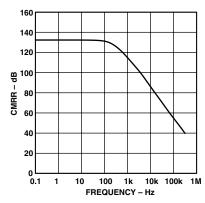

TPC 14. Common-Mode Rejection Ratio vs. Frequency

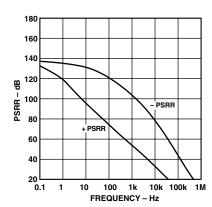

TPC 15. Power Supply Rejection Ratio vs. Frequency

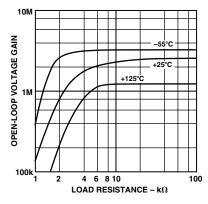

TPC 16. Open-Loop Gain vs. Load Resistance vs. Load Resistance

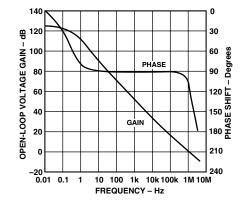

TPC 17. Open-Loop Gain and Phase Shift vs. Frequency

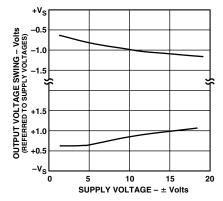

TPC 18. Output Voltage Swing vs. Supply Voltage

REV. G -5-

## **AD706**

Figure 2a. Crosstalk vs. Frequency

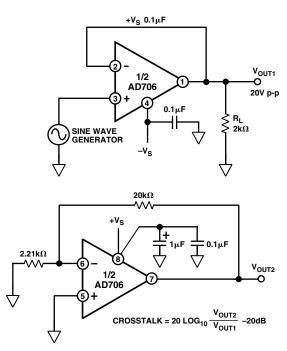

Figure 2b. Crosstalk Test Circuit

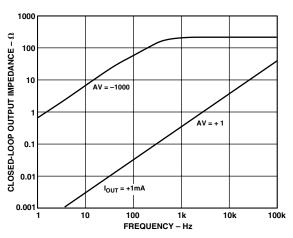

Figure 3. Magnitude of Closed-Loop Output Impedance vs. Frequency

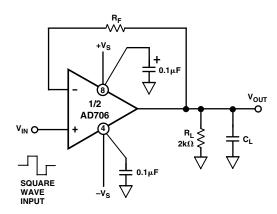

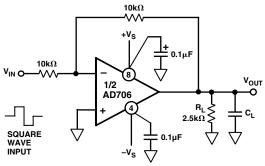

Figure 4a. Unity Gain Follower (For large signal applications, resistor  $R_F$  limits the current through the input protection diodes.)

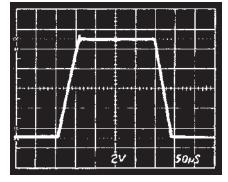

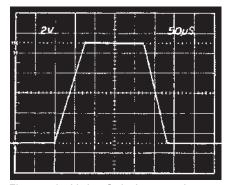

Figure 4b. Unity Gain Follower Large Signal Pulse Response,  $R_F = 10 \text{ k}\Omega$ ,  $C_L = 1,000 \text{ pF}$

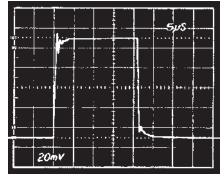

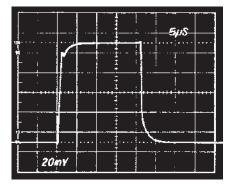

Figure 4c. Unity Gain Follower Small Signal Pulse Response,  $R_F = 0 \Omega$ ,  $C_L = 100 pF$

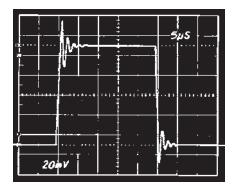

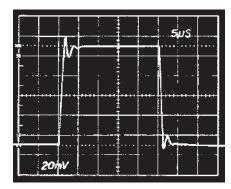

Figure 4d. Unity Gain Follower Small Signal Pulse Response,  $R_F = 0 \Omega$ ,  $C_L = 1000 pF$

-6- REV. G

Figure 5a. Unity Gain Inverter Connection

Figure 5b. Unity Gain Inverter Large Signal Pulse Response,  $C_L = 1,000 \text{ pF}$

Figure 5c. Unity Gain Inverter Small Signal Pulse Response,  $C_L = 100 \text{ pF}$

Figure 5d. Unity Gain Inverter Small Signal Pulse Response,  $C_L = 1000 \text{ pF}$

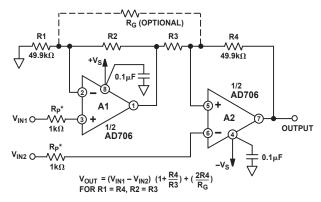

Figure 6 shows an in-amp circuit that has the obvious advantage of requiring only one AD706, rather than three op amps, with subsequent savings in cost and power consumption. The transfer function of this circuit (without  $R_{\rm G}$ ) is

$$V_{OUT} = (V_{IN1} - V_{IN2}) \left( 1 + \frac{R4}{R3} \right)$$

for R1 = R4 and R2 = R3.

Input resistance is high, thus permitting the signal source to have an unbalanced output impedance.

\*OPTIONAL INPUT PROTECTION RESISTOR FOR GAINS GREATER THAN 100 OR INPUT VOLTAGES EXCEEDING THE SUPPLY VOLTAGE.

Figure 6. Two Op Amp Instrumentation Amplifier

Furthermore, the circuit gain may be fine trimmed using an optional trim resistor, R<sub>G</sub>. Like the three op amp circuit, CMR increases with gain, once initial trimming is accomplished—but

CMR is still dependent upon the ratio matching of Resistors R1 through R4. Resistor values for this circuit, using the optional gain resistor,  $R_G$ , can be calculated using

$$R1 = R4 = 49.9 \, k\Omega$$

$$R2 = R3 = \frac{49.9 \, k\Omega}{0.9 \, G - 1}$$

$$R_G = \frac{99.8 \, k\Omega}{0.06 \, G}$$

where G =The desired circuit gain.

Table I provides practical 1% resistance values. Note that without resistor  $R_G$ ,  $R_G$  and  $R_G$  = 49.9  $k\Omega/G$ -1.

Table I. Operating Gains of Amplifiers A1 and A2 and Practical 1% Resistor Values for the Circuit of Figure 6

| Circuit Gain | Gain of A1 | Gain of A2 | R2, R3                  | R1, R4  |

|--------------|------------|------------|-------------------------|---------|

| 1.10         | 11.00      | 1.10       | 499 kΩ                  | 49.9 kΩ |

| 1.33         | 4.01       | 1.33       | $150~\mathrm{k}\Omega$  | 49.9 kΩ |

| 1.50         | 3.00       | 1.50       | $100~\mathrm{k}\Omega$  | 49.9 kΩ |

| 2.00         | 2.00       | 2.00       | $49.9~\mathrm{k}\Omega$ | 49.9 kΩ |

| 10.1         | 1.11       | 10.10      | $5.49~\mathrm{k}\Omega$ | 49.9 kΩ |

| 101.0        | 1.01       | 101.0      | $499 \Omega$            | 49.9 kΩ |

| 1001         | 1.001      | 1001       | $49.9 \Omega$           | 49.9 kΩ |

For a much more comprehensive discussion of in-amp applications, refer to the *Instrumentation Amplifier Applications Guide*—available free from Analog Devices, Inc.

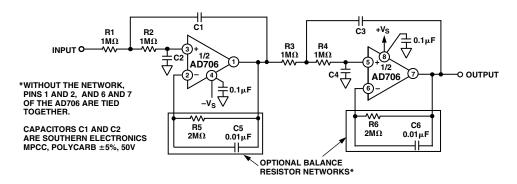

Figure 7. 1 Hz, 4-Pole Active Filter

#### 1 Hz, 4-Pole, Active Filter

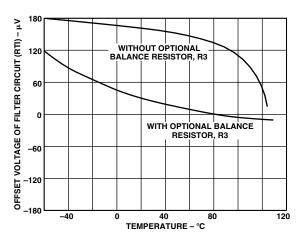

Figure 7 shows the AD706 in an active filter application. An important characteristic of the AD706 is that both the input bias current, input offset current, and their drift remain low over most of the op amp's rated temperature range. Therefore, for most applications, there is no need to use the normal balancing resistor. Adding the balancing resistor enhances performance at high temperatures, as shown by Figure 8.

Figure 8.  $V_{OS}$  vs. Temperature Performance of the 1 Hz Filter

Table II. 1 Hz, 4-Pole, Low Pass Filter Recommended Component Values

| Desired Low<br>Pass Response | Section 1<br>Frequency<br>(Hz) | Q     | Section 2<br>Frequency<br>(Hz) | Q     | C1<br>(µF) | C2<br>(µF) | C3<br>(µF) | C4<br>(μF) |

|------------------------------|--------------------------------|-------|--------------------------------|-------|------------|------------|------------|------------|

| Bessel                       | 1.43                           | 0.522 | 1.60                           | 0.806 | 0.116      | 0.107      | 0.160      | 0.0616     |

| Butterworth                  | 1.00                           | 0.541 | 1.00                           | 1.31  | 0.172      | 0.147      | 0.416      | 0.0609     |

| 0.1 dB Chebychev             | 0.648                          | 0.619 | 0.948                          | 2.18  | 0.304      | 0.198      | 0.733      | 0.0385     |

| 0.2 dB Chebychev             | 0.603                          | 0.646 | 0.941                          | 2.44  | 0.341      | 0.204      | 0.823      | 0.0347     |

| 0.5 dB Chebychev             | 0.540                          | 0.705 | 0.932                          | 2.94  | 0.416      | 0.209      | 1.00       | 0.0290     |

| 1.0 dB Chebychev             | 0.492                          | 0.785 | 0.925                          | 3.56  | 0.508      | 0.206      | 1.23       | 0.0242     |

NOTE

Specified Values are for a -3 dB point of 1.0 Hz. For other frequencies simply scale capacitors C1 through C4 directly, i.e. for 3 Hz Bessel response, C1 =  $0.0387 \, \mu\text{F}$ , C2 =  $0.0357 \, \mu\text{F}$ , C3 =  $0.0533 \, \mu\text{F}$ , C4 =  $0.0205 \, \mu\text{F}$ .

\_8\_ REV. G

AD706 Data Sheet

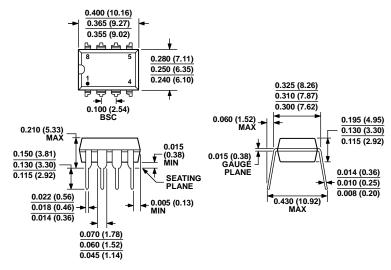

### **OUTLINE DIMENSIONS**

#### COMPLIANT TO JEDEC STANDARDS MS-001

CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN. CORNER LEADS MAY BE CONFIGURED AS WHOLE OR HALF LEADS.

Figure 9. 8-Lead Plastic Dual-in-line Package [PDIP]

Narrow Body

(N-8)

Dimensions shown in inches and (millimeters)

5.00 (0.1968) 4.80 (0.1890) A A 6.20 (0.2441) 4.00 (0.1574) 5.80 (0.2284) 3.80 (0.1497) À 0.50 (0.0196) × 45° 1.27 (0.0500) BSC 1.75 (0.0688) 0.25 (0.0099) 1.35 (0.0532) 0.25 (0.0098) 0.10 (0.0040) -►I--1.27 (0.0500) 0.51 (0.0201) COPLANARITY 0.10 0.31 (0.0122) 0.25 (0.0098) **SEATING** 0.40 (0.0157) 0.17 (0.0067) PLANE

#### COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 10. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

#### **ORDERING GUIDE**

| Model          | <b>Temperature Range</b> | Package Description             | Package Option |

|----------------|--------------------------|---------------------------------|----------------|

| AD706AR        | -40°C to +85°C           | 8-Lead SOIC_N                   | R-8            |

| AD706ARZ       | -40°C to +85°C           | 8-Lead SOIC_N                   | R-8            |

| AD706ARZ-REEL  | -40°C to +85°C           | 8-Lead SOIC_N, 13"Tape and Reel | R-8            |

| AD706ARZ-REEL7 | -40°C to +85°C           | 8-Lead SOIC_N, 7"Tape and Reel  | R-8            |

| AD706JNZ       | 0°C to + 70°C            | 8-Lead PDIP                     | N-8            |

| AD706JRZ       | 0°C to + 70°C            | 8-Lead SOIC_N                   | R-8            |

| AD706JRZ-REEL  | 0°C to + 70°C            | 8-Lead SOIC_N, 13"Tape and Reel | R-8            |

| AD706JRZ-REEL7 | 0°C to + 70°C            | 8-Lead SOIC_N, 7"Tape and Reel  | R-8            |

REV. G -9-

Data Sheet AD706

#### **REVISION HISTORY**

| 7/2018—Rev. F to Rev. G                      |

|----------------------------------------------|

| Changed Plastic Mini-DIP to PDIP             |

| Updated Outline Dimensions                   |

| 8/2017—Rev. E to Rev. F                      |

| Changes to Figure 66                         |

| Updated Outline Dimensions10                 |

| Changes to Ordering Guide                    |

| 10/2003—Rev. D to Rev. E                     |

| Removed K Version                            |

| Changes to Features and Product Description1 |

| Renumbered TPC's4                            |

| Renumbered Figured6                          |

| Updated Outline Dimensions                   |

| 10/2002—Rev. C to Rev. D                     |

| Deleted 8-Lead CERDIP (Q-8) Package          |

| Changes to Features and Product Description1 |

| Changes to Specifications Section2           |

| Changes to Absolute Maximum Ratings Section3 |

| Changes to Ordering Guide3                   |

| Updated Outline Dimensions                   |