# Compact, Low Power, 12-Bit, 2 MSPS/500 kSPS Easy Drive SAR ADC

#### **FEATURES**

- ▶ Small footprint, big performance

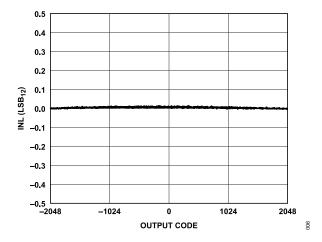

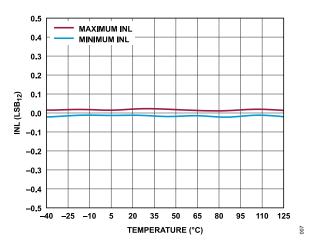

- ▶ INL: ±0.1 LSB maximum

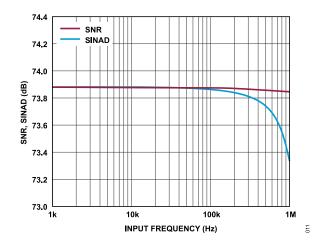

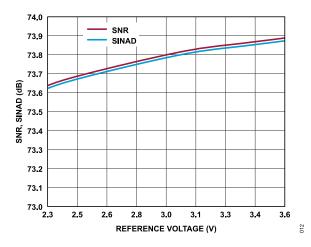

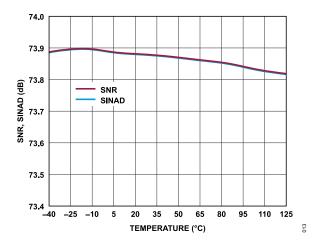

- $\triangleright$  SNR: 73.8 dB with  $V_{REF} = 3.3 \text{ V}$

- ▶ 1.35 nJ per conversion

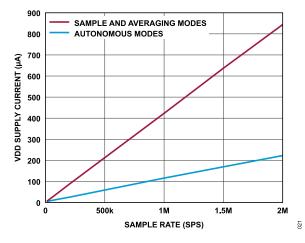

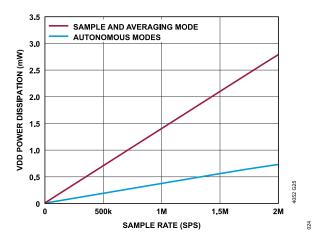

- ▶ 1.35 mW/0.68 mW at 1 MSPS/500 kSPS in sample mode

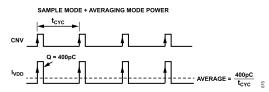

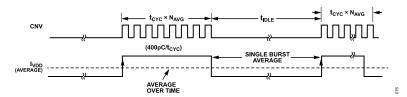

- ▶ 370 µW/112 µW at 1 MSPS/300 kSPS in autonomous modes

- ▶ 4.1 µW standby power

- ▶ Versatile signal conditioning integration

- ▶ Easy Drive features enable small, low-power AFE designs

- ▶ Compatible with differential and single-ended signal chains

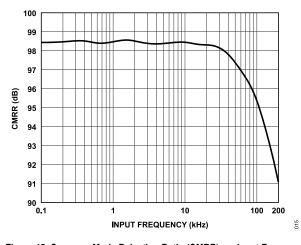

- ▶ Wide common-mode input range

- ▶ Minimizes digital host activity and power dissipation

- ► Autonomous sampling with window comparator and interrupt generation

- Averaging filter with continuous and burst sampling options

- ▶ Power cycling synchronization for companion devices

- ▶ 4-wire SPI compatible with 1.8 V to 3.3 V logic

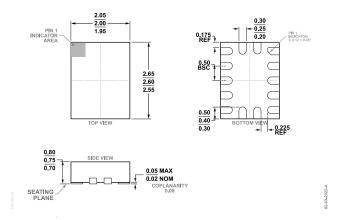

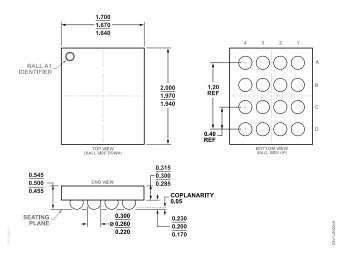

- ▶ 2.00 mm × 2.6 mm LFCSP and 1.67 mm × 1.97 mm WLCSP

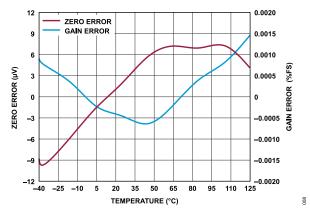

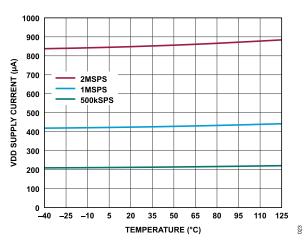

- ▶ Wide operating temperature range: -40°C to +125°C

#### **APPLICATIONS**

- Battery-powered data acquisition

- Vital signs monitoring

- ▶ Biological and chemical analysis

- Geologic and seismic sensing

- Motion and robotics

### **GENERAL DESCRIPTION**

The AD4050/AD4056 are versatile, 12-bit, successive approximation register (SAR) analog-to-digital converters (ADCs) that enable low-power, high-density data acquisition solutions without sacrificing precision. These ADCs offer a unique balance of performance and power efficiency, plus innovative features for seamlessly switching between high-resolution and low-power modes tailored to the immediate needs of the system. The AD4050/AD4056 are ideal for battery-powered, compact data acquisition and edge sensing applications.

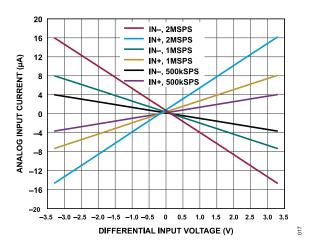

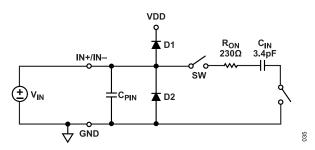

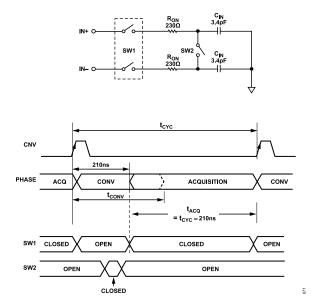

The Easy Drive features enable highly efficient analog front end (AFE) designs. The small sampling capacitors (3.4 pF) maximize input impedance, thus reducing the dependence on high-bandwidth, power-hungry amplifiers typically required by SAR ADCs. The wide input common-mode range grants inherent support for both differential and single-ended signals.

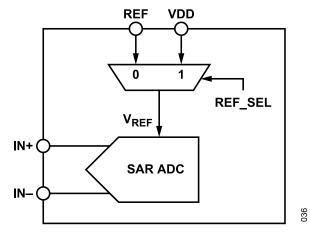

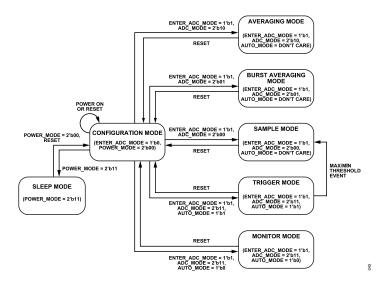

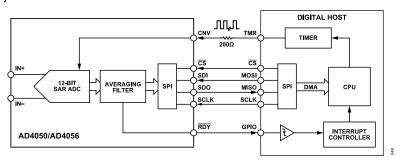

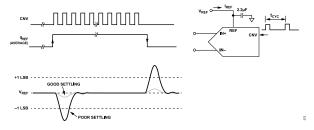

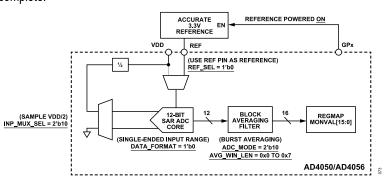

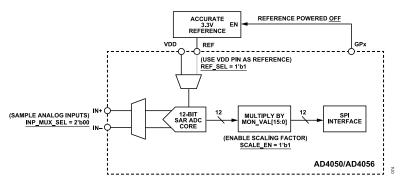

The AD4050/AD4056 support microcontrollers with power-down modes and interrupt-driven firmware. The autonomous modes enable out-of-range event detection while the digital host sleeps. The averaging modes deliver on-demand, high-resolution measurements while offloading computations from the host processor. The self timed device enable signal (DEV\_EN) synchronizes AFE device power cycling to the ADC sampling instant, optimizing system power consumption while minimizing power-up settling error artifacts. The AD4050/AD4056 also support power cycling the voltage reference and using the supply as the ADC reference voltage (V<sub>REF</sub>) for additional power savings.

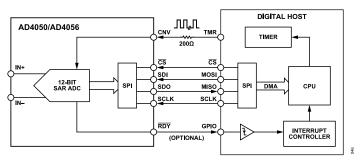

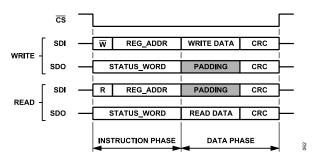

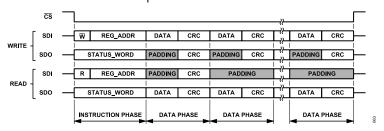

The device configuration and ADC data readback are supported via a robust, 4-wire serial peripheral interface (SPI) with cyclic redundancy check (CRC) supported for all data transfers. The AD4050/AD4056 are available in compact LFCSP and WLCSP packages and operate across a wide temperature range, making them ideal for a diverse set of applications.

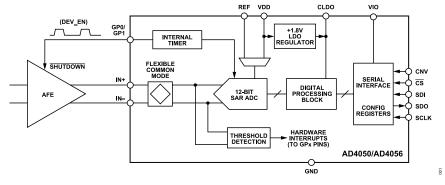

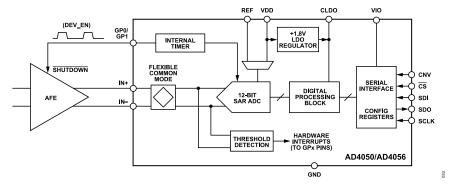

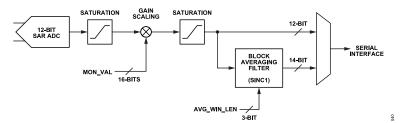

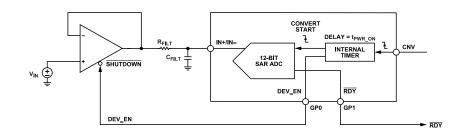

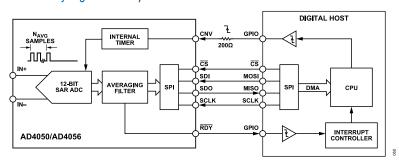

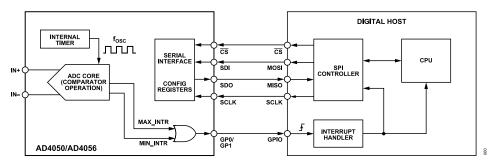

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

Rev. A

### www.datasheetall.com

# **TABLE OF CONTENTS**

| Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1         | Achieving High Accuracy with Reference  |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------|----|

| Separation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1         |                                         | 48 |

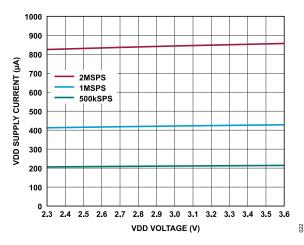

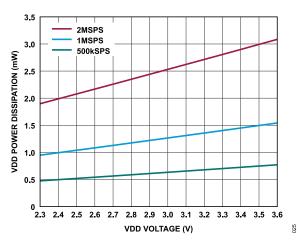

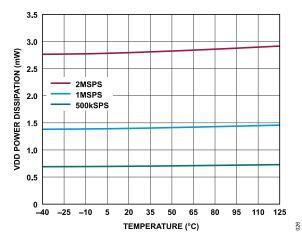

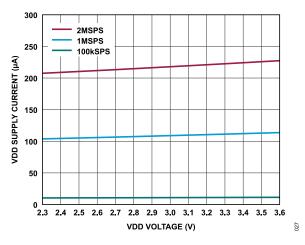

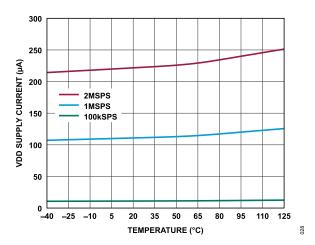

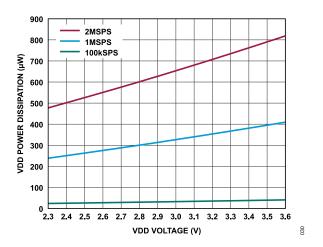

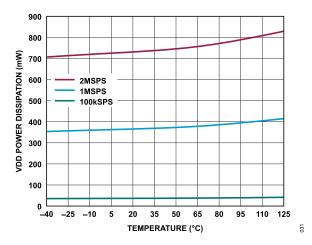

| Functional Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | VDD Power Dissipation                   | 50 |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | •                                       |    |

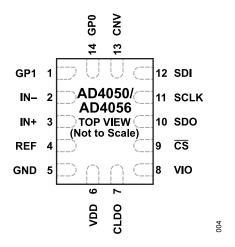

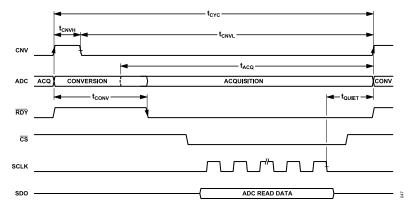

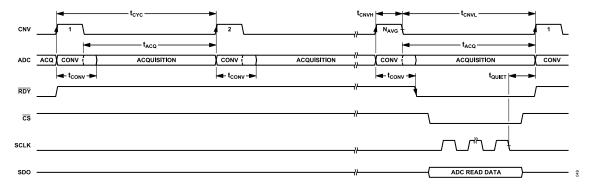

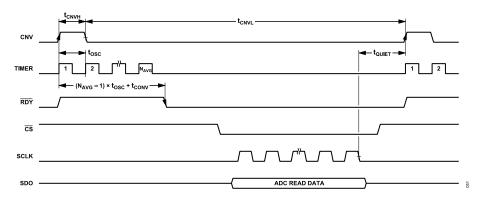

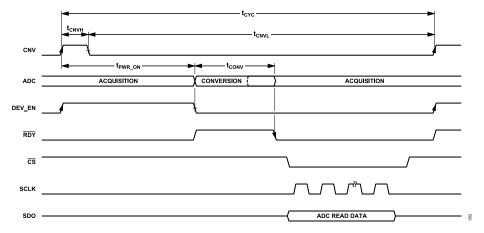

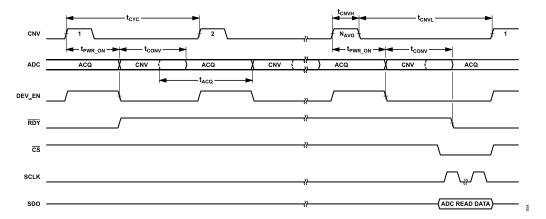

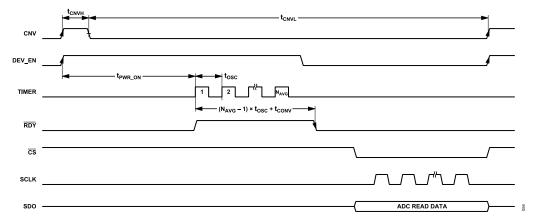

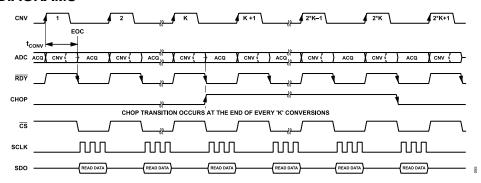

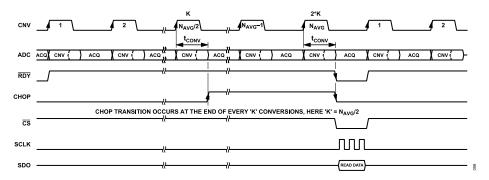

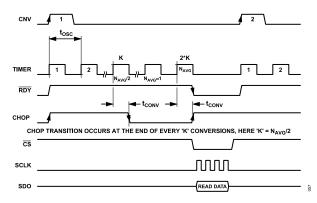

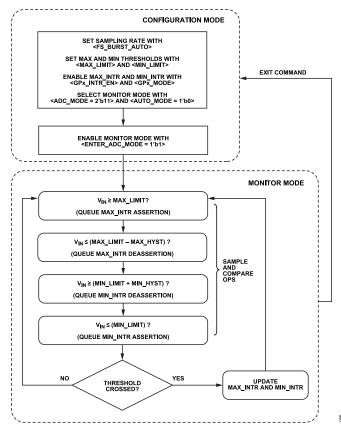

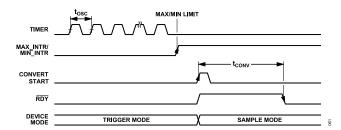

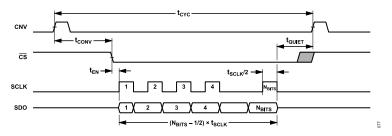

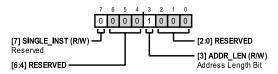

| Timing Specifications. 7 Layout Recommendations. 52 Absolute Maximum Ratings. 10 Register Summary. 53 Thermal Resistance. 10 Register Details. 54 Register Details. 54 Register Details. 55 Register Details. 54 Interface Configuration A Register. 54 Pin Configuration and Function Descriptions. 11 Device Configuration Register. 54 Typical Performance Characteristics. 13 Device Type Register. 55 Theory of Operation. 19 Product Identification (LSByte) Register. 55 Overview. 19 Device Grade Register. 55 Converter Operation. 19 Product Identification (MSByte) Register. 55 Overview. 19 Device Grade Register. 55 Converter Operation. 19 Scratch Pad Register. 56 Analog Inputs. 21 Vendor Identification (MSByte) Register. 56 Digital Processing Features. 22 Reserved Registers. 57 Internal Timer. 23 Interface Status Register. 57 Comparator Operation. 23 Interface Status Register. 57 Comparator Operation. 23 Device Mode Select Register. 58 Modes of Operation. 29 Averaging Mode. 31 Averaging Mode. 32 General Purpose Pin Configuration Register. 59 APC Operating Mode. 32 General Purpose Pin Configuration Register. 61 DEV_EN Timing Diagrams. 35 Timer Configuration Register. 61 ChOP Timing Diagrams. 35 Timer Configuration Register. 61 ChOP Timing Diagrams. 35 Timer Configuration Register. 63 Maximum Threshold Configuration Register. 64 Device Reset. 43 Maximum Threshold Hysteresis Register. 64 Device Reset. 43 Maximum Threshold Hysteresis Register. 64 Applications Information. 45 Device Reset. 43 Maximum Threshold Hysteresis Register. 64 Maximum Interrupt Sample Register. 65 Analog Front-End Design. 47 Optimized Amplifier Shutdown and ADC Sampling. 48 Evaluation Boards. 67 Revision History 41/2024—Rev. 0 to Rev. A Changes to Table 22. Changes to Table 22. Changes to Table 40. 65 Changes to Table 40. 66 Changes to Table |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                         | 51 |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                         |    |

| Thermal Resistance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | · · · · · · · · · · · · · · · · · · ·   |    |

| Electrostatic Discharge (ESD) Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           | - · · · · · · · · · · · · · · · · · · · |    |

| ESD Caution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Electrostatic Discharge (ESD) Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10        | •                                       |    |

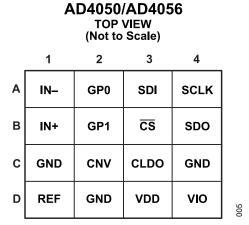

| Pin Configuration and Function Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                         |    |

| Typical Performance Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                         |    |

| Terminology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                         |    |

| Product Identification (MSByte) Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | * ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                                         |    |

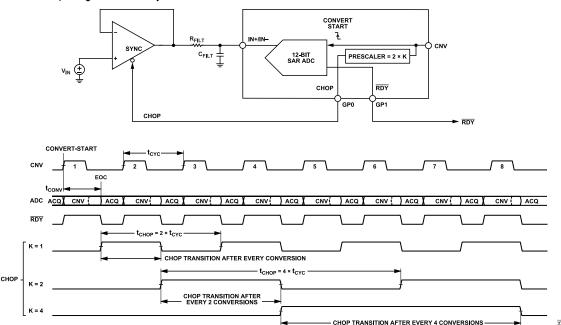

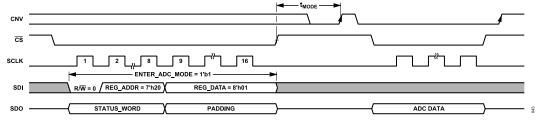

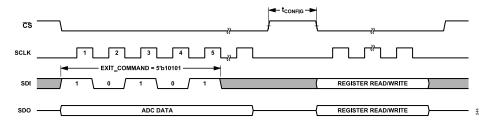

| Overview.         19         Device Grade Register.         55           Converter Operation.         19         Scratch Pad Register.         56           Analog Inputs.         21         Vendor Identification (LSByte) Register.         56           Voltage Reference.         21         Vendor Identification (MSByte) Register.         56           Digital Processing Features.         22         Reserved Registers.         57           Interral Timer.         23         Interface Configuration C Register.         57           Power Supplies.         23         Interface Status Register.         57           Comparator Operation.         23         Device Mode Select Register.         58           Interrupts and Control Signals.         25         ADC Operating Mode Configuration Register.         58           Modes of Operation.         29         ADC Setup Configuration Register.         59           Sample Mode.         31         Averaging Mode Configuration Register.         59           Sample Mode.         32         General Purpose Pin Configuration Register.         69           Burst Averaging Mode.         33         Interrupt Configuration Register.         61           CHOP Timing Diagrams.         34         Chop Signal Configuration Register.         61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                                         |    |

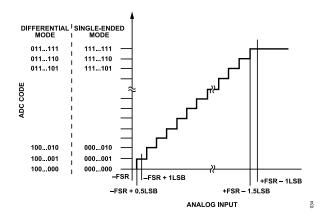

| Converter Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                         |    |

| Analog Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                         |    |

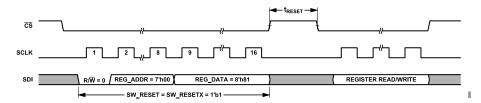

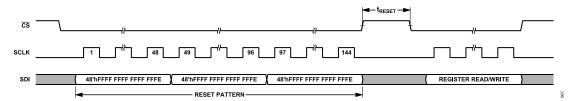

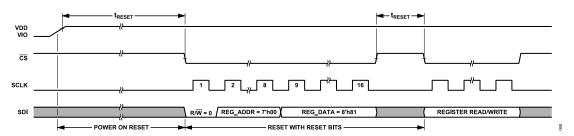

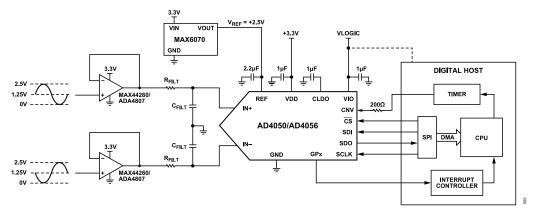

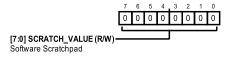

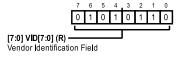

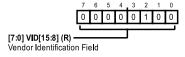

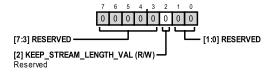

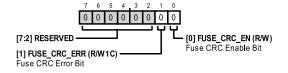

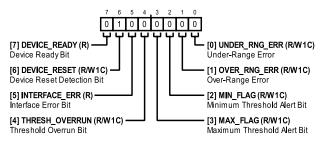

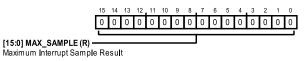

| Voltage Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | <del>-</del>                            |    |