MAX3100 Datasheet

SPI/MICROWIRE-Compatible UART in QSOP-16

SPI/MICROWIRE-Compatible UART in QSOP-16

| Part No. | In Stock | Price | Packaging | SPQ | Marking | MSL | Pins | Temp Range | Package Description |

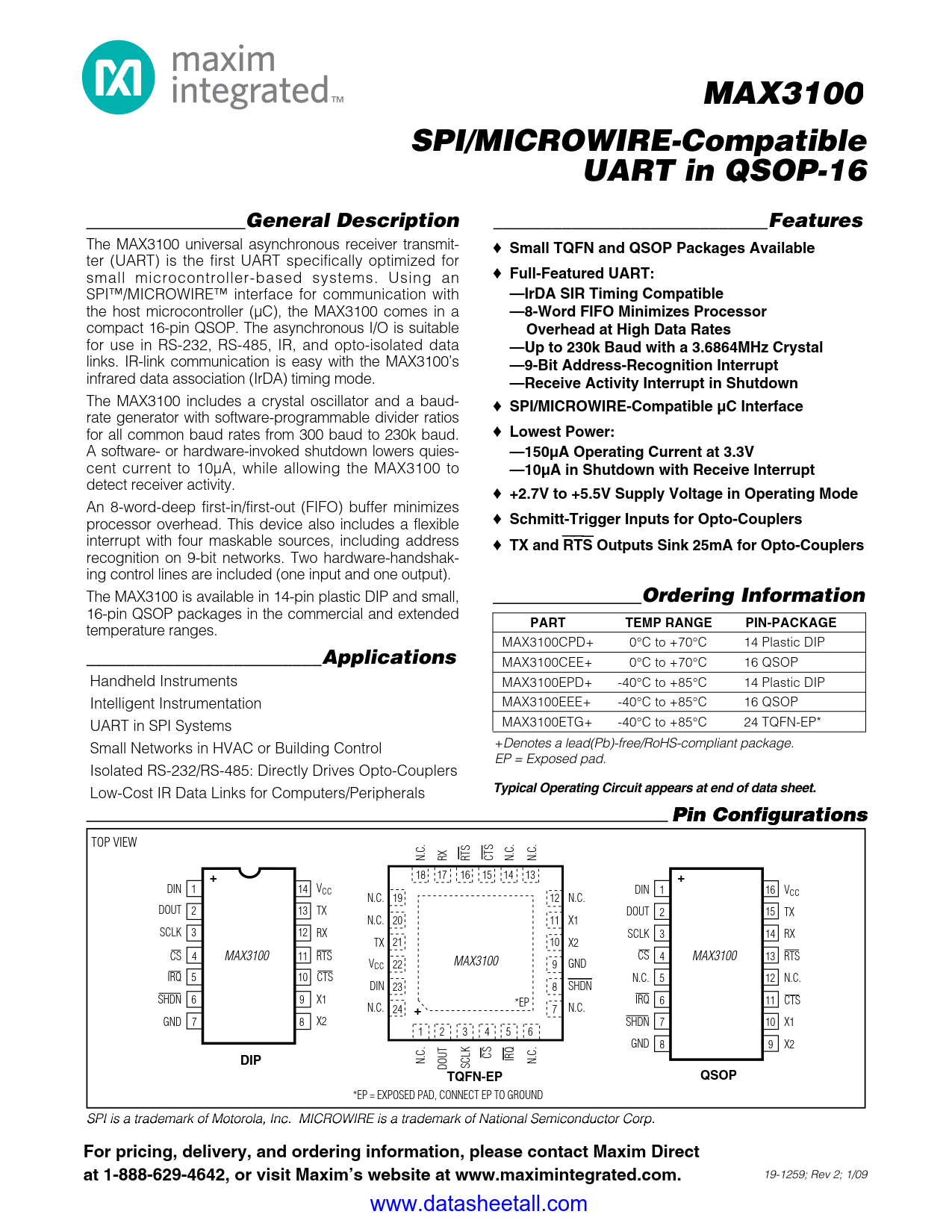

The MAX3100 universal asynchronous receiver transmitter (UART) is the first UART specifically optimized for small microcontroller-based systems. Using an SPI™/MICROWIRE™ interface for communication with the host microcontroller (µC), the MAX3100 comes in a compact 24-pin-TQFN and 16-pin QSOP. The asynchronous I/O is suitable for use in RS-232, RS-485, IR, and opto-isolated data links. IR-link communication is easy with the MAX3100's infrared data association (IrDA) timing mode.

The MAX3100 includes a crystal oscillator and a baud-rate generator with software-programmable divider ratios for all common baud rates from 300 baud to 230k baud. A software- or hardware-invoked shutdown lowers quiescent current to 10µA, while allowing the MAX3100 to detect receiver activity.

An 8-word-deep first-in/first-out (FIFO) buffer minimizes processor overhead. This device also includes a flexible interrupt with four maskable sources, including address recognition on 9-bit networks. Two hardware-handshaking control lines are included (one input and one output).

The MAX3100 is available in 14-pin plastic DIP and small, 16-pin QSOP packages in the commercial and extended temperature ranges.