ADSP-TS203S Datasheet

500 MHz TigerSHARC Processor with 4 Mbit on-chip embedded DRAM

500 MHz TigerSHARC Processor with 4 Mbit on-chip embedded DRAM

| Part No. | In Stock | Price | Packaging | SPQ | Marking | MSL | Pins | Temp Range | Package Description |

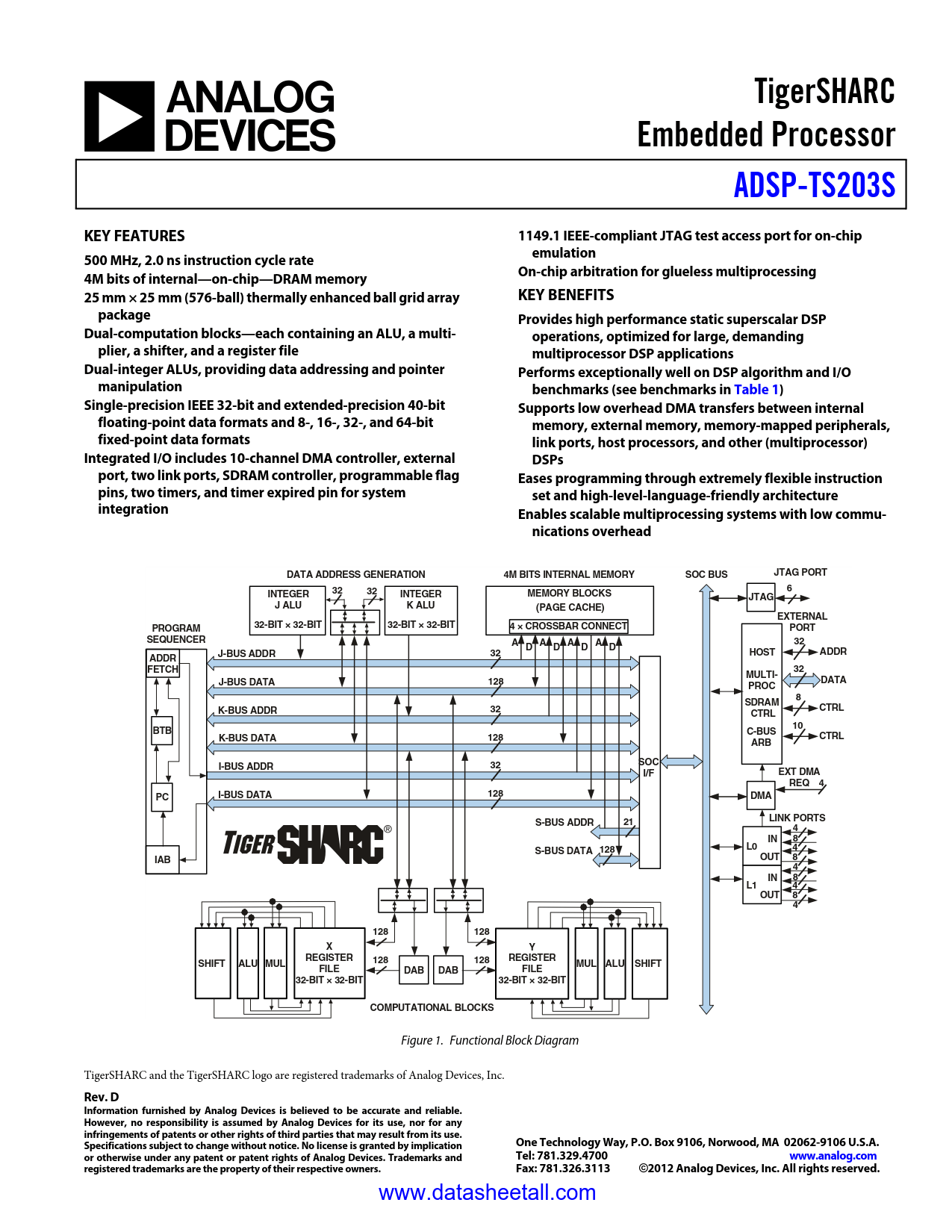

The ADSP-TS203S is a member of the TigerSHARC Processor family. Targeted at numerous signal processing applications that rely on multiple processors working together to execute computationally-intensive real-time functions, ADI's TigerSHARC Processor is well-suited to video and communication markets as well as defense, medical imaging, industrial instrumentation. The ADSP-TS203S features a static superscaler architecture which combines RISC, VLIW and standard DSP functionality. Native support of fixed and floating point data types, coupled with the leading edge multiprocessing capabilities allows the TigerSHARC Processor to offer unrivaled DSP performance. At a 500 MHz clock rate, the ADSP-TS203S offers the industry's highest 16-bit fixed-point and 32-bit floating-point performance. The ADSP-TS203S has a 32-bit 1024-point complex FFT time of 20.2 microseconds and provides 1500 MFLOPs per watt.

ADSP-TS203S Performance:The ADSP-TS201S is available in a 25x25mm inexpensive, BGA package. The TigerSHARC Processor is available for general purpose sampling today.