ADSP-21569 Datasheet

Up to 1GHz SHARC+ DSP with 640KB L1, 1024KB Shared L2 SRAM, 400-Ball CSP_BGA

Up to 1GHz SHARC+ DSP with 640KB L1, 1024KB Shared L2 SRAM, 400-Ball CSP_BGA

| Part No. | In Stock | Price | Packaging | SPQ | Marking | MSL | Pins | Temp Range | Package Description |

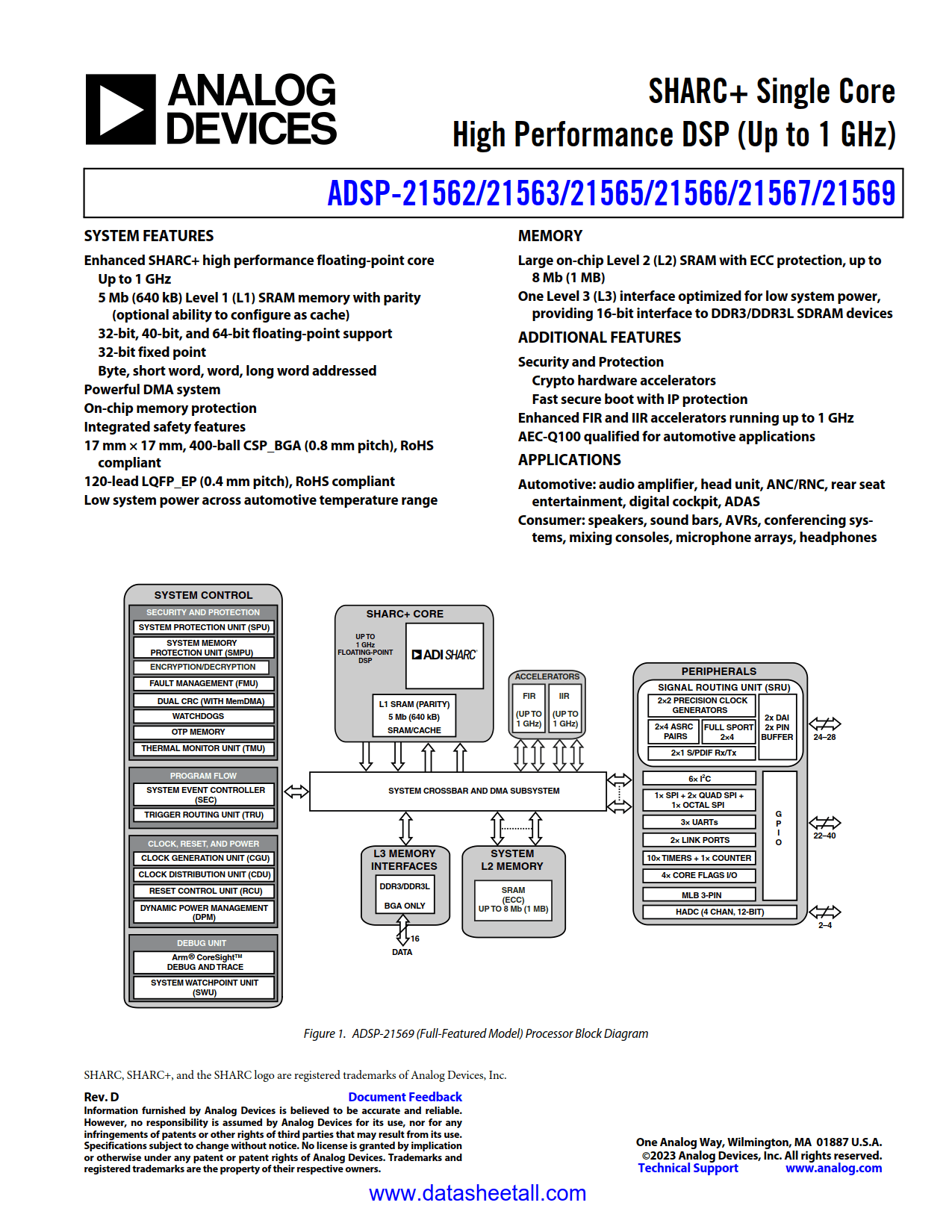

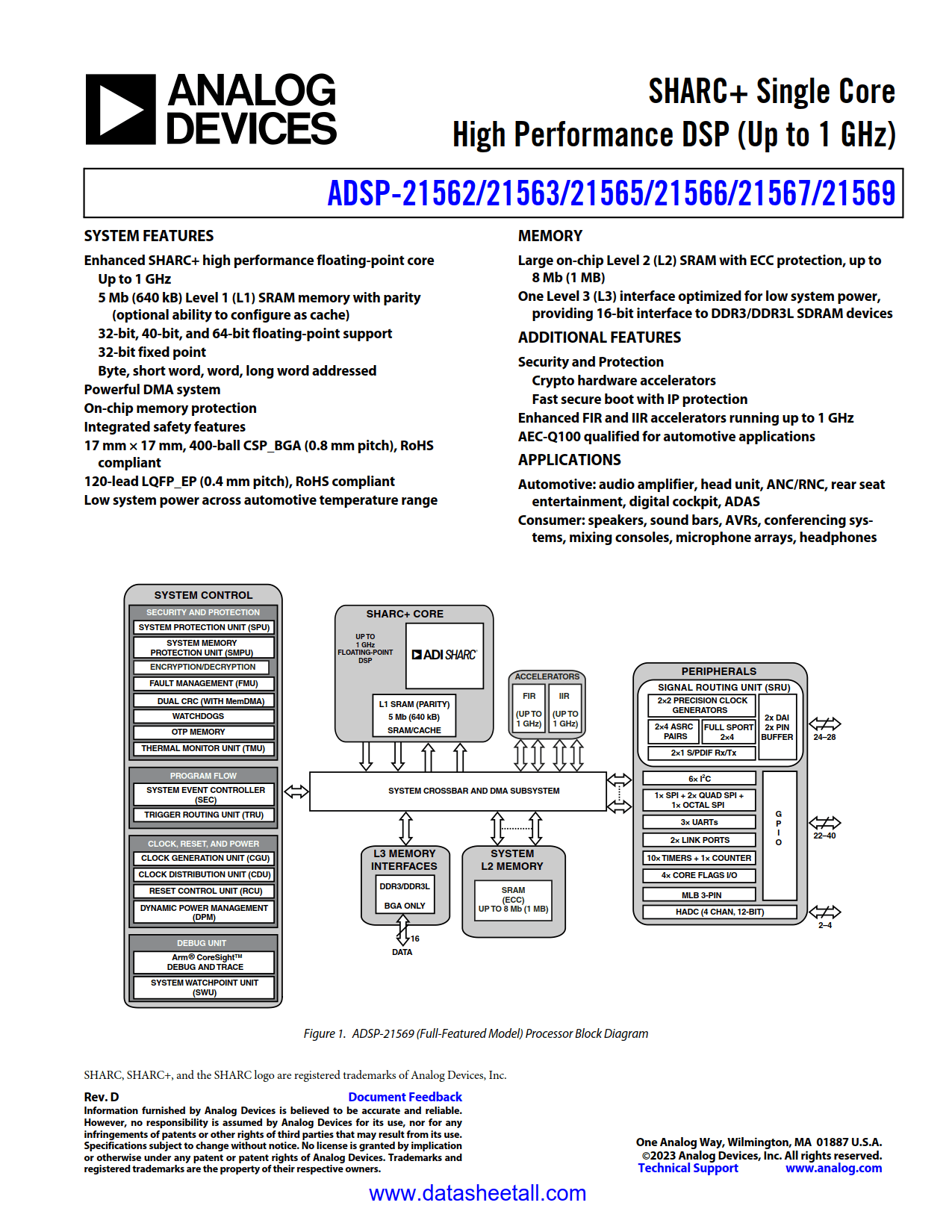

Reaching speeds of up to 1 GHz, the ADSP-21569 processors are members of the SHARC® family of products. The ADSP-21569 processor is based on the SHARC+® single core. The ADSP-21569 SHARC processors are members of the SIMD SHARC family of digital signal processors (DSPs) that feature Analog Devices, Inc., Super Harvard Architecture. These 32-bit/40-bit/64-bit floating-point processors are optimized for high performance audio/floating-point applications with large on-chip static random-access memory (SRAM), multiple internal buses that eliminate input/output (I/O) bottlenecks, and innovative digital audio interfaces (DAI). New additions to the SHARC+ core include cache enhancements and branch prediction, while maintaining instruction set compatibility to previous SHARC products.

By integrating a rich set of industry-leading system peripherals and memory (see Table 1 in the data sheet), the SHARC+ processor is the platform of choice for applications that require programmability similar to reduced instruction set computing (RISC), multimedia support, and leading edge signal processing in one integrated package. These applications span a wide array of markets, including automotive, professional audio, and industrial-based applications that require high floating-point performance.