ADP5043 Datasheet

Micro PMU with 800 mA Buck, 300 mA LDO, Supervisory, Watchdog, and Manual Reset

Micro PMU with 800 mA Buck, 300 mA LDO, Supervisory, Watchdog, and Manual Reset

| Part No. | In Stock | Price | Packaging | SPQ | Marking | MSL | Pins | Temp Range | Package Description |

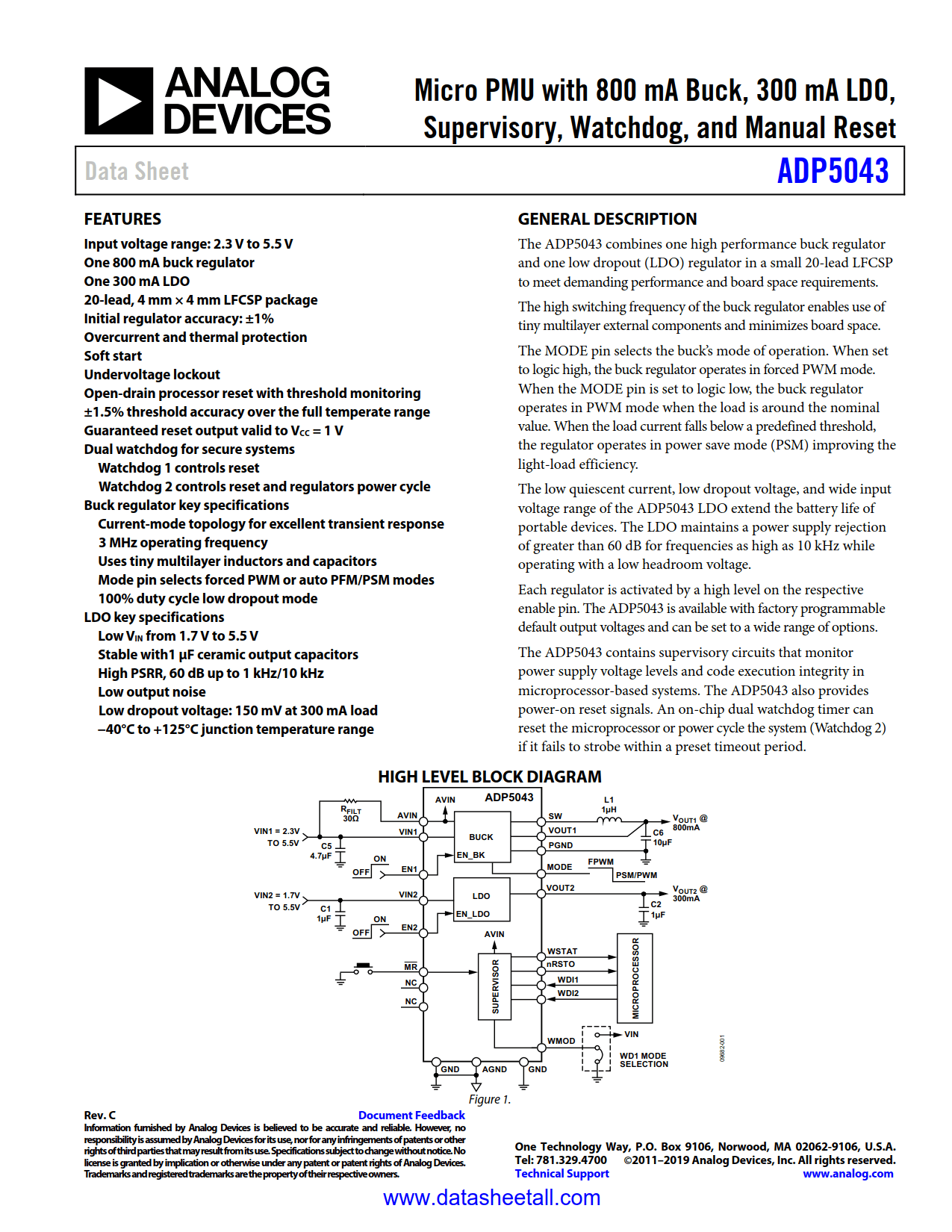

The ADP5043 combines one high performance buck regulator and one low dropout (LDO) regulator in a small 20-lead LFCSP to meet demanding performance and board space requirements.

The high switching frequency of the buck regulator enables use of tiny multilayer external components and minimizes board space.

The MODE pin selects the buck’s mode of operation. When set to logic high, the buck regulator operates in forced PWM mode. When the MODE pin is set to logic low, the buck regulator operates in PWM mode when the load is around the nominal value. When the load current falls below a predefined threshold, the regulator operates in power save mode (PSM) improving the light-load efficiency.

The low quiescent current, low dropout voltage, and wide input voltage range of the ADP5043 LDO extend the battery life of portable devices. The LDO maintains a power supply rejection of greater than 60 dB for frequencies as high as 10 kHz while operating with a low headroom voltage.

Each regulator is activated by a high level on the respective enable pin. The ADP5043 is available with factory programmable default output voltages and can be set to a wide range of options.

The ADP5043 contains supervisory circuits that monitor power supply voltage levels and code execution integrity in microprocessor-based systems. The ADP5043 also provides power-on reset signals. An on-chip dual watchdog timer can reset the microprocessor or power cycle the system (Watchdog 2) if it fails to strobe within a preset timeout period.