AD9557 Datasheet

Dual-Input Multiservice Line Card Adaptive Clock Translator

Dual-Input Multiservice Line Card Adaptive Clock Translator

| Part No. | In Stock | Price | Packaging | SPQ | Marking | MSL | Pins | Temp Range | Package Description |

| AD9557BCPZ | 0 | $23.355 | Tray | 24 | AD9557BCPZ | 3 | 40 | -40°C ~ 85°C | 40-Lead LFCSP-VQ |

| AD9557BCPZ-REEL7 | 1500pcs | $23.355 | Reel | 750 | AD9557BCPZ | 3 | 40 | -40°C ~ 85°C | 40-Lead LFCSP-VQ |

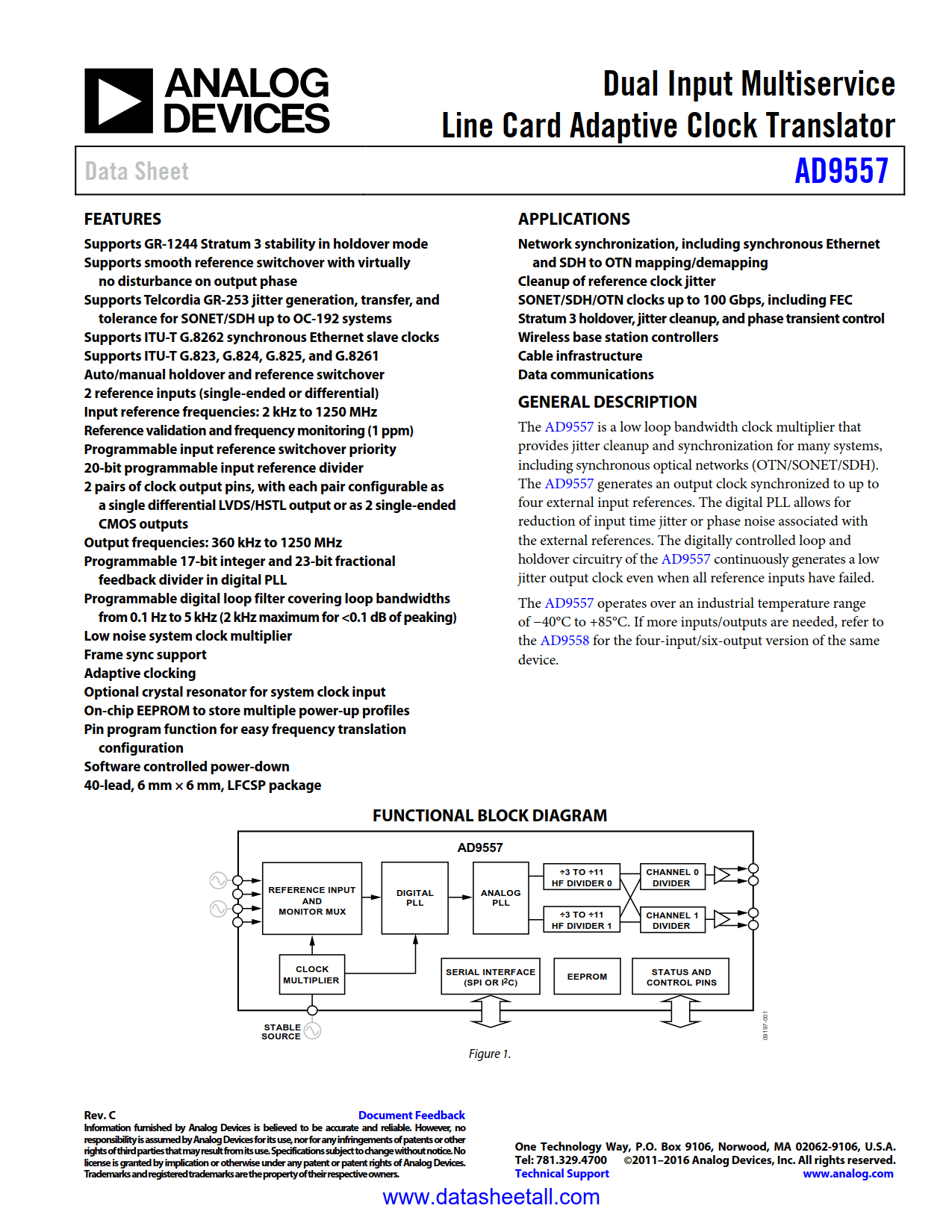

The AD9557 is a low loop bandwidth clock multiplier that provides jitter cleanup and synchronization for many systems, including synchronous optical networks (OTN/SONET/SDH). The AD9557 generates an output clock synchronized to up to four external input references. The digital PLL allows for reduction of input time jitter or phase noise associated with the external references. The digitally controlled loop and holdover circuitry of the AD9557 continuously generates a low jitter output clock even when all reference inputs have failed.

The AD9557 operates over an industrial temperature range of −40°C to +85°C. If more inputs/outputs are needed, refer to the AD9558 for the four-input/six-output version of the same device.