AD608 Datasheet

Low Power Mixer/Limiter/RSSI 3V Receiver IF Subsystem

Low Power Mixer/Limiter/RSSI 3V Receiver IF Subsystem

| Part No. | In Stock | Price | Packaging | SPQ | Marking | MSL | Pins | Temp Range | Package Description |

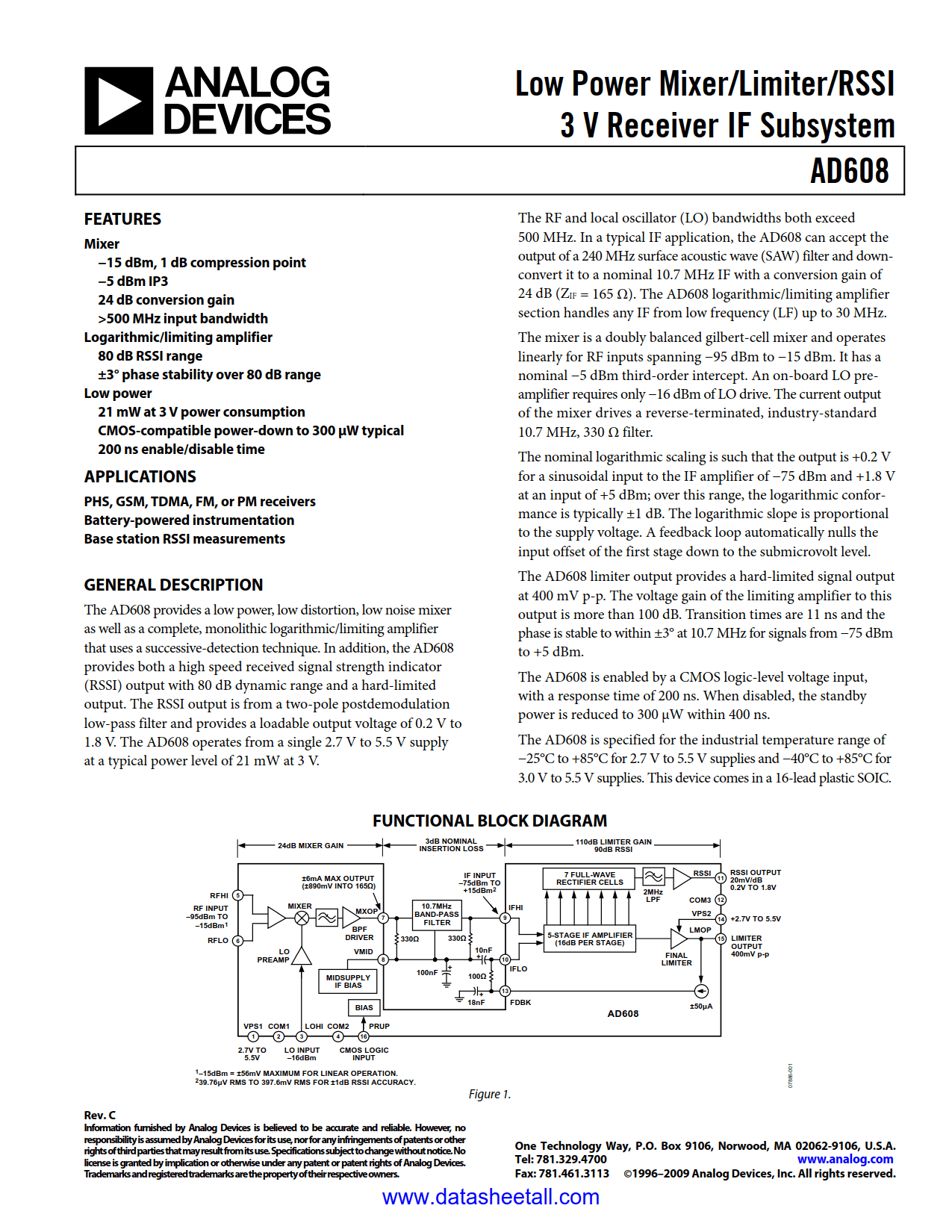

The AD608 provides a low power, low distortion, low noise mixer as well as a complete, monolithic logarithmic/limiting amplifier that uses a successive-detection technique. In addition, the AD608 provides both a high speed received signal strength indicator (RSSI) output with 80 dB dynamic range and a hard-limited output. The RSSI output is from a two-pole postdemodulation low-pass filter and provides a loadable output voltage of 0.2 V to 1.8 V. The AD608 operates from a single 2.7 V to 5.5 V supply at a typical power level of 21 mW at 3 V.

The RF and local oscillator (LO) bandwidths both exceed 500 MHz. In a typical IF application, the AD608 can accept the output of a 240 MHz surface acoustic wave (SAW) filter and down-convert it to a nominal 10.7 MHz IF with a conversion gain of 24 dB (ZIF = 165 Ω). The AD608 logarithmic/limiting amplifier section handles any IF from low frequency (LF) up to 30 MHz.

The mixer is a doubly balanced gilbert-cell mixer and operates linearly for RF inputs spanning −95 dBm to −15 dBm. It has a nominal −5 dBm third-order intercept. An on-board LO preamplifier requires only −16 dBm of LO drive. The current output of the mixer drives a reverse-terminated, industry-standard 10.7 MHz, 330 Ω filter.

The nominal logarithmic scaling is such that the output is +0.2 V for a sinusoidal input to the IF amplifier of −75 dBm and +1.8 V at an input of +5 dBm; over this range, the logarithmic conformance is typically ±1 dB. The logarithmic slope is proportional to the supply voltage. A feedback loop automatically nulls the input offset of the first stage down to the submicrovolt level.

The AD608 limiter output provides a hard-limited signal output at 400 mV p-p. The voltage gain of the limiting amplifier to this output is more than 100 dB. Transition times are 11 ns and the phase is stable to within ±3° at 10.7 MHz for signals from −75 dBm to +5 dBm.

The AD608 is enabled by a CMOS logic-level voltage input, with a response time of 200 ns. When disabled, the standby power is reduced to 300 μW within 400 ns.

The AD608 is specified for the industrial temperature range of −25°C to +85°C for 2.7 V to 5.5 V supplies and −40°C to +85°C for 3.0 V to 5.5 V supplies. This device comes in a 16-lead plastic SOIC.