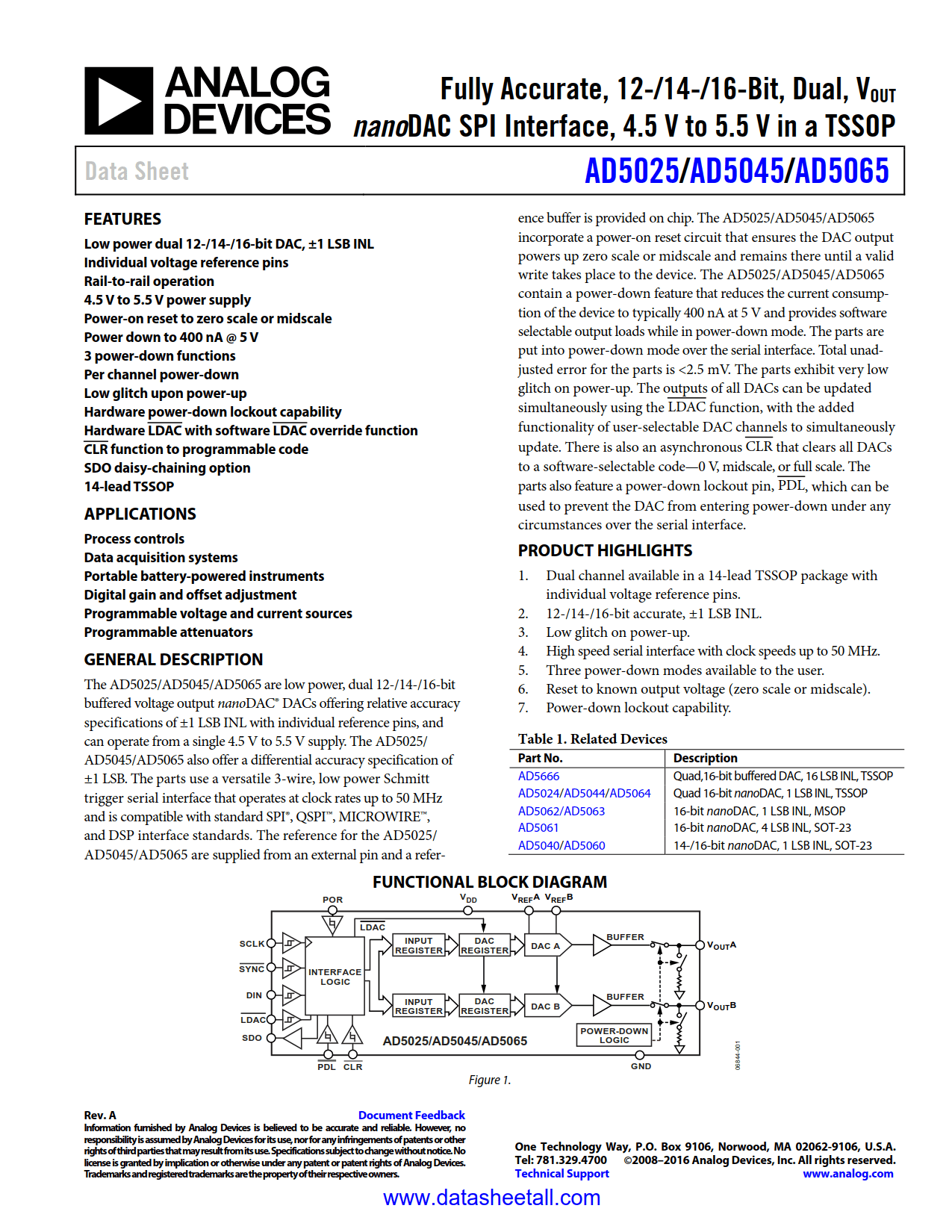

AD5045 Datasheet

Fully Accurate 14-Bit VOUT nanoDAC® SPI Interface 4.5 V to 5.5 V in a TSSOP

Fully Accurate 14-Bit VOUT nanoDAC® SPI Interface 4.5 V to 5.5 V in a TSSOP

| Part No. | In Stock | Price | Packaging | SPQ | Marking | MSL | Pins | Temp Range | Package Description |