#### **ADES1755**

# 14-Channel, High-Voltage Data-Acquisition Systems

### **General Description**

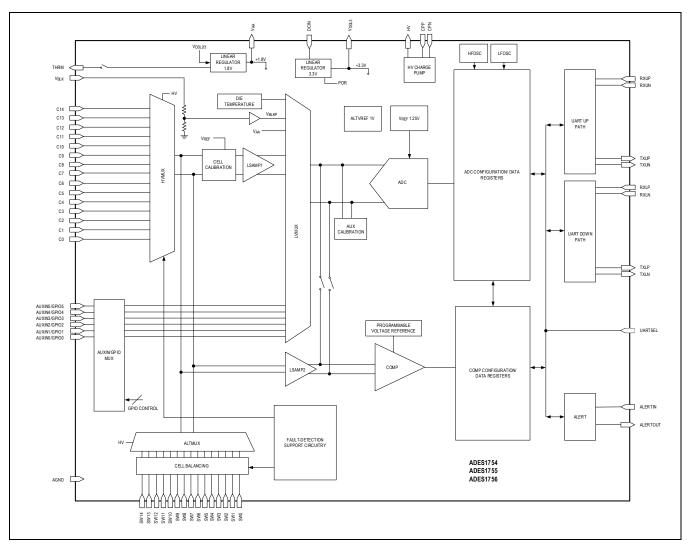

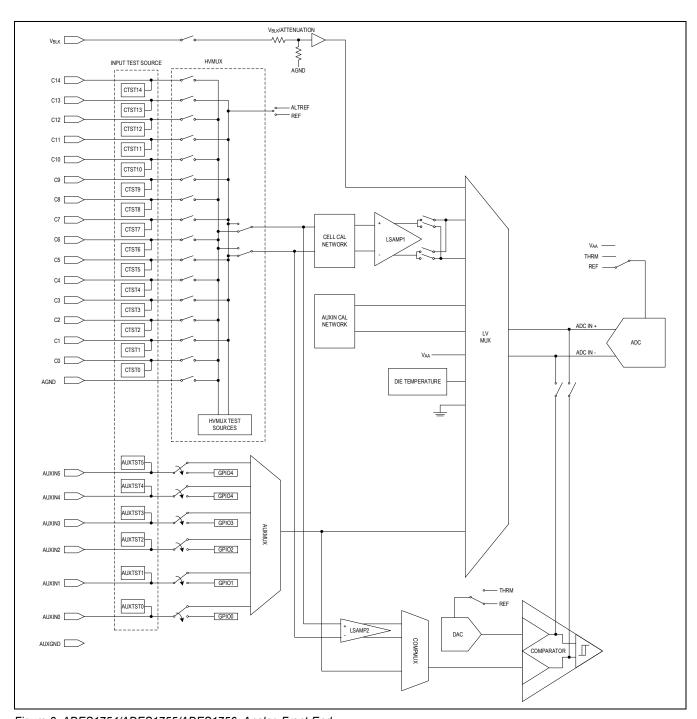

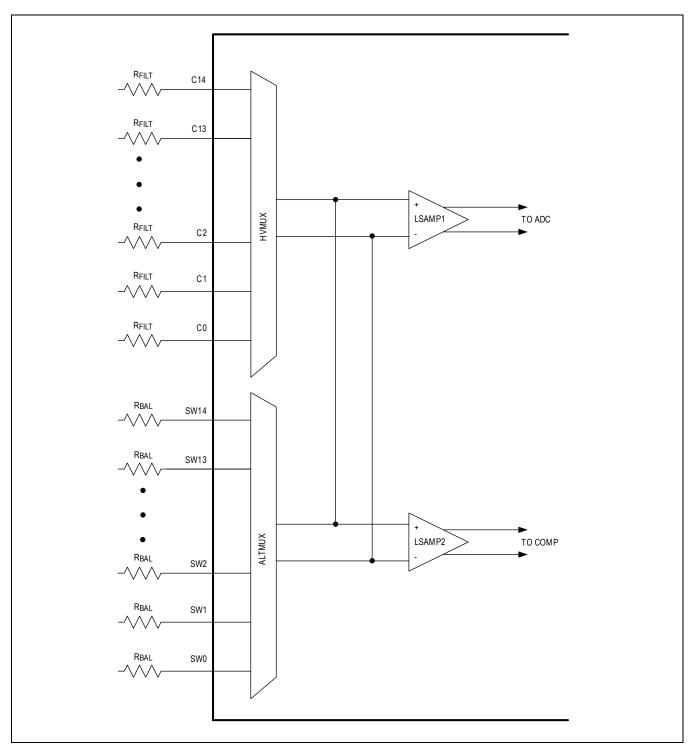

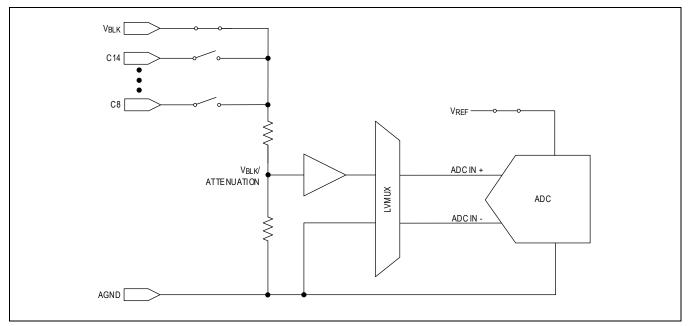

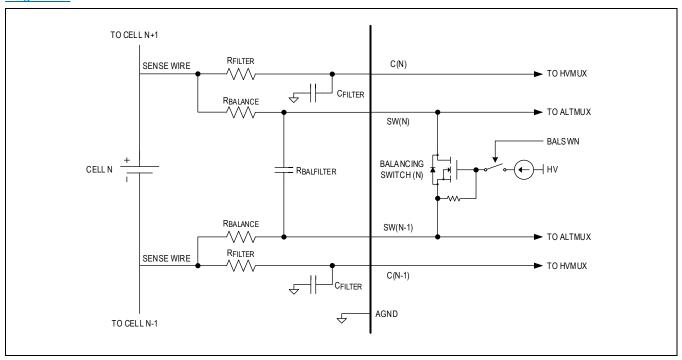

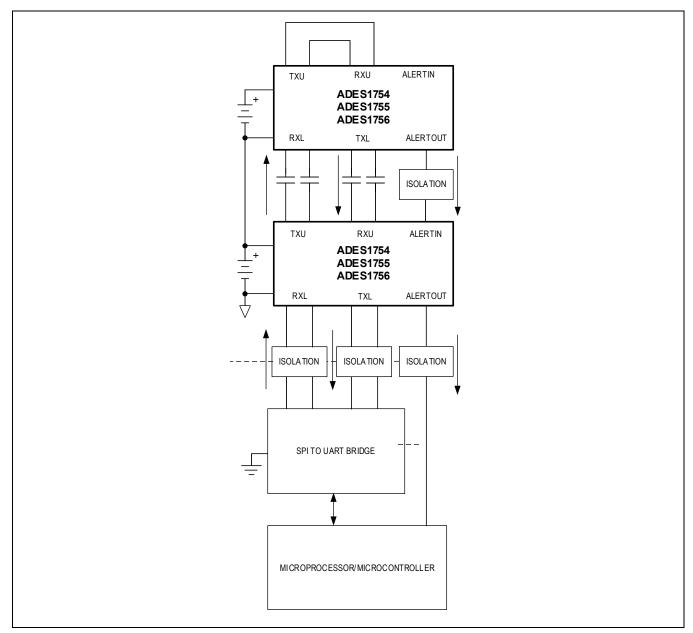

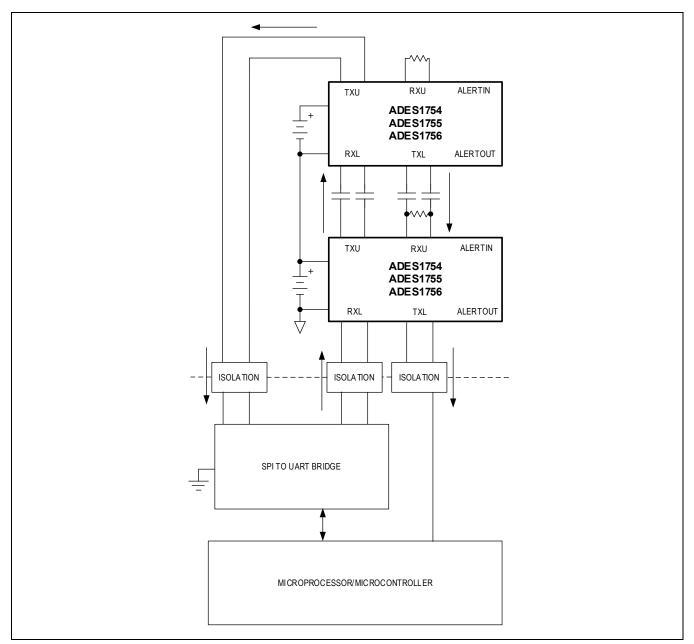

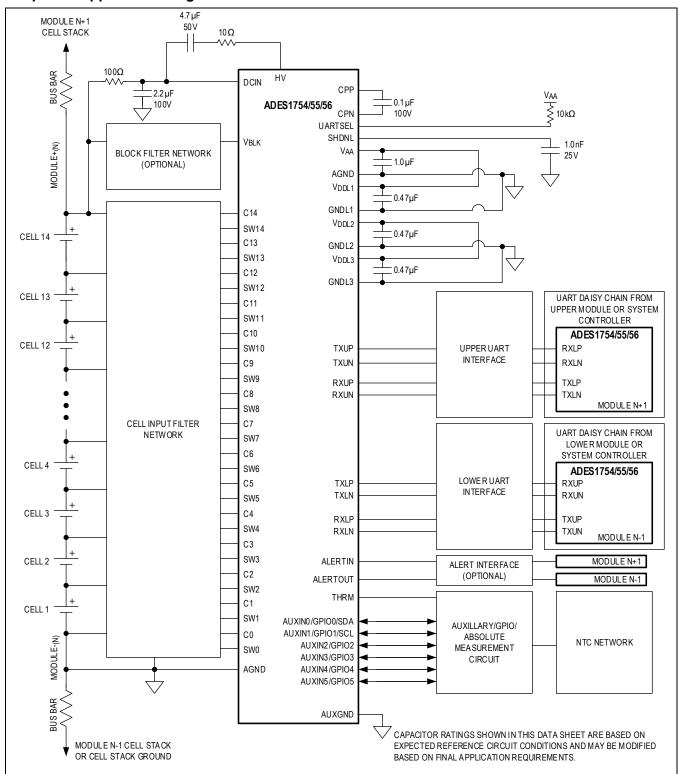

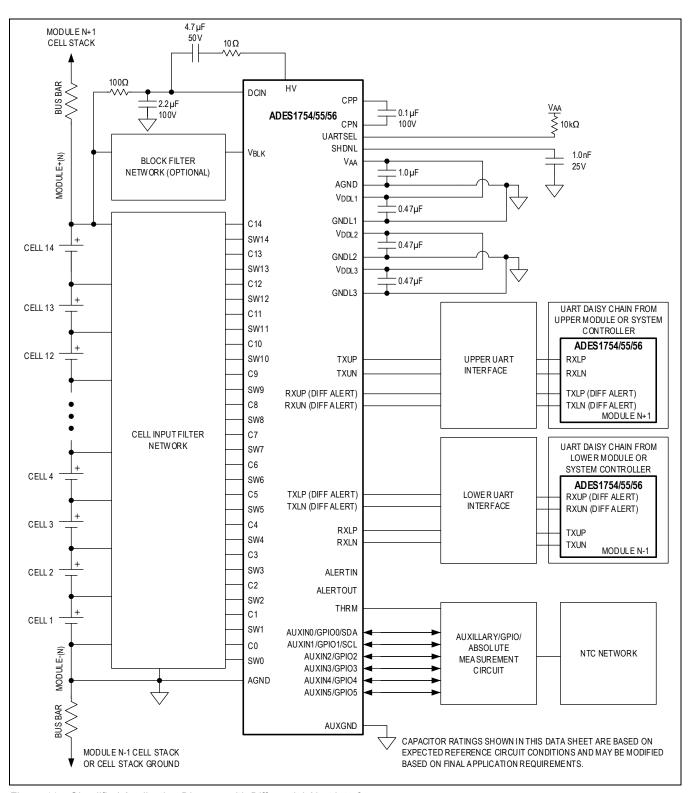

The ADES1754/ADES1755/ADES1756 are flexible data-acquisition systems for the management of high-voltage and low-voltage battery modules. The systems can measure 14 cell voltages and a combination of six temperatures or system voltage measurements with fully redundant measurement engines in 162µs, or perform all inputs solely with the ADC measurement engine in 99µs. Fourteen internal balancing switches rated for >300mA for cell-balancing current support extensive built-in diagnostics. Up to 32 devices can be daisy-chained to manage 448 cells and monitor 192 temperatures.

Cell and bus-bar voltages ranging from -2.5V to +5V are measured differentially over a 65V common-mode range, with a typical accuracy of  $100\mu V$ . If oversampling is enabled, up to 128 measurements per channel can be averaged internally with 14-bit resolution and combined with digital post-processing IIR filtering for increased noise immunity.

The system can shut itself down in the event of a thermal overload by measuring its own die temperature. The system uses Analog Devices' battery-management UART protocol for robust communications and supports an I<sup>2</sup>C controller interface for external device control. It is optimized to support a reduced feature set of internal diagnostics and rapid-alert communication through both embedded communication and hardware-alert interfaces.

# **Key Applications**

- Residential Battery Storage Systems

- High-Voltage Battery Stacks

- Battery-Backup Systems (UPS)

- Super-Cap Systems

- Battery-Powered Tools

- EV Charging

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- 65V Operating Voltage

- Ultra-Low Power Operation

- Shutdown Mode: 2µA

- Redundant ADC and Comparator (COMP) Acquisitions

- Simultaneous Cell and Bus-Bar Voltage Acquisitions

- 14 Cell-Voltage Measurement Channels

- 2.2mV/5mV/10mV Accuracy (-40°C to +105°C)

- 1.8mV Accuracy (+5°C to +65°C)

- 14 Cell-Balancing Switches

- >300mA Software-Programmable Balancing Current

- · Automated Balancing with Individual Cell Timers

- · Automated Balancing by Cell Voltage

- · Emergency Discharge Mode

- Six Configurable Auxiliary Inputs for Temperature, Voltage, or GPIO

- Integrated Die Temperature Measurement

- Automatic Thermal Protection

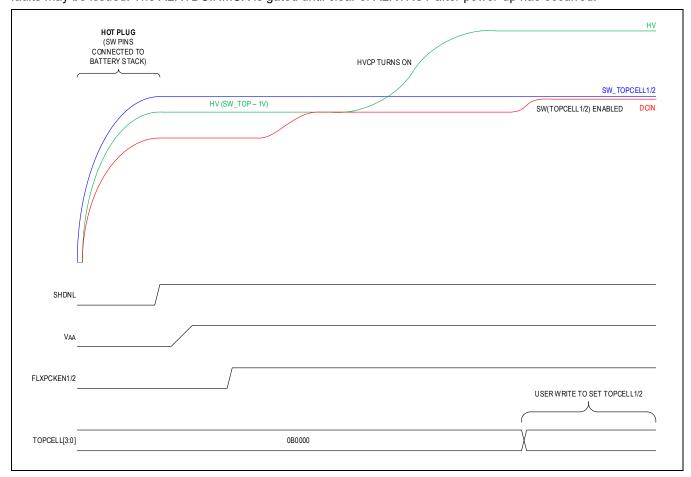

- Hot Plug-Tolerant without External Protection

- Individually Configurable Safety Alerts

- · Overvoltage, Undertemperature Faults

- · Undervoltage, Overtemperature Faults

- 1-Cell Mismatch Alert

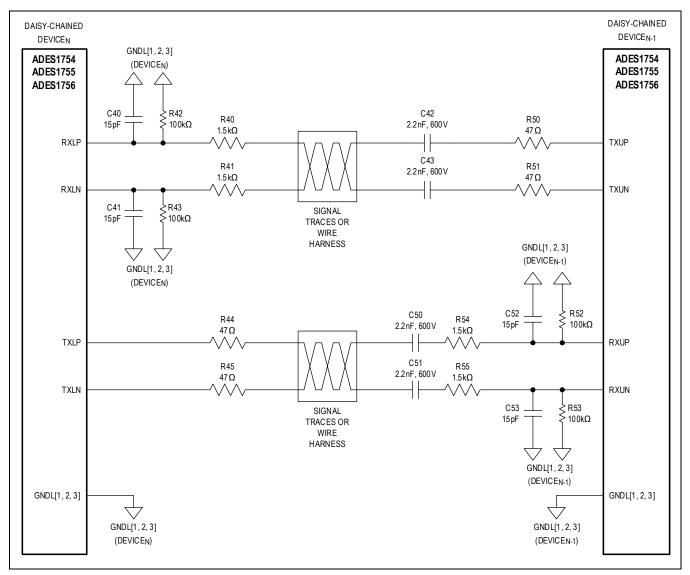

- UART. Dual UART Interface

- Battery-Management UART Protocol

- · Daisy-Chain up to 32 Devices

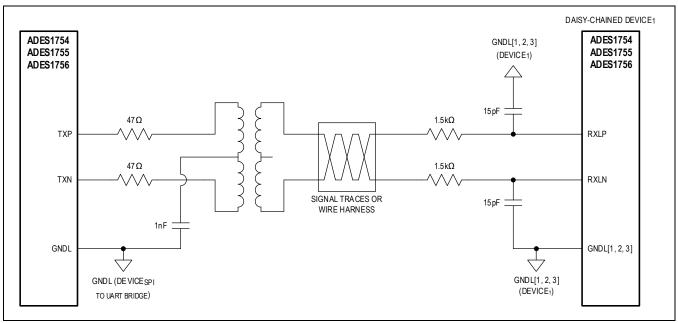

- · Inductive for Higher Galvanic Isolation

- Up to 2Mbps Baud Rate (Auto-Detect)

- 1.5µs Propagation Delay per Device

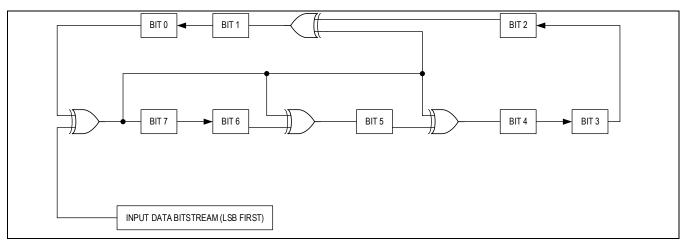

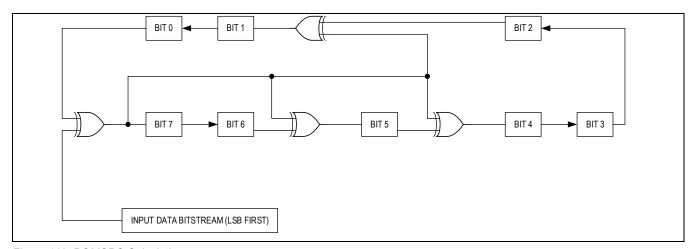

- Packet-Error Checking (PEC)

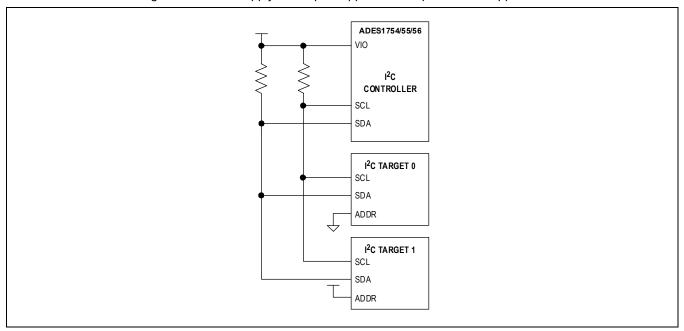

- I<sup>2</sup>C Controller

- Configurable Hardware-Alert Interfaces

- 32-Bit Unique Device ID

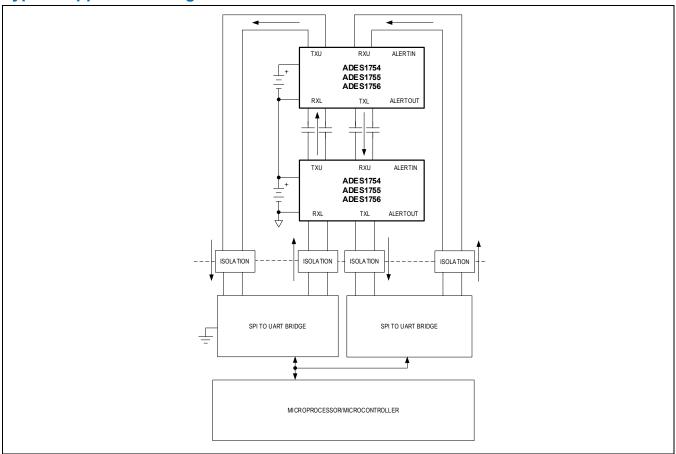

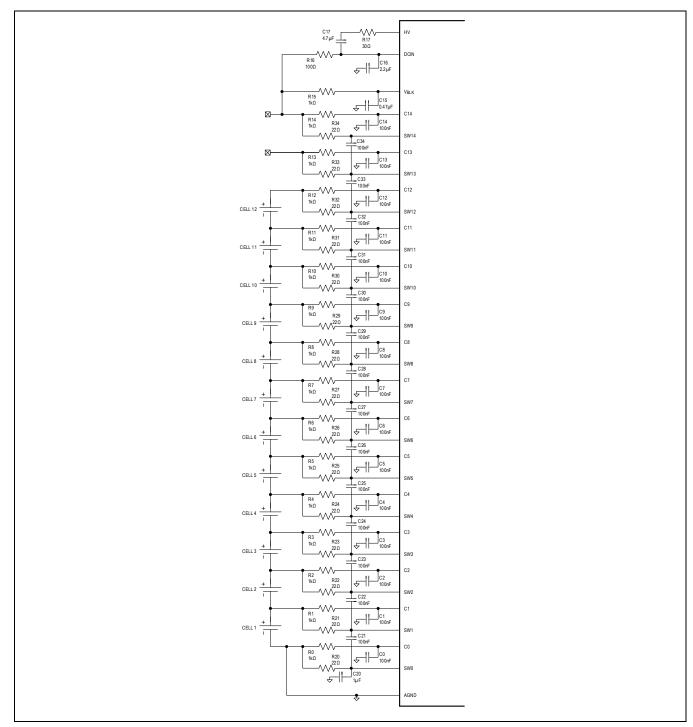

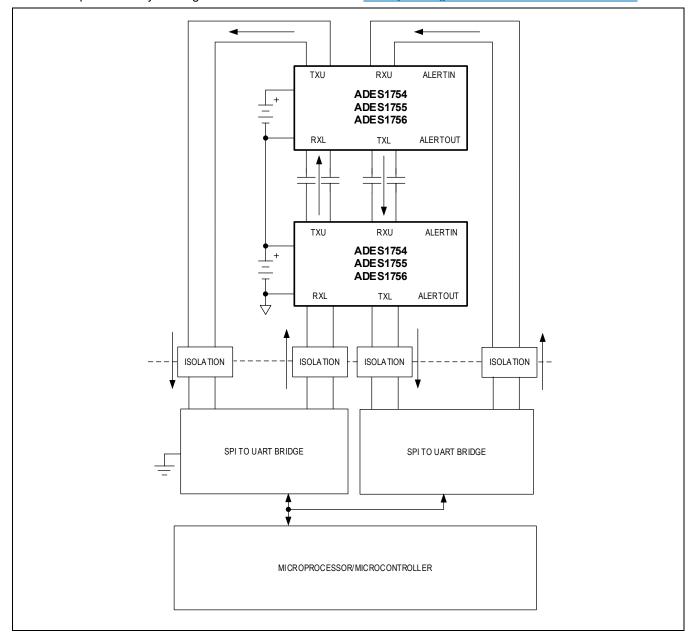

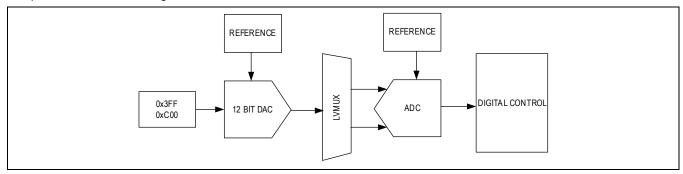

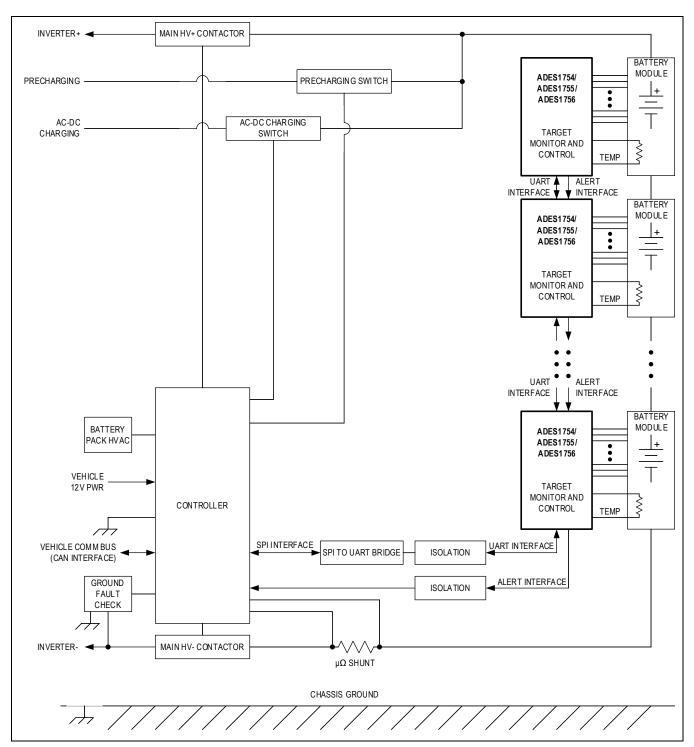

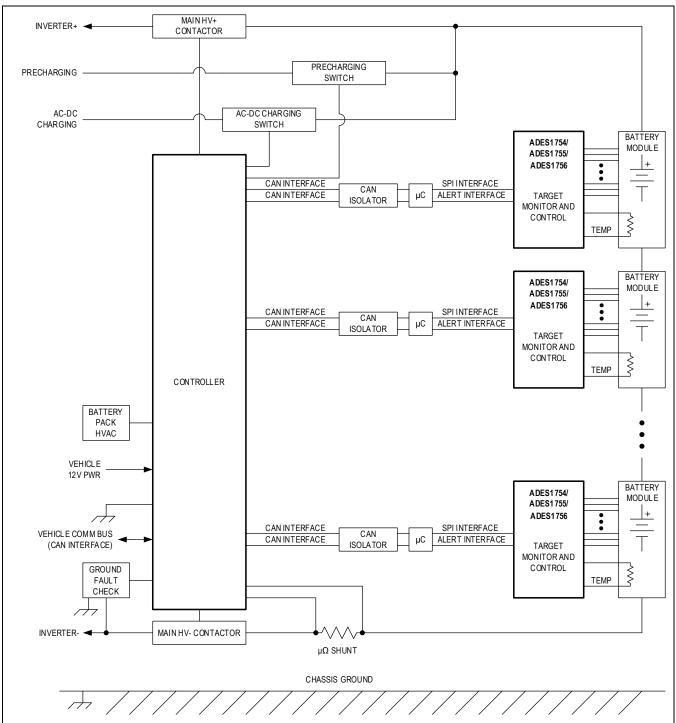

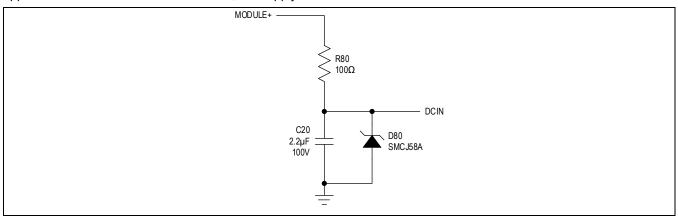

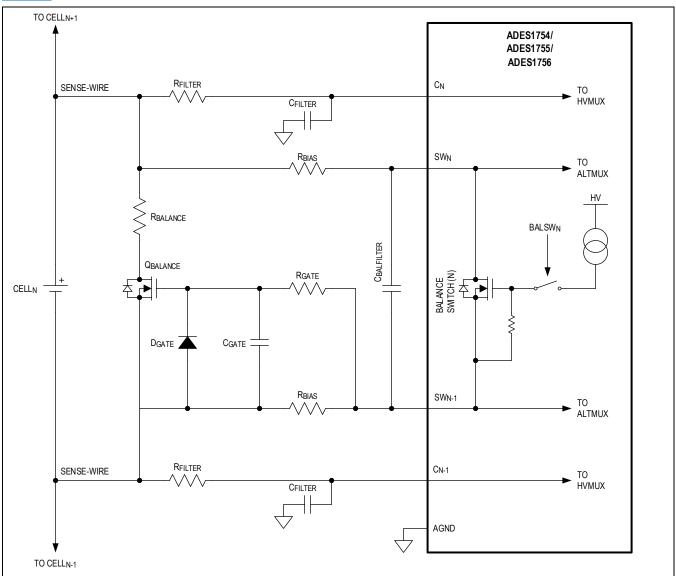

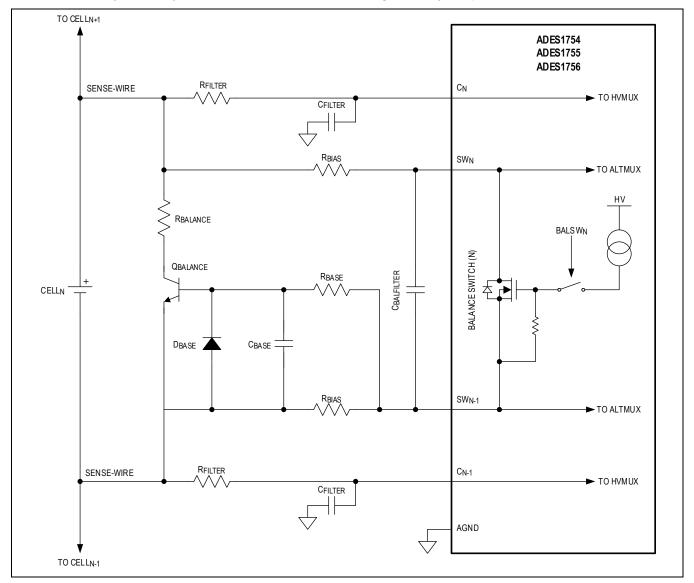

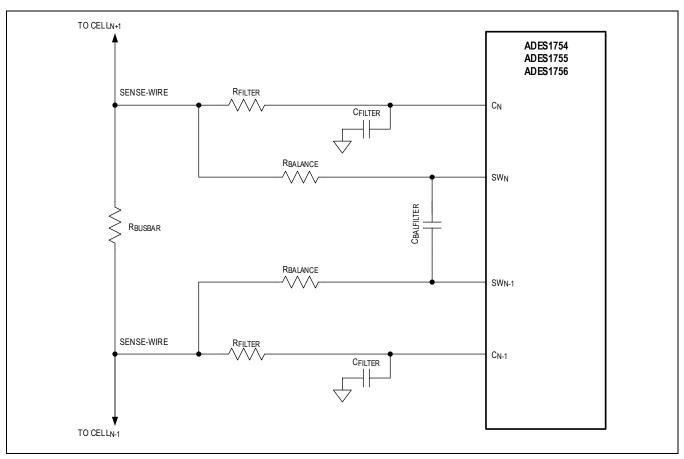

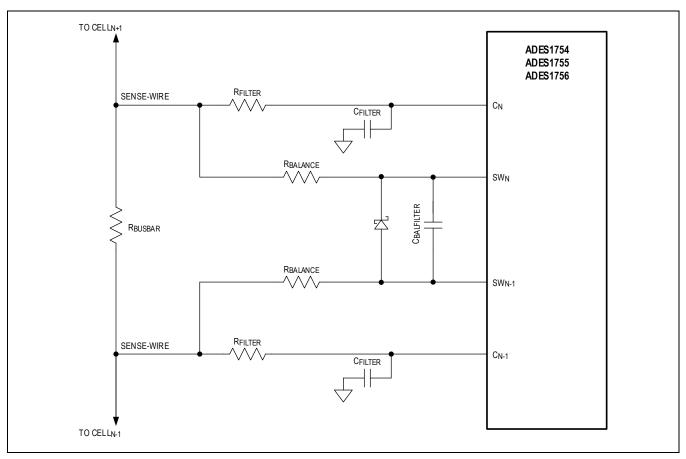

# **Typical Application Diagram**

### **Absolute Maximum Ratings**

| HV to AGND                                  | 0.3V to +80V                                 |

|---------------------------------------------|----------------------------------------------|

| DCIN, SWn, $V_{BLK}$ , Cn to AGND -0.3\72)V | $^{\prime}$ to min (V <sub>HV</sub> + 0.3 or |

| Cn to Cn-1                                  | 72V to +72V                                  |

| SWn to SWn-1                                | 0.3V to +52V                                 |

| V <sub>AA</sub> to AGND                     | 0.3V to +2.2V                                |

| V <sub>DDL1</sub> to GNDL1                  | 0.3V to +2.2V                                |

| V <sub>AA</sub> to V <sub>DDL1</sub>        | 0.3V to +0.3V                                |

| $V_{DDL2}, V_{DDL3}$ to GNDL2, GNDL3        | -0.3V to 6.0V                                |

| AGND to GNDL1, GNDL2, GNDL3                 | 0.3V to 0.3V                                 |

| AGND to AUXGND                              | 0.3V                                         |

| GPIOn/AUXINn                                | 0.3V to V <sub>DDL2</sub> + 0.3V             |

| THRM to AGND                                | 0.3V to V <sub>AA</sub> + 0.3V               |

| SHDNL to AGND                               | 0.3V to V <sub>DCIN</sub> + 0.3V             |

|                                             |                                              |

| RXLP, RXLN, RXUP, RXUN, ALERTIN to AGND-30V to +30V                                      |

|------------------------------------------------------------------------------------------|

| TXLP, TXLN, ALERTOUT to GNDL20.3V to +6V                                                 |

| TXUP, TXUN to GNDL30.3V to +6V                                                           |

| CPP to AGND $V_{DCIN}$ – 1V to $V_{HV}$ + 1V                                             |

| CPN to AGND0.3V to V <sub>DCIN</sub> + 0.3V                                              |

| Maximum Continuous Current into Any Pin ( $\underline{\textit{Note 1}}$ ) -50mA to +50mA |

| Maximum Continuous Current into SWn Pin ( $\underline{\textit{Note 2}}$ )650mA to +650mA |

| Maximum Average Power for ESD Diodes ( <u>Note 3</u> ) 14.4W / $\sqrt{t}$                |

| Package Continuous Power (Note 4)2000mW                                                  |

| Operating Temperature Range40°C to +105°C                                                |

| Storage Temperature Range55°C to +150°C                                                  |

| Junction Temperature (Continuous)+150°C                                                  |

| Soldering Lead Temperature (10s maximum)+300°C                                           |

- **Note 1:** Balancing switches disabled.

- Note 2: One balancing switch enabled, 60s (max).

- Note 3: Average power for time period t where t is the time constant (in μs) of the transient diode current during hot-plug event. For, example, if t is 330μs, the maximum average power is 0.793W. Peak current must never exceed 2A. Actual average power during hot-plug must be calculated from the diode current waveform for the application circuit and compared to the maximum rating.

- Note 4: Multilayer board. For T<sub>A</sub> > +70°C, derate 25mW/°C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

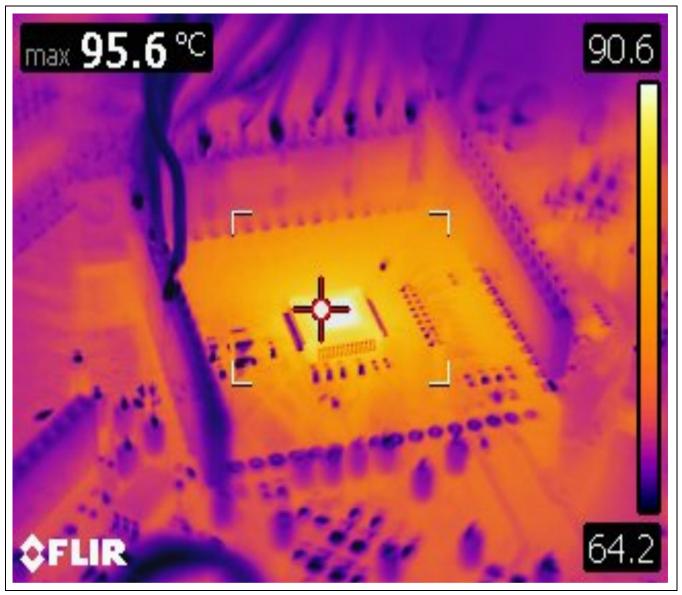

### **Package Information**

#### **LQFP**

| Package Code                           | C64+13C        |

|----------------------------------------|----------------|

| Outline Number                         | <u>21-0083</u> |

| Land Pattern Number                    | <u>90-0141</u> |

| Thermal Resistance, Four Layer Board:  |                |

| Junction to Ambient (θ <sub>JA</sub> ) | 40°C/W         |

| Junction to Case $(\theta_{JC})$       | 8°C/W          |

For the latest package outline information and land patterns (footprints), go to the <u>Package Index</u> on the Analog Devices website. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://example.com/Thermal Characterization of IC Packages">Thermal Characterization of IC Packages</a>.

#### **Electrical Characteristics**

$(V_{DCIN} = +56V, T_A = T_{MIN} \text{ to } T_{MAX} \text{ unless otherwise noted, where } T_{MIN} = -40^{\circ}\text{C} \text{ and } T_{MAX} = +105^{\circ}\text{C}.$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .

| PARAMETER                                          | SYMBOL                                                          | CONDITIONS                                                                                                                                                     | MIN                         | TYP               | MAX             | UNITS |

|----------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------|-----------------|-------|

| POWER REQUIREMENT                                  | 'S                                                              |                                                                                                                                                                |                             |                   |                 |       |

| Supply Voltage, DCIN                               | V <sub>DCIN</sub>                                               |                                                                                                                                                                | 9                           |                   | 65              | V     |

| Supply Voltage VDDL2,<br>VDDL3                     | V <sub>DDL2</sub> ,<br>V <sub>DDL3</sub> ,<br>V <sub>DDIO</sub> | V <sub>DDL2</sub> = V <sub>DDL3</sub> External overdrive (>V <sub>DDL2/3_REG</sub> ) allowed. Also used as V <sub>DDIO</sub> in I <sup>2</sup> C applications. | V <sub>DDL2/3</sub><br>_REG | 3.3               | 5.5             | V     |

| DCIN Current,<br>Shutdown Mode                     | I <sub>DCSHDN</sub>                                             | V <sub>SHDNL</sub> = 0V                                                                                                                                        |                             | 0.1               |                 | μΑ    |

| DCIN Current, Standby<br>Mode                      | I <sub>DCSTBY</sub>                                             | V <sub>SHDNL</sub> > 1.8V, UART in idle mode; not in acquisition mode; balance switches, test current sources, and alert interface disabled; <i>Note</i> 6     | 2.2                         |                   | 3.1             | mA    |

| DCIN Current, ADC<br>Acquisition Mode              | I <sub>DC_ADC</sub>                                             | All cell and auxiliary measurements enabled, OVSAMPL[2:0] = 000b; Note 6                                                                                       |                             | 4.2               | 5               | mA    |

| DCIN Current, COMP<br>Acquisition Mode             | I <sub>DC_COMP</sub>                                            | All cell and auxiliary measurements enabled, OVSAMPL[2:0] = 000b; Note 6                                                                                       |                             | 4.6               | 5.5             | mA    |

| DCIN Current, ADC + COMP Acquisition Mode          | IDC_ADCCOMP                                                     | All cell and auxiliary measurements enabled; <u>Note 6</u>                                                                                                     |                             | 5.4               | 6.4             | mA    |

| DCIN Incremental<br>Current, UART<br>Communication | I <sub>DCCOMM_</sub> UA<br>RT                                   | Baud rate = 2Mbps (0% idle time preambles mode), 200pF load on TXUP and TXUN, TXL not active, not in acquisition mode, BALSWEN, CTSTEN = 0000h; Note 6         |                             | 160               | 230             | μΑ    |

| HV Current, ADC<br>Acquisition Mode                | I <sub>HVMEAS</sub>                                             | ADC-only acquisition, all cells and auxiliary channels enabled, $V_{HV} = V_{DCIN} + 5.5V$                                                                     | 0.7                         | 0.9               | 1.1             | mA    |

| HV Current, Comparator Scan Mode                   | I <sub>HVCOMP</sub>                                             | COMP only acquisition, all cells and auxiliary channels enabled, $V_{HV} = V_{DCIN} + 5.5V$                                                                    | 0.7                         | 0.9               | 1.1             | mA    |

| Incremental HV Current,<br>Cell-Balancing Mode     | I <sub>HVBAL</sub>                                              | V <sub>HV</sub> = V <sub>DCIN</sub> + 5.5V, n balancing switches enabled                                                                                       | (n + 1) x<br>5              | (n + 1) x<br>15.5 | (n + 1) x<br>26 | μΑ    |

| CELL VOLTAGE INPUTS                                | S (Cn, V <sub>BLK</sub> )                                       |                                                                                                                                                                |                             |                   |                 |       |

| Differential Input Range                           | V <sub>CELLn</sub>                                              | Unipolar mode, <u>Note 7</u><br>Bipolar mode,                                                                                                                  | 0                           |                   | 5               | V     |

| Common-Mode Input                                  | V <sub>CnCM</sub>                                               | Note 7  Not connected to SWn inputs                                                                                                                            | -2.5                        |                   | 2.5             |       |

| Range                                              | ▼ CnCivi                                                        | •                                                                                                                                                              | 0                           |                   | 65              | V     |

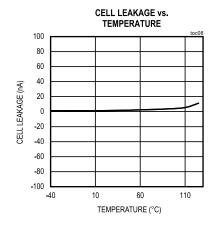

| Input Leakage Current                              | ILKG_Cn                                                         | Not in acquisition mode, V <sub>Cn</sub> = 65V                                                                                                                 | -100                        | ±10               | 100             | nA    |

| V <sub>BLK</sub> Input Resistance                  | R <sub>VBLK</sub>                                               | V <sub>BLK</sub> = V <sub>DCIN</sub> = 57.6V                                                                                                                   | 4.5                         | 10                | 20              | ΜΩ    |

| HVMUX Switch<br>Resistance                         | R <sub>HVMUX</sub>                                              | CTSTDAC[3:0] = Fh                                                                                                                                              | 1.7                         | 3.3               | 5               | kΩ    |

| CELL-BALANCING INPU                                | JTS (SWn)                                                       |                                                                                                                                                                |                             |                   |                 |       |

| Leakage Current                                    | I <sub>LKG_SW</sub>                                             | $V_{SW0} = 0V, V_{SWn} = 5V, V_{SWn} - 1 = 0V$                                                                                                                 | -1.0                        |                   | +1.0            | μΑ    |

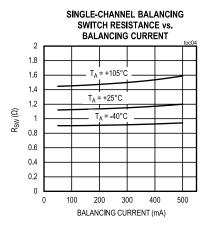

| Resistance, SWn to                                 | R <sub>SW</sub>                                                 | BALSWEN[n-1] = 1, I <sub>SWn</sub> = 100mA<br>BALSWEN[n-1] = 1, I <sub>SWn</sub> = 300mA; <u>Note</u>                                                          | 0.5                         | 1.25              | 2.25            | Ω     |

| SWn-1                                              |                                                                 | <u>8</u>                                                                                                                                                       |                             | 1.3               |                 |       |

$(V_{DCIN} = +56V, T_A = T_{MIN} \text{ to } T_{MAX} \text{ unless otherwise noted, where } T_{MIN} = -40^{\circ}\text{C} \text{ and } T_{MAX} = +105^{\circ}\text{C}. \text{ Typical values are at } T_A = +25^{\circ}\text{C}.$

| Operation is with the recon | nmend application | n circuit. ( <u>Note 5</u> )) |

|-----------------------------|-------------------|-------------------------------|

|                             |                   |                               |

| Operation is with the recon                |                       |                                                                                                                                              |      |      |                         |       |

|--------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------------------------|-------|

| PARAMETER                                  | SYMBOL                | CONDITIONS                                                                                                                                   | MIN  | TYP  | MAX                     | UNITS |

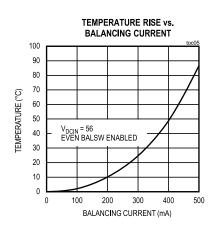

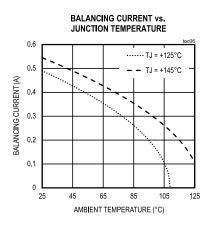

| Maximum Allowed<br>Balancing Current       | I <sub>BAL_MAX</sub>  | T <sub>J</sub> = +105°C, CBMEASEN = 0x00,<br>FLXPCKEN1/2 = 0, all even or all odd<br>channels enabled. <i>Note</i> 9                         |      | 650  |                         | mA    |

| <b>AUXILIARY INPUTS (AU</b>                | XINn)                 |                                                                                                                                              |      |      |                         |       |

| Input Voltage Range                        | V <sub>AUXIN</sub>    | V <sub>ADCREF</sub> = V <sub>THRM</sub> or V <sub>REF</sub> based on AUXREFSEL                                                               | 0    |      | V <sub>ADCRE</sub><br>F | V     |

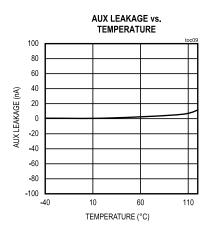

| Input Leakage Current                      | I <sub>LKG_AUX</sub>  | Not in acquisition mode,<br>V <sub>AUXINn</sub> = 1.65V                                                                                      | -400 | +10  | +400                    | nA    |

| THRM OUTPUT                                |                       |                                                                                                                                              |      |      |                         |       |

| Switch Resistance, V <sub>AA</sub> to THRM | R <sub>THRM</sub>     |                                                                                                                                              |      | 25   | 70                      | Ω     |

| Leakage Current                            | I <sub>LKG_THRM</sub> | $V_{THRM} = V_{AA}$                                                                                                                          | -1   |      | +1                      | μA    |

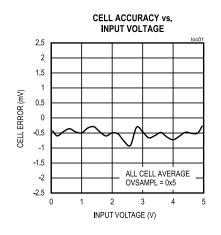

| MEASUREMENT ACCUR                          | RACY                  | 1                                                                                                                                            | I    |      | l                       |       |

|                                            |                       | Unipolar mode; V <sub>CELLn</sub> = 3.6V;                                                                                                    |      |      |                         |       |

|                                            |                       | SCANMODE = 0x0, 0x1; Note 10<br>Unipolar mode; $0.2V \le V_{CELLn} \le 4.8V$ ;                                                               |      | ±200 |                         | μV    |

|                                            |                       | +5°C < temp < +65°C; SCANMODE = 0x0, 0x1; <i>Note 10</i>                                                                                     | -1.8 |      | +1.8                    |       |

|                                            | ent                   | Unipolar mode; $0.2V \le V_{CELLn} \le 4.8V$ ; - $40^{\circ}C < temp < +105^{\circ}C$ ; SCANMODE = $0x0$ , $0x1$ ; <u>Note 10</u> (ADES1754) | -2.2 |      | +2.2                    |       |

|                                            |                       | Unipolar mode; $0.2V \le V_{CELLn} \le 4.8V$ ; - $40^{\circ}C < temp < +105^{\circ}C$ ; SCANMODE = $0x0$ , $0x1$ ; <u>Note 10</u> (ADES1755) | -5   |      | +5                      | mV    |

| ADC Measurement                            |                       | Unipolar mode; $0.2V \le V_{CELLn} \le 4.8V$ ; - $40^{\circ}C < temp < +105^{\circ}C$ ; SCANMODE = $0x0$ , $0x1$ ; <u>Note 10</u> (ADES1756) | -10  |      | +10                     |       |

| Error, HVMUX Inputs                        | V <sub>CELLnERR</sub> | Bipolar mode; V <sub>CELLn</sub> = 1.1V;<br>SCANMODE = 0x0, 0x1; <i>Note 10</i>                                                              |      | ±200 |                         | μV    |

|                                            |                       | Bipolar mode; $-2.3V \le V_{CELLn} \le +2.3V$ ;<br>+5°C < temp < +65°C;<br>SCANMODE = 0x0, 0x1; Note 10                                      | -1.8 |      | +1.8                    |       |

|                                            |                       | Bipolar mode; -2.3V ≤ V <sub>CELLn</sub> ≤ +2.3V; -<br>40°C < temp < +105°C;<br>SCANMODE = 0x0, 0x1; <u>Note 10</u><br>(ADES1754)            | -2.2 |      | +2.2                    |       |

|                                            |                       | Bipolar mode; -2.3V ≤ V <sub>CELLn</sub> ≤ +2.3V; -<br>40°C < temp < +105°C;<br>SCANMODE = 0x0, 0x1; <u>Note 10</u><br>(ADES1755)            | -5   |      | +5                      | mV    |

|                                            |                       | Bipolar mode; -2.3V ≤ V <sub>CELLn</sub> ≤ +2.3V; -<br>40°C < temp < +105°C;<br>SCANMODE = 0x0, 0x1; <u>Note 10</u><br>(ADES1756)            | -10  |      | +10                     |       |

| ADC Measurement<br>Error, ALTMUX Inputs    | V <sub>SWnERR</sub>   | Unipolar mode; V <sub>CELL</sub> = 3.6V;<br>SCANMODE = 0x0, 0x1; <u>Note 10</u>                                                              |      | ±200 |                         | μV    |

$(V_{DCIN} = +56V, T_A = T_{MIN} \text{ to } T_{MAX} \text{ unless otherwise noted, where } T_{MIN} = -40^{\circ}\text{C} \text{ and } T_{MAX} = +105^{\circ}\text{C}. \text{ Typical values are at } T_A = +25^{\circ}\text{C}.$ Operation is with the recommend application circuit. (Note 5))

| PARAMETER                                             | SYMBOL                  | CONDITIONS                                                                                            | MIN  | TYP  | MAX  | UNITS             |

|-------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|-------------------|

|                                                       |                         | Unipolar mode; $0.2V \le V_{CELLn} \le 4.8V$ ;<br>SCANMODE = 0x0, 0x1; <u>Note 10</u><br>(ADES1754)   | -2.2 |      | +2.2 |                   |

|                                                       |                         | Unipolar mode; 0.2V ≤ V <sub>CELLn</sub> ≤ 4.8V;<br>SCANMODE = 0x0, 0x1; <u>Note 10</u><br>(ADES1755) | -5   |      | +5   | mV                |

|                                                       |                         | Unipolar mode; 0.2V ≤ V <sub>CELLn</sub> ≤ 4.8V;<br>SCANMODE = 0x0, 0x1; <u>Note 10</u><br>(ADES1756) | -10  |      | +10  |                   |

|                                                       |                         | Bipolar mode; V <sub>CELLn</sub> = 1.1V;<br>SCANMODE = 0x0, 0x1; <u>Note 10</u>                       |      | ±200 |      | μV                |

|                                                       |                         | Bipolar mode; 0 ≤ V <sub>CELLn</sub> ≤ 2.3V;<br>SCANMODE = 0x0, 0x1 (ADES1754)                        | -2.2 |      | +2.2 |                   |

|                                                       |                         | Bipolar mode; $0 \le V_{CELLn} \le 2.3V$ ;<br>SCANMODE = 0x0, 0x1 (ADES1755)                          | -5   |      | +5   | mV                |

|                                                       |                         | Bipolar mode; $0 \le V_{CELLn} \le 2.3V$ ;<br>SCANMODE = 0x0, 0x1 (ADES1756)                          | -10  |      | +10  |                   |

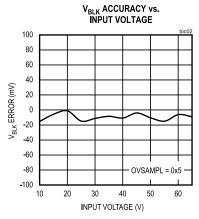

| ADC Measurement<br>Error, V <sub>BLK</sub> Input      | V <sub>BLKERR</sub>     | 9V ≤ V <sub>BLK</sub> ≤ 64.4V; V <sub>DCIN</sub> = 64.4V;<br>SCANMODE = 0x0, 0x1; <u>Note 11</u>      | -160 |      | +160 | mV                |

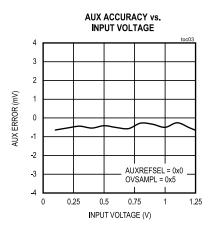

| ADC Measurement<br>Error, Ratiometric<br>AUXIN Inputs | V <sub>OS_AUX_RAT</sub> | AUXREF[n] = 0b; SCANMODE = 0x0,<br>0x1; OVSAMPL != 0x0; <u>Note 11</u>                                | -3.5 |      | +3.5 | mV                |

| ADC Measurement<br>Error, Absolute AUXIN<br>Inputs    | Vos_aux_abs             | AUXREF[n] = 1b; SCANMODE = 0x0,<br>0x1; <u>Note 11</u>                                                | -4   |      | +4   | mV                |

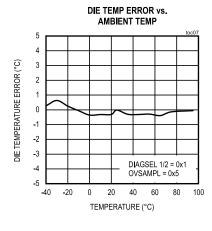

| Total Measurement Error, Die Temperature              | T <sub>DIE_ERR</sub>    | T <sub>J</sub> = -40°C to +105°C; OVSAMPL[2:0] = 000b; <i>Note 8</i>                                  | -5   | 0    | +5   | °C                |

| Cell Input Referred<br>Noise                          | V <sub>CELLNOISE</sub>  | OVSAMPL[2:0] = 0x3h; <u>Note 8</u>                                                                    |      | 250  |      | μV <sub>RMS</sub> |

| Auxiliary Input Referred Noise                        | V <sub>AUXNOISE</sub>   | OVSAMPL[2:0] = 0x3h; <u>Note 8</u>                                                                    |      | 50   |      | μV <sub>RMS</sub> |

| Differential Nonlinearity (Any Conversion)            | DNL                     |                                                                                                       |      | ±1.0 |      | LSb               |

| ADC Resolution                                        |                         |                                                                                                       | 12   |      |      | bits              |

| Level-Shifting Amplifier<br>Offset                    | V <sub>OS_LSAMP</sub>   | DIAGSEL[2:0] = 011b; <u>Note 12</u>                                                                   | -2   | +0.1 | +2   | mV                |

| COMPARATOR                                            |                         |                                                                                                       |      |      |      |                   |

| Input Common-Mode<br>Range                            | V <sub>CM_COMP</sub>    |                                                                                                       | 0    |      | 65   | V                 |

| Input Differential Mode<br>Range                      | V <sub>DM_COMP</sub>    |                                                                                                       | 0    |      | 5    | V                 |

| Comparator Accuracy                                   | Vos_comp_c              | 0.2V ≤ V <sub>CELLn</sub> ≤ 4.8V                                                                      | -20  |      | +20  | mV                |

$0V \le V_{AUXn} \le V_{AA}$

$V_{DCIN} \ge 12V$

$V_{DCIN} = 9V$

ELL

V<sub>OS\_COMP\_A</sub>

UX

V<sub>IL\_SHDNL</sub>

$V_{IH\_SHDNL}$

V<sub>SHDNLIMIT</sub>

**CELL**

AUX

Comparator Accuracy

Input Low Voltage

Input High Voltage

Regulated Voltage

SHDNL INPUT AND CHARGE PUMP

mV

V

٧

٧

+20

0.6

14

-20

1.8

7

10.8

8.5

$(V_{DCIN} = +56V, T_A = T_{MIN} \text{ to } T_{MAX} \text{ unless otherwise noted, where } T_{MIN} = -40^{\circ}\text{C} \text{ and } T_{MAX} = +105^{\circ}\text{C}.$  Typical values are at  $T_A = +25^{\circ}\text{C}$ . Operation is with the recommend application circuit. (*Note 5*))

| PARAMETER                                                                     | SYMBOL                           | n circuit. ( <u>Note 5</u> ))  CONDITIONS                                       | MIN                             | TYP                    | MAX                             | UNITS              |

|-------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------|---------------------------------|------------------------|---------------------------------|--------------------|

|                                                                               |                                  |                                                                                 |                                 |                        |                                 |                    |

| Pull-down Resistance                                                          | R <sub>FORCEPOR</sub>            | FORCEPOR = 1                                                                    | 200                             | 500                    | 800                             | Ω                  |

| Input Leakage Current                                                         | I <sub>LKG_SHDNL</sub>           | V <sub>SHDNL</sub> = 3.3V                                                       |                                 |                        | 1                               | μΑ                 |

| -                                                                             |                                  | V <sub>SHDNL</sub> = 65V                                                        |                                 | 40                     | 75                              | <b>I</b> ·         |

| Charge Pump Current -<br>UARTL/UARTU                                          | I <sub>SHDNL</sub>               | V <sub>SHDNL</sub> < V <sub>SHDNLIMIT</sub> ; baud rate = 2Mbps; <u>Note 13</u> | 15                              | 117                    | 350                             | μΑ                 |

| UARTSEL                                                                       |                                  |                                                                                 |                                 |                        |                                 | Ī                  |

| UARTSEL Input High<br>Voltage                                                 | V <sub>IH_UARTSEL</sub>          |                                                                                 | 0.7 x<br>V <sub>AA</sub>        |                        |                                 | V                  |

| GENERAL-PURPOSE I/C                                                           | (GPIOn)                          |                                                                                 |                                 |                        |                                 |                    |

| Input Low Voltage                                                             | $V_{\text{IL\_GPIO}}$            |                                                                                 |                                 |                        | 0.3 x<br>V <sub>DDL2</sub>      | ٧                  |

| Input High Voltage                                                            | V <sub>IH_GPIO</sub>             |                                                                                 | 0.7 x<br>V <sub>DDL2</sub>      |                        |                                 | <b>V</b>           |

| Pull-down Resistance                                                          | $R_{GPIO}$                       | AUXINn/GPIOn configured as GPIO input                                           | 0.5                             | 2                      | 7.5                             | МΩ                 |

| Output Low Voltage                                                            | V <sub>OL_GPIO</sub>             | I <sub>SINK</sub> = 4mA                                                         |                                 |                        | 0.4                             | V                  |

| Output High Voltage                                                           | V <sub>OH_GPIO</sub>             | I <sub>SOURCE</sub> = 4mA                                                       | V <sub>DDL2</sub> - 0.4         |                        |                                 | V                  |

| ALERTIN                                                                       |                                  |                                                                                 | -                               |                        |                                 |                    |

| ALERTIN Comparator<br>Threshold                                               | V <sub>CL</sub>                  |                                                                                 | V <sub>DDL2/3</sub><br>/2 - 0.4 | V <sub>DDL2/3</sub> /2 | V <sub>DDL2/3</sub><br>/2 + 0.4 | V                  |

| ALERTIN Comparator<br>Hysteresis                                              | V <sub>HYS_ALERTI</sub><br>N     |                                                                                 |                                 | 75                     |                                 | mV                 |

| ALERTIN Common-<br>Mode Voltage Bias                                          | V <sub>CM</sub>                  |                                                                                 |                                 | V <sub>DDL2/3</sub>    |                                 | V                  |

| Leakage Current                                                               | I <sub>LKG_ALERTIN</sub>         | V <sub>ALERTIN</sub> = 1.5V                                                     |                                 | ±1.0                   |                                 | μA                 |

| Input Capacitance                                                             | C <sub>ALERTIN</sub>             |                                                                                 |                                 | 2                      |                                 | pF                 |

| Bit Period                                                                    | <sup>t</sup> BIT                 | <u>Note 14</u>                                                                  |                                 | 8                      |                                 | 1/<br>fosc_16<br>M |

| ALERTIN Fall Time                                                             | talertin_fall                    | Note 8, Note 15                                                                 |                                 |                        | 0.5                             | t <sub>BIT</sub>   |

| ALERTIN Rise Time                                                             | talertin_rise                    | Note 8, Note 15                                                                 |                                 |                        | 0.5                             | t <sub>BIT</sub>   |

| ALERTIN Qualification Time                                                    | tALERTIN_QUA                     |                                                                                 |                                 | 25                     |                                 | μs                 |

| Propagation Delay (ALERTIN Port to ALERTOUT Port)                             | talert_prop                      |                                                                                 |                                 | 2.5                    | 3                               | <sup>t</sup> BIT   |

| Start-Up Time from<br>SHNDL High and V <sub>AA</sub> =<br>0V to ALERTIN Valid | t <sub>ALERTIN</sub> STA<br>RTUP |                                                                                 |                                 | 1                      |                                 | ms                 |

| ALERTOUT                                                                      |                                  |                                                                                 | 1                               |                        |                                 | <u> </u>           |

| Output Low Voltage                                                            | V <sub>OL_ALERTOU</sub>          | I <sub>SINK</sub> = 20mA                                                        |                                 |                        | 0.4                             | V                  |

| Output High Voltage                                                           | VOH_ALERTOU<br>T                 | I <sub>SOURCE</sub> = 20mA                                                      | V <sub>DDL2</sub> - 0.4         |                        |                                 | V                  |

| Leakage Current                                                               | ILKG_ALERTO<br>UT                | V <sub>ALERTOUT</sub> = 1.5V                                                    | -1                              |                        | +1                              | μA                 |

$(V_{DCIN} = +56V, T_A = T_{MIN} \text{ to } T_{MAX} \text{ unless otherwise noted, where } T_{MIN} = -40^{\circ}\text{C} \text{ and } T_{MAX} = +105^{\circ}\text{C}.$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .

| PARAMETER                                                | SYMBOL                           | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MIN                                | TYP                                         | MAX                                  | UNITS                  |

|----------------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------|--------------------------------------|------------------------|

| 3.3V Regulator Output<br>Voltage                         | V <sub>DDL2/3_REG</sub>          | 0 ≤ I <sub>DDL2/3</sub> < 30mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.2                                | 3.3                                         | 3.4                                  | V                      |

| Short-Circuit Current                                    | I <sub>DDL2/3</sub> _SC          | V <sub>DDL2/3</sub> shorted to AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30                                 |                                             |                                      | mA                     |

| 1.8V REGULATOR (V <sub>AA</sub>                          | .)                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |                                             |                                      |                        |

| 1.8V Regulator Output<br>Voltage                         | V <sub>AA</sub>                  | 0 ≤ I <sub>AA</sub> < 3mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.71                               | 1.8                                         | 1.89                                 | V                      |

| Short-Circuit Current                                    | I <sub>AA_SC</sub>               | V <sub>AA</sub> shorted to AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                 |                                             |                                      | mA                     |

| POR Threshold                                            | V <sub>1.8</sub> REG_POR<br>RISE | V <sub>AA</sub> rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1.3                                | 1.5                                         | 1.65                                 | V                      |

| FOR THIESHOID                                            | V <sub>1.8</sub> REG_POR<br>HYS  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    | 50                                          |                                      | mV                     |

| THERMAL SHUTDOWN                                         |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |                                             |                                      |                        |

| Thermal Shutdown<br>Temperature                          | T <sub>SHDN</sub>                | Temperature rising; <u>Note 8</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                    | +145                                        |                                      | °C                     |

| Thermal Shutdown Hysteresis                              | T <sub>HYS</sub>                 | Note 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                    | 15                                          |                                      | °C                     |

| HV CHARGE PUMP                                           |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |                                             |                                      |                        |

| Output Voltage (V <sub>HV</sub> -                        | V <sub>HV-DCIN</sub>             | 9V ≤ V <sub>DCIN</sub> ≤ 12V, I <sub>LOAD</sub> = 1.5mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6.5                                | 6.9                                         | 7.4                                  | V                      |

| V <sub>DCIN</sub> )                                      | VHV-DCIN                         | 12V ≤ V <sub>DCIN</sub> ≤ 65V, I <sub>LOAD</sub> = 3mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6.5                                | 6.9                                         | 7.4                                  |                        |

| Output Voltage (V <sub>HV</sub> - V <sub>TOPCELL</sub> ) | V <sub>HV</sub> -                | $14V \le V_{DCIN} \le 65V$ , $I_{LOAD} = 3mA$ , $FLXPCKEN1/2 = 1b$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8.0                                | 8.5                                         | 9.0                                  | V                      |

| Charge Pump Efficiency                                   | Eff <sub>HVCP</sub>              | V <sub>DCIN</sub> = 57.6V; <u>Note 16</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                    | 38                                          |                                      | %                      |

| OSCILLATORS                                              |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |                                             |                                      |                        |

| LFOSC Frequency                                          | f <sub>LFOSC</sub>               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32.11                              | 32.768                                      | 33.42                                | kHz                    |

| HFOSC Frequency                                          | f <sub>HFOSC</sub>               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15.68                              | 16                                          | 16.32                                | MHz                    |

| DIAGNOSTIC TEST SOL                                      | JRCES                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                    |                                             |                                      |                        |

|                                                          | 1                                | OTOTD A O(0.01 - 0b 1/ 41/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |                                             |                                      |                        |

|                                                          |                                  | CTSTDAC[3:0] = 9h, V <sub>C0</sub> < V <sub>DDL2/3</sub> - 1.4V, V <sub>DDL2/3</sub> = 3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50                                 | 62.5                                        | 75                                   |                        |

| Cell Test Source                                         | Itoto                            | 1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C0</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50<br>36                           | 62.5<br>45                                  | 75<br>54                             |                        |

| Cell Test Source<br>Current                              | I <sub>TSTCn</sub>               | 1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C0</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>1.4V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |                                             |                                      | μΑ                     |

| -                                                        | l <sub>TSTCn</sub>               | 1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C0</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>1.4V<br>CTSTDAC[3:0] = 9Fh, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>1.4V                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36                                 | 45                                          | 54                                   | - μΑ                   |

| -                                                        |                                  | 1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C0</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>1.4V<br>CTSTDAC[3:0] = 9Fh, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>+ 1.4V<br>CTSTDAC[3:0] = 9h, V <sub>Cn</sub> < V <sub>HV</sub> - 1.4V,<br>V <sub>HV</sub> = 53.5V                                                                                                                                                                                                                                                                                                                                                               | 36<br>-54                          | 45<br>-45                                   | 54<br>-36                            |                        |

| Current                                                  | I <sub>TSTCn</sub>               | $ \begin{array}{l} 1.4 \text{V}, \text{V}_{\text{DDL2/3}} = 3.3 \text{V} \\ \text{CTSTDAC}[3:0] = 6 \text{h}, \text{V}_{\text{C0}} < \text{V}_{\text{DDL2/3}} - \\ 1.4 \text{V}, \text{V}_{\text{DDL2/3}} = 3.3 \text{V} \\ \text{CTSTDAC}[3:0] = 6 \text{h}, \text{V}_{\text{C1-C14}} > \text{V}_{\text{AGND}} + \\ 1.4 \text{V} \\ \text{CTSTDAC}[3:0] = 9 \text{Fh}, \text{V}_{\text{C1-C14}} > \text{V}_{\text{AGND}} \\ + 1.4 \text{V} \\ \text{CTSTDAC}[3:0] = 9 \text{h}, \text{V}_{\text{Cn}} < \text{V}_{\text{HV}} - 1.4 \text{V}, \\ \text{V}_{\text{HV}} = 53.5 \text{V} \\ \text{CTSTDAC}[3:0] = 6 \text{h}, \text{V}_{\text{Cn}} < \text{V}_{\text{HV}} - 1.4 \text{V}, \\ \text{V}_{\text{HV}} = 53.5 \text{V} \\ \end{array} $ | 36<br>-54<br>-75                   | 45<br>-45<br>-62.5                          | 54<br>-36<br>-50                     | - μA<br>-<br>-<br>- μA |

| Current  HVMUX Test Source                               |                                  | 1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C0</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>1.4V<br>CTSTDAC[3:0] = 9Fh, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>1.4V<br>CTSTDAC[3:0] = 9h, V <sub>Cn</sub> < V <sub>HV</sub> - 1.4V,<br>V <sub>HV</sub> = 53.5V<br>CTSTDAC[3:0] = 6h, V <sub>Cn</sub> < V <sub>HV</sub> - 1.4V,<br>V <sub>HV</sub> = 53.5V<br>CTSTDAC[3:0] = 9h, V <sub>AUXINn</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V                                                                                                                                                                | 36<br>-54<br>-75<br>25             | 45<br>-45<br>-62.5<br>31.25                 | 54<br>-36<br>-50<br>37.5             |                        |

| Current  HVMUX Test Source                               | ITSTHVMUX                        | 1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C0</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>1.4V<br>CTSTDAC[3:0] = 9Fh, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>1.4V<br>CTSTDAC[3:0] = 9h, V <sub>Cn</sub> < V <sub>HV</sub> - 1.4V,<br>V <sub>HV</sub> = 53.5V<br>CTSTDAC[3:0] = 6h, V <sub>Cn</sub> < V <sub>HV</sub> - 1.4V,<br>V <sub>HV</sub> = 53.5V<br>CTSTDAC[3:0] = 9h, V <sub>AUXINn</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>AUXINn</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V                                                          | 36<br>-54<br>-75<br>25<br>18       | 45<br>-45<br>-62.5<br>31.25<br>22.5         | 54<br>-36<br>-50<br>37.5<br>27       | μΑ                     |

| Current  HVMUX Test Source Current                       |                                  | 1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C0</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>1.4V<br>CTSTDAC[3:0] = 9Fh, V <sub>C1-C14</sub> > V <sub>AGND</sub> +<br>1.4V<br>CTSTDAC[3:0] = 9h, V <sub>Cn</sub> < V <sub>HV</sub> - 1.4V,<br>V <sub>HV</sub> = 53.5V<br>CTSTDAC[3:0] = 6h, V <sub>Cn</sub> < V <sub>HV</sub> - 1.4V,<br>V <sub>HV</sub> = 53.5V<br>CTSTDAC[3:0] = 9h, V <sub>AUXINn</sub> < V <sub>DDL2/3</sub> -<br>1.4V, V <sub>DDL2/3</sub> = 3.3V<br>CTSTDAC[3:0] = 6h, V <sub>AUXINn</sub> < V <sub>DDL2/3</sub>                                                                                                | 36<br>-54<br>-75<br>25<br>18<br>50 | 45<br>-45<br>-62.5<br>31.25<br>22.5<br>62.5 | 54<br>-36<br>-50<br>37.5<br>27<br>75 |                        |

$(V_{DCIN} = +56V, T_A = T_{MIN} \text{ to } T_{MAX} \text{ unless otherwise noted, where } T_{MIN} = -40^{\circ}\text{C} \text{ and } T_{MAX} = +105^{\circ}\text{C}.$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .

| Operation is with the recon PARAMETER                         | SYMBOL                       | CONDITIONS                                              | MIN                       | TYP                 | MAX                          | UNITS  |

|---------------------------------------------------------------|------------------------------|---------------------------------------------------------|---------------------------|---------------------|------------------------------|--------|

|                                                               |                              | DIAGSEL[2:0] = 001b; <u>Note 12</u>                     | 0.99                      | 1.00                | 1.01                         |        |

| ALTREF Voltage                                                | V <sub>ALTREF</sub>          | DIAGSEL[2:0] = 001b; 5°C < temp < +65°C; <u>Note 12</u> | 0.995                     | 1.00                | 1.005                        | V      |

| ALTREF Temperature Coefficient $(\Delta V_{ALTREF}/\Delta T)$ | A <sub>ALTREF</sub>          | Note 8                                                  |                           | ±25                 |                              | ppm/°C |

| PTAT Output Voltage                                           | $V_{PTAT}$                   | T <sub>J</sub> = +120°C; <u>Note 8</u>                  |                           | 1.14                |                              | V      |

| PTAT Temperature Coefficient ( $\Delta V_{PTAT}\Delta T$ )    | A <sub>V_PTAT</sub>          | Note 8                                                  |                           | 2.87                |                              | mV/°C  |

| PTAT Temperature<br>Offset                                    | T <sub>OS_PTAT</sub>         | Note 8                                                  |                           | -4.4                |                              | °C     |

| ALERTS                                                        |                              |                                                         |                           |                     |                              |        |

| ALRTVDDL1 Threshold                                           | V <sub>VDDL1_OC</sub>        | V <sub>AA</sub> = 1.8V                                  | 1.62                      | 1.65                | 1.68                         | V      |

| ALRTVDDL2/3<br>Threshold                                      | V <sub>VDDL2/3</sub> OC      | V <sub>DDL2/3</sub> = 3.3V                              | 2.9                       | 3.0                 | 3.1                          | V      |

| ALRTGNDLn Threshold                                           | V <sub>GNDL_OC</sub>         | AGND = 0V                                               | 0.05                      | 0.15                | 0.3                          | V      |

| ALRTHVUV Threshold                                            | V <sub>HVUV</sub>            | $V_{HV} - V_{DCIN}$ falling, FLXPCKEN1/2 = 0            | 1.8                       | 2                   | 2.2                          | V      |

| ALRTHVOV Threshold                                            | V <sub>HVOV</sub>            | V <sub>HV</sub> - V <sub>DCIN</sub> rising              | 9.0                       | 9.5                 | 9.9                          | V      |

| ALRTHVHDRM<br>Threshold                                       | V <sub>HVHDRM</sub>          | ALRTHVHDRM = 0                                          | 3.0                       |                     |                              | V      |

| ALRTTEMP Threshold                                            | T <sub>ALRTTEMP</sub>        | Note 8                                                  | 115                       | 120                 | 125                          | °C     |

| ALRTTEMP Hysteresis                                           | T <sub>ALRTTEMPHY</sub><br>S | Note 8                                                  |                           | 2                   |                              | °C     |

| UART OUTPUTS (TXLP,                                           | TXLN, TXUP, TX               | (UN)                                                    |                           |                     |                              |        |

| Output Low Voltage                                            | V <sub>OL</sub>              | I <sub>SINK</sub> = 20mA                                |                           |                     | 0.4                          | V      |

| Output High Voltage<br>(TXLP, TXLN)                           | V <sub>OH</sub>              | I <sub>SOURCE</sub> = 20mA                              | V <sub>DDL2</sub> - 0.4   |                     |                              | V      |

| Output High Voltage<br>(TXUP, TXUN)                           | V <sub>OH</sub>              | I <sub>SOURCE</sub> = 20mA                              | V <sub>DDL3</sub> - 0.4   |                     |                              | V      |

| Leakage Current                                               | I <sub>LKG_TX</sub>          | V <sub>TX</sub> = 1.5V                                  | -1                        |                     | +1                           | μΑ     |

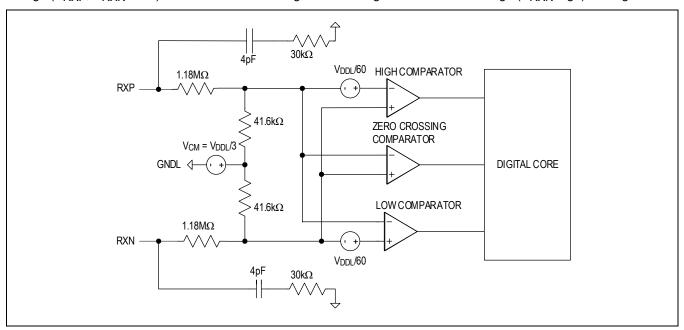

| UART INPUTS (RXLP, R                                          | XLN, RXUP, RXU               | JN)                                                     |                           |                     |                              |        |

| Input Voltage Range                                           | $V_{RX}$                     |                                                         | -25                       |                     | +25                          | V      |

| Receiver High<br>Comparator Threshold                         | V <sub>CH</sub>              | <u>Note 17</u>                                          | V <sub>AA</sub> /2 - 0.4  | V <sub>AA</sub> /2  | V <sub>AA</sub> /2 + 0.4     | V      |

| Receiver Zero-Crossing Comparator Threshold                   | V <sub>ZC</sub>              | Note 17                                                 | -0.4                      | 0                   | +0.4                         | V      |

| Receiver Low Comparator Threshold                             | V <sub>CL</sub>              | <u>Note 17</u>                                          | -V <sub>AA</sub> /2 - 0.4 | -V <sub>AA</sub> /2 | -V <sub>AA</sub> /2 +<br>0.4 | V      |

| Receiver Comparator<br>Hysteresis                             | V <sub>HYS_RX</sub>          | Note 17                                                 |                           | 75                  |                              | mV     |

| Receiver Common-<br>Mode Voltage Bias                         | V <sub>CM</sub>              | <u>Note 17</u>                                          |                           | V <sub>AA</sub> /2  |                              | V      |

| Leakage Current                                               | I <sub>LKG_RX</sub>          | $V_{RX} = 0.9V$                                         |                           | ±1.0                |                              | μA     |

| Input Capacitance<br>(RXLP, RXLN)                             | C <sub>RXL</sub>             |                                                         |                           | 4                   |                              | pF     |

| Input Capacitance<br>(RXUP, RXUN)                             | C <sub>RXU</sub>             |                                                         |                           | 4                   |                              | pF     |

$(V_{DCIN} = +56V, T_A = T_{MIN} \text{ to } T_{MAX} \text{ unless otherwise noted, where } T_{MIN} = -40^{\circ}\text{C} \text{ and } T_{MAX} = +105^{\circ}\text{C}.$  Typical values are at  $T_A = +25^{\circ}\text{C}$ .

| PARAMETER                                                                          | SYMBOL                  | CONDITIONS                                                                 | MIN                      | TYP  | MAX                      | UNITS                      |

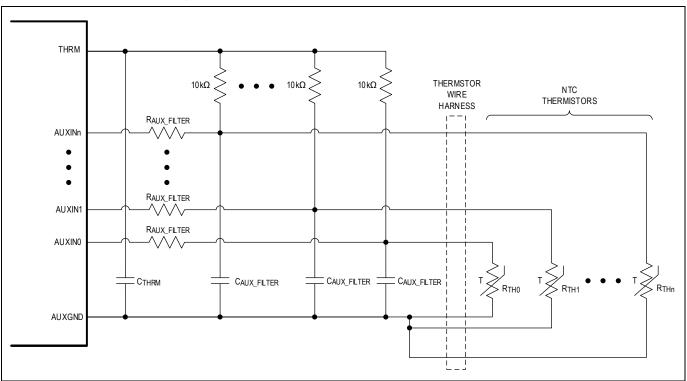

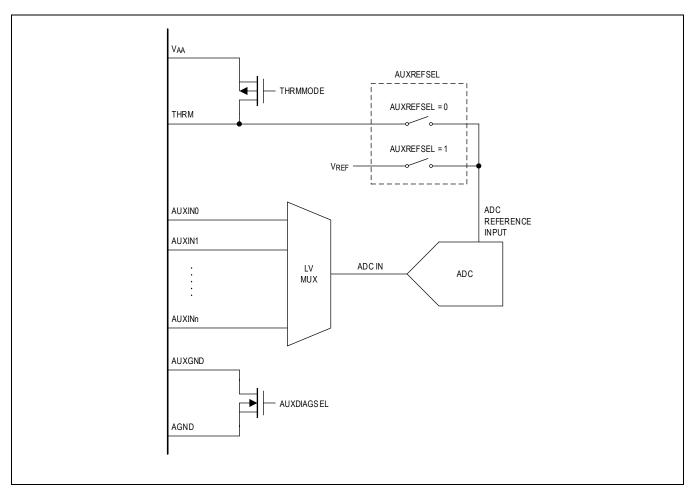

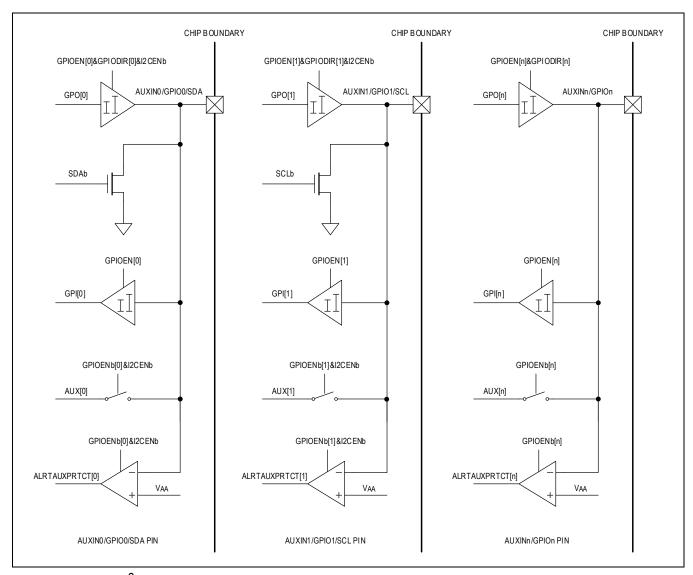

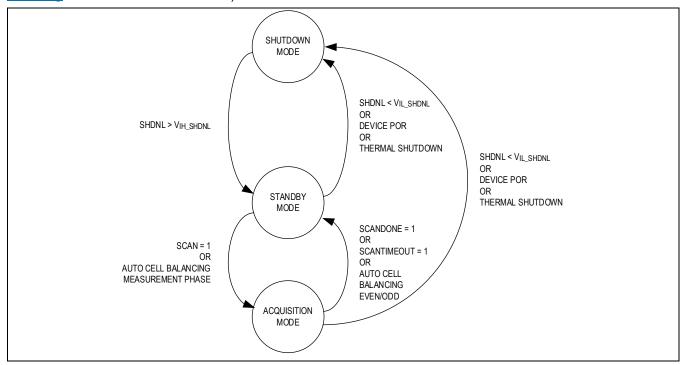

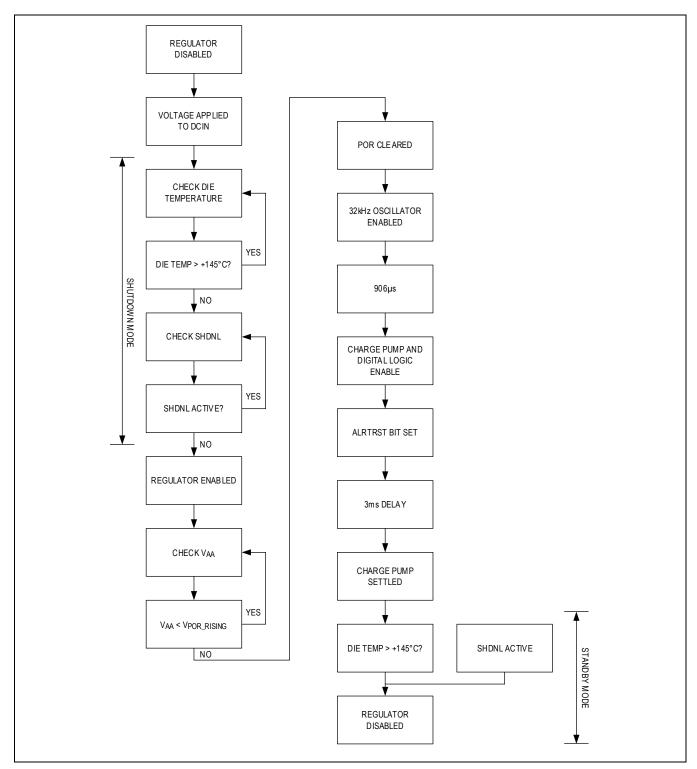

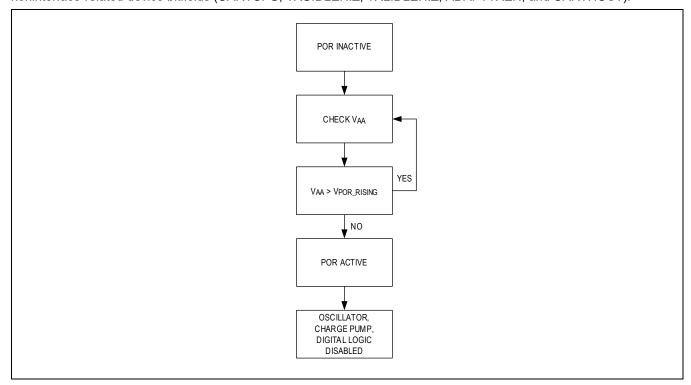

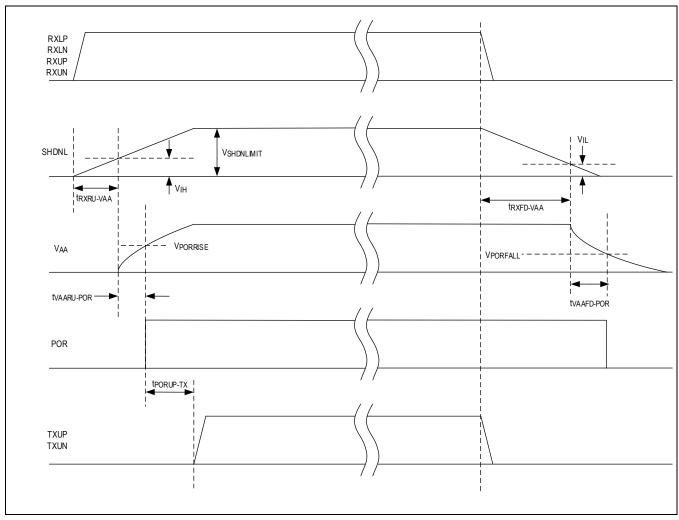

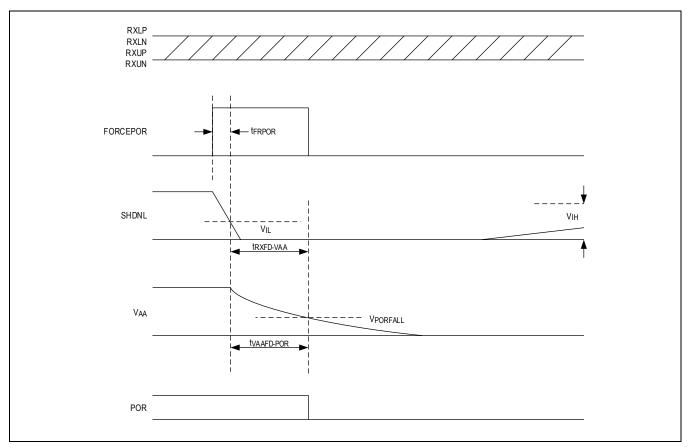

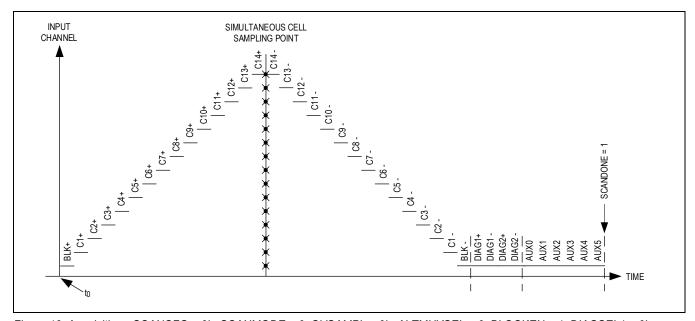

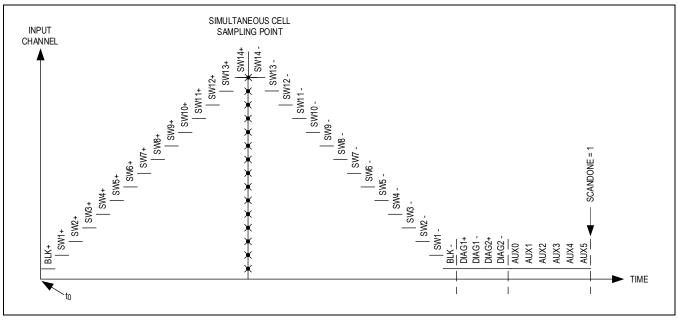

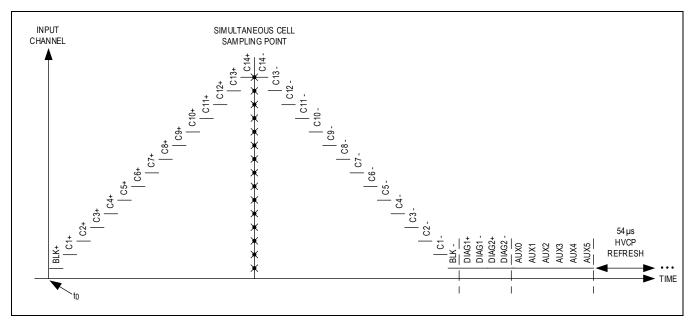

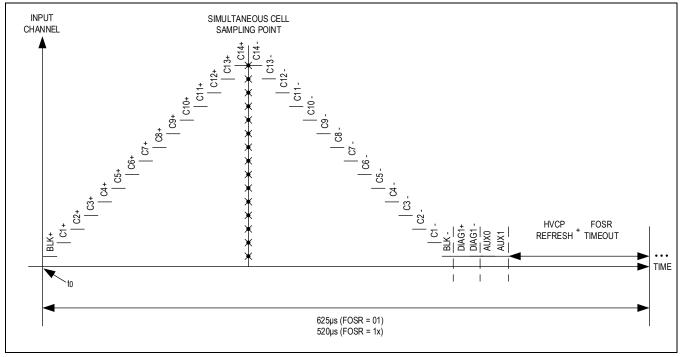

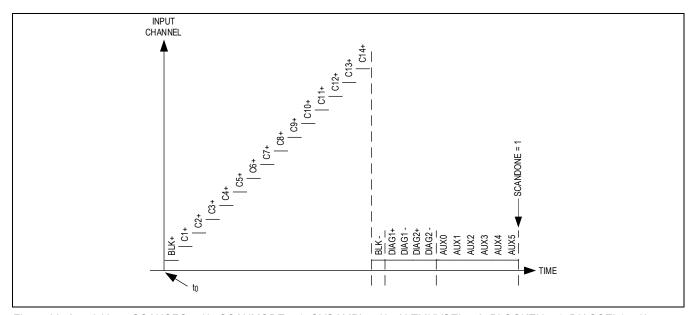

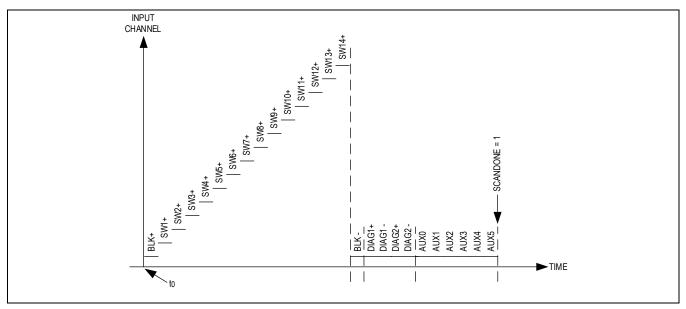

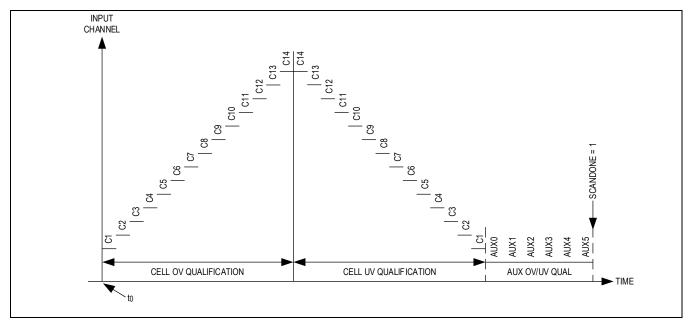

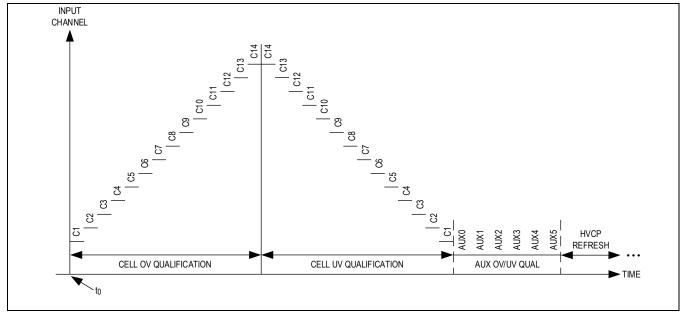

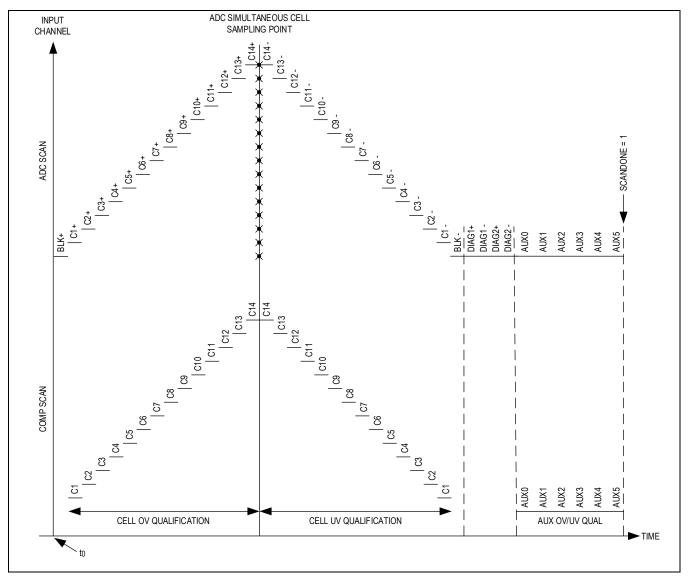

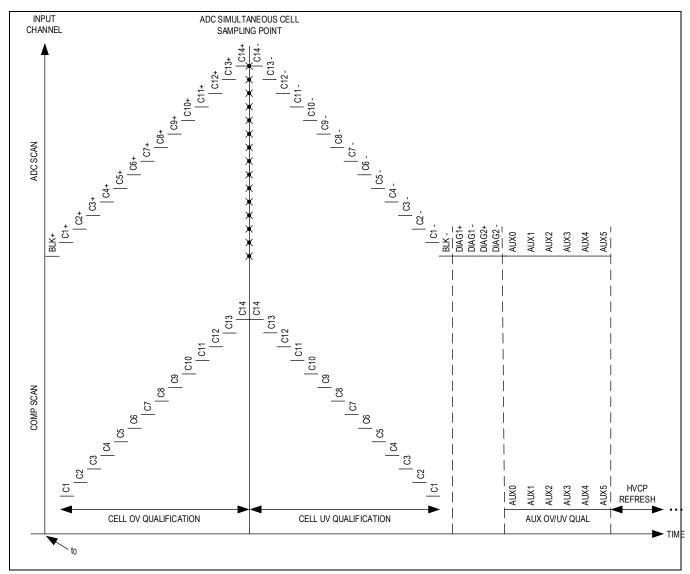

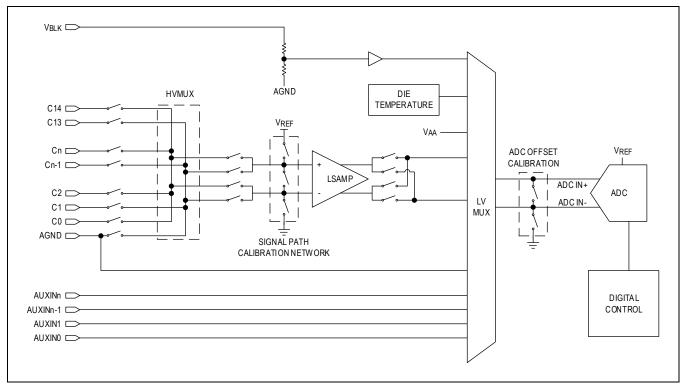

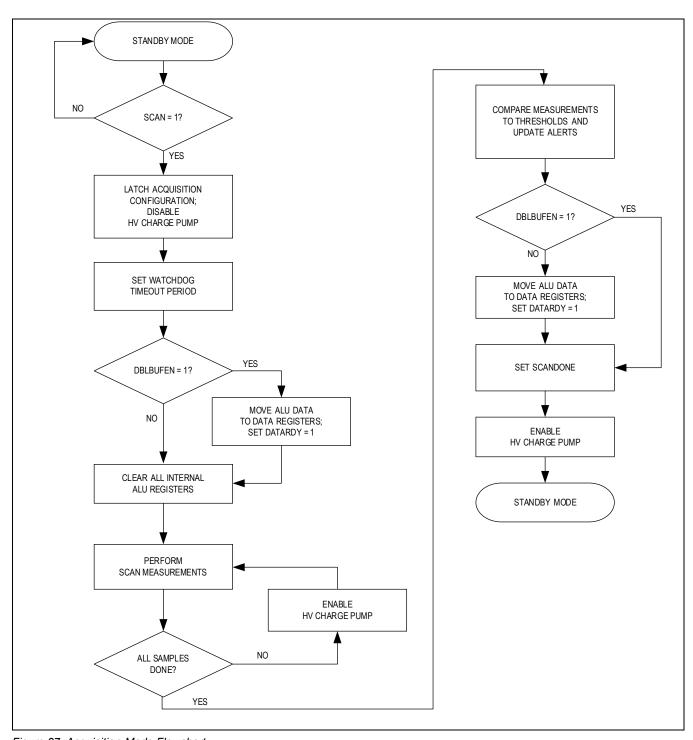

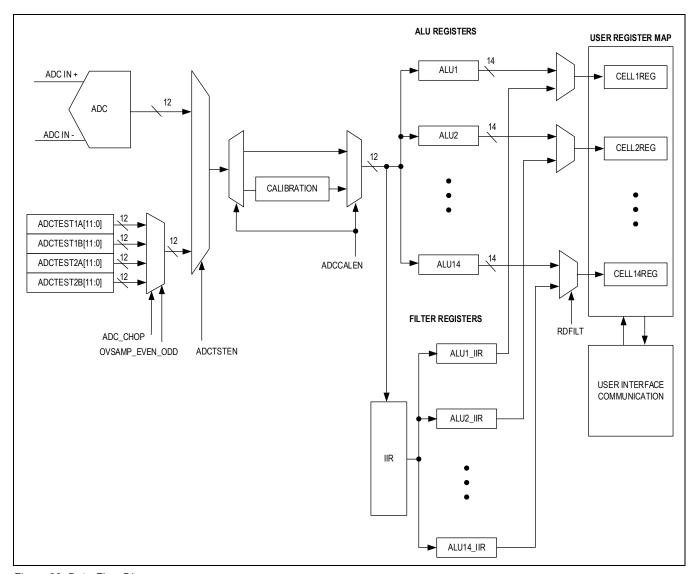

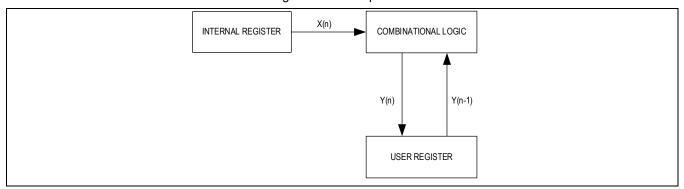

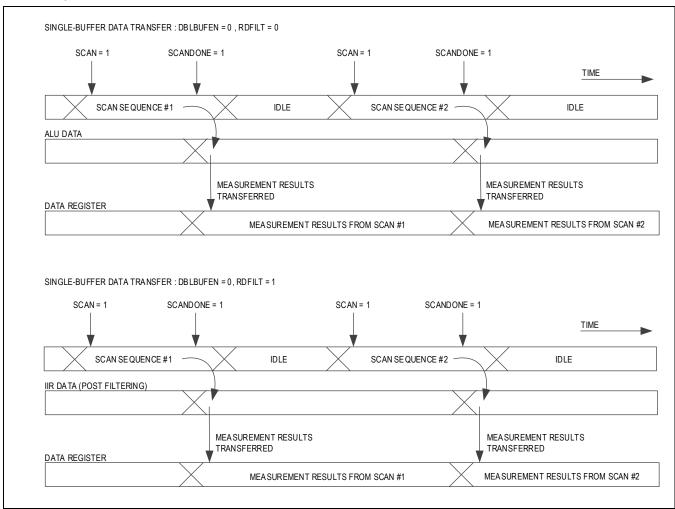

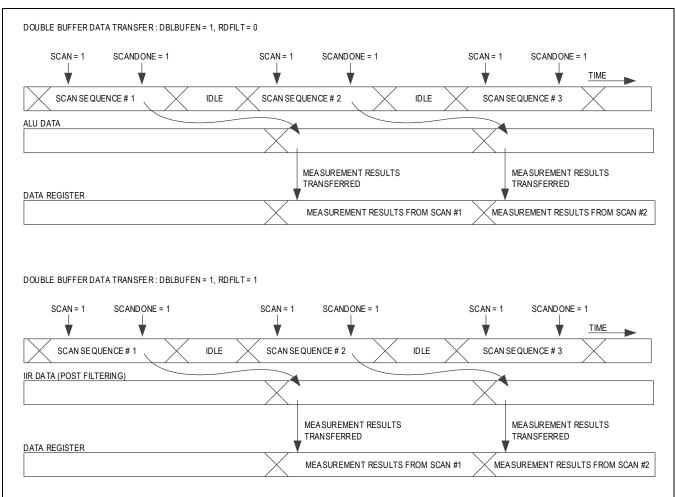

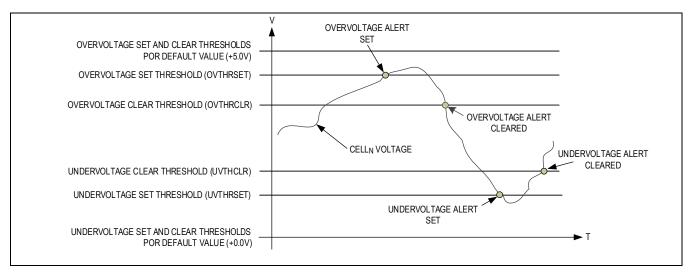

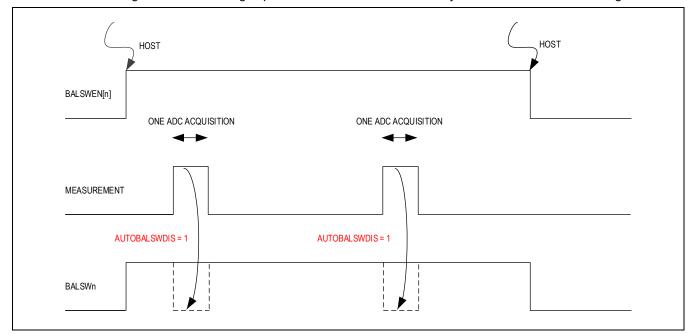

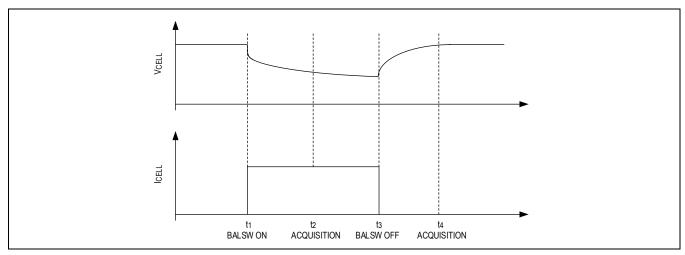

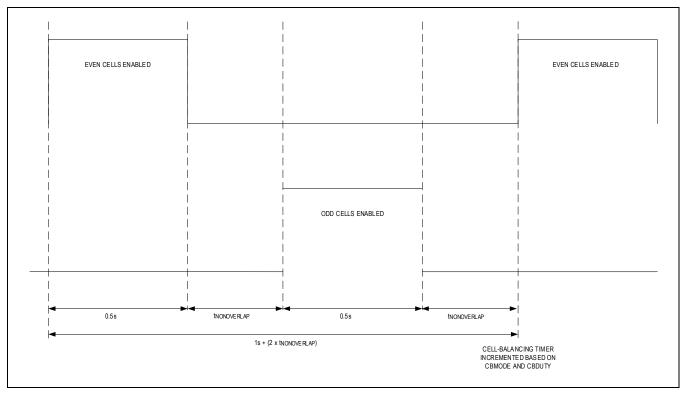

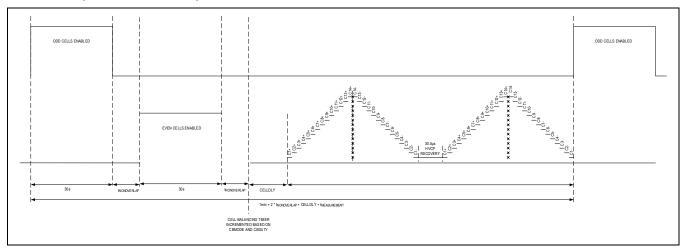

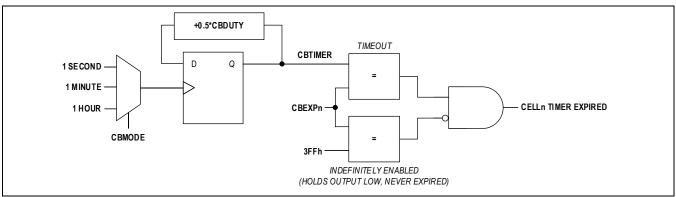

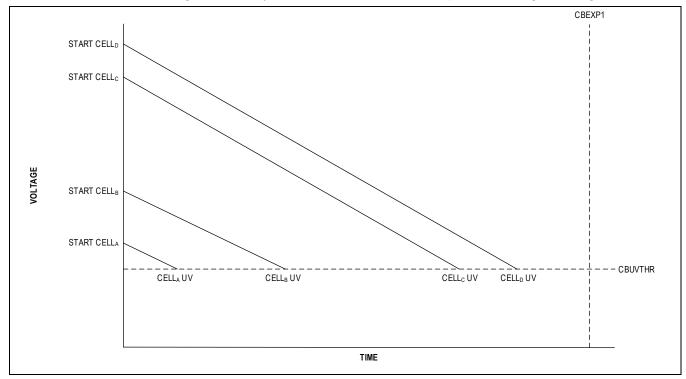

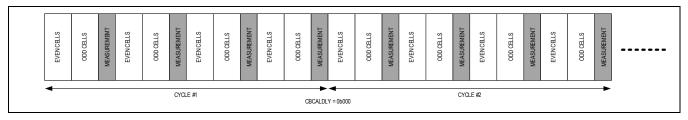

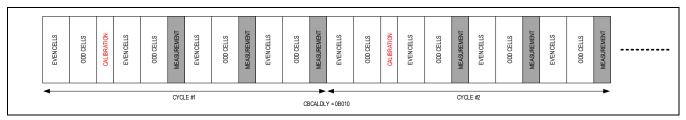

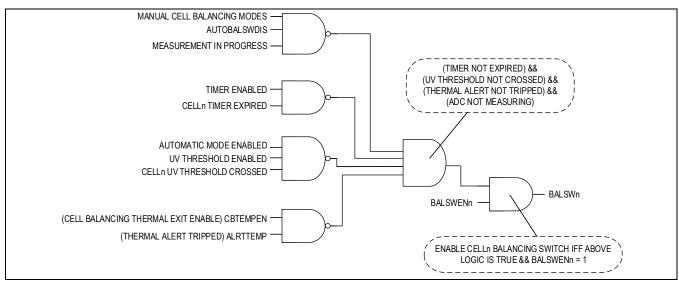

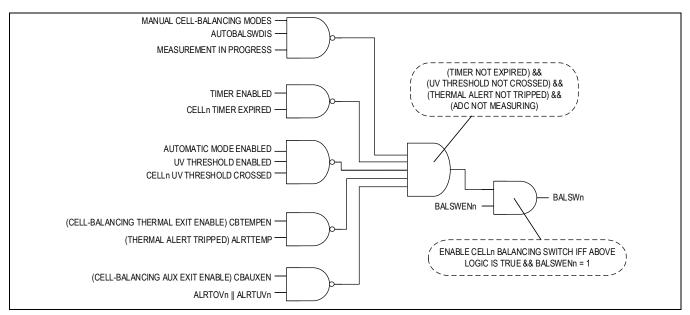

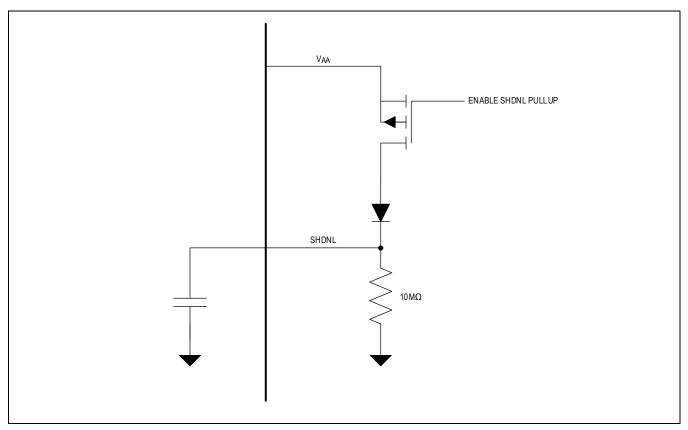

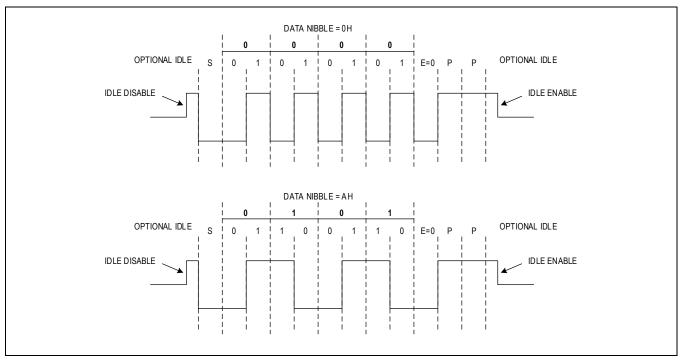

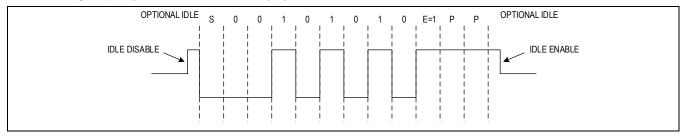

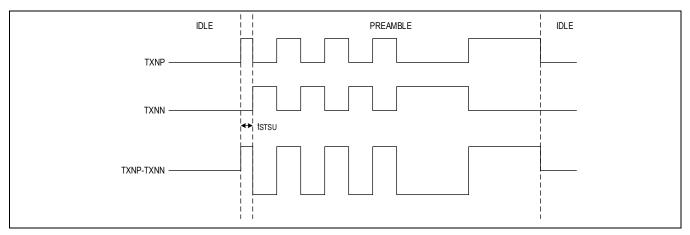

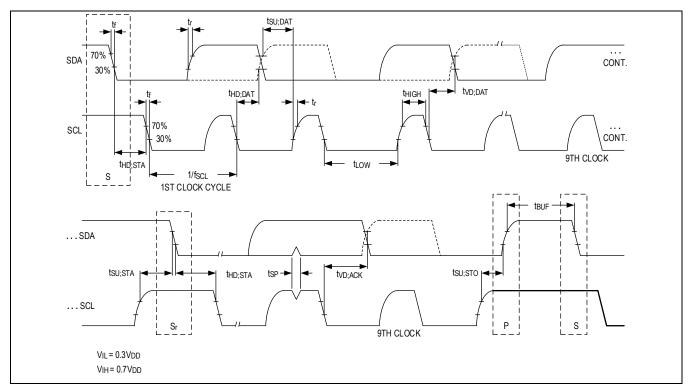

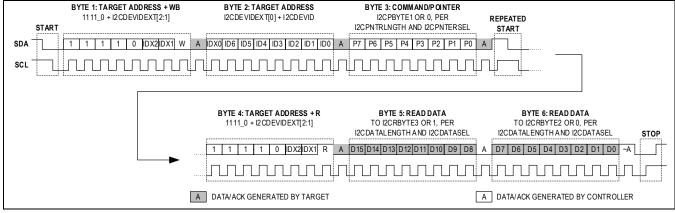

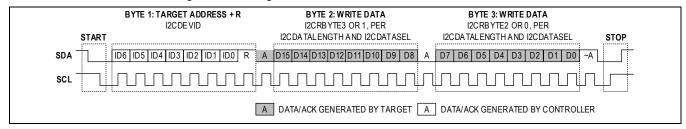

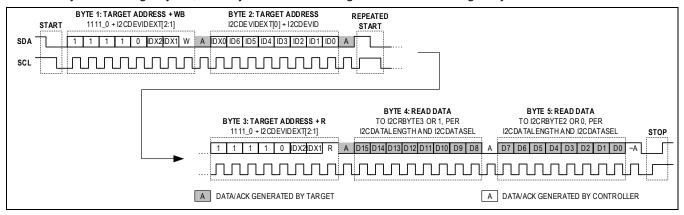

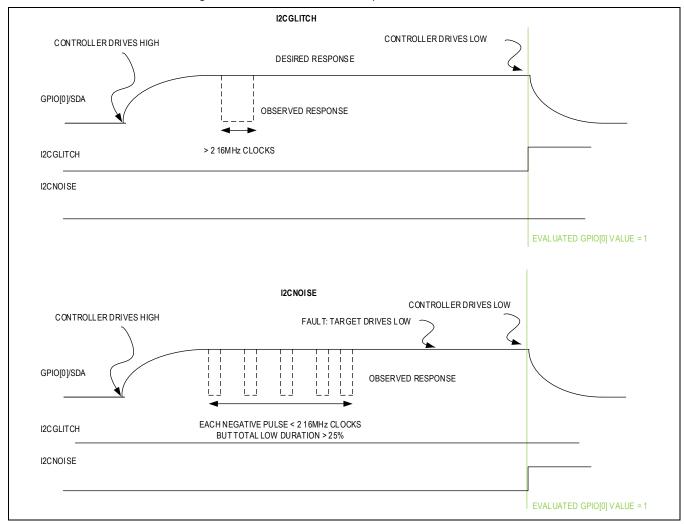

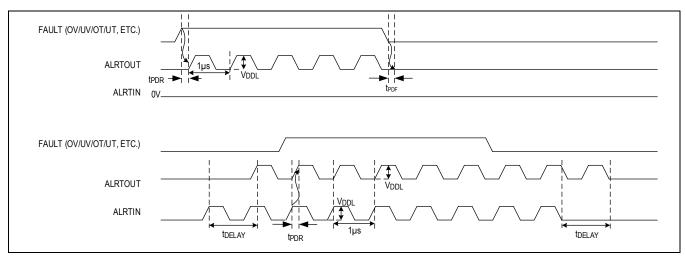

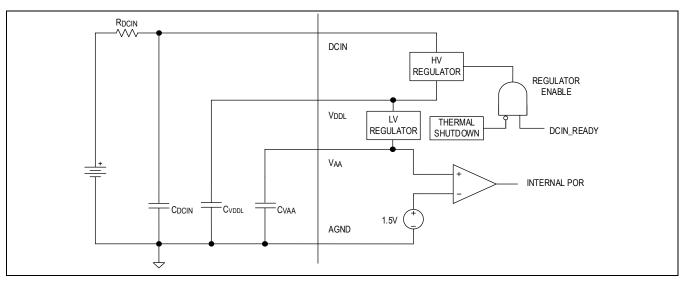

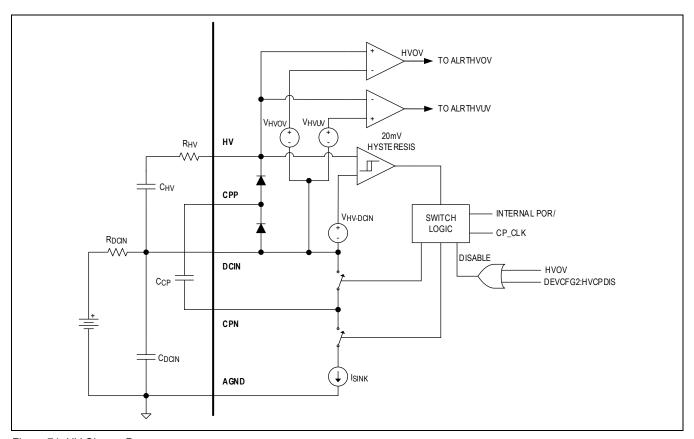

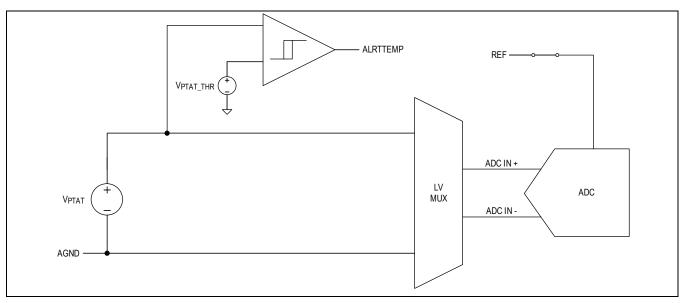

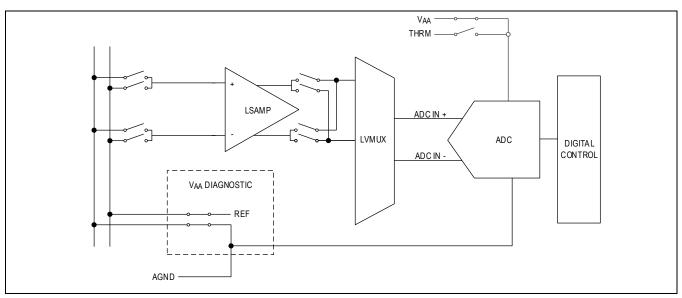

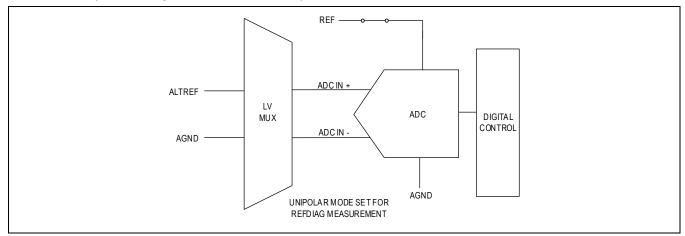

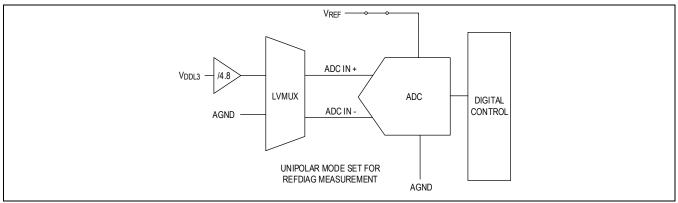

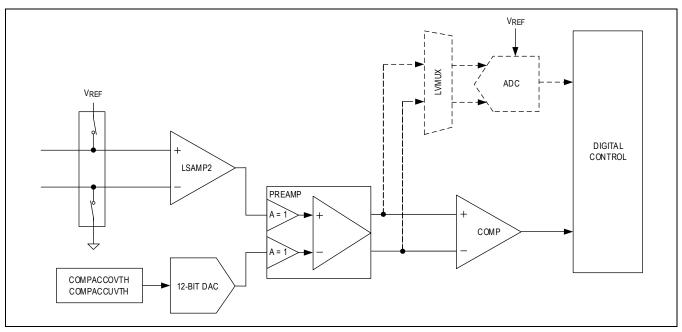

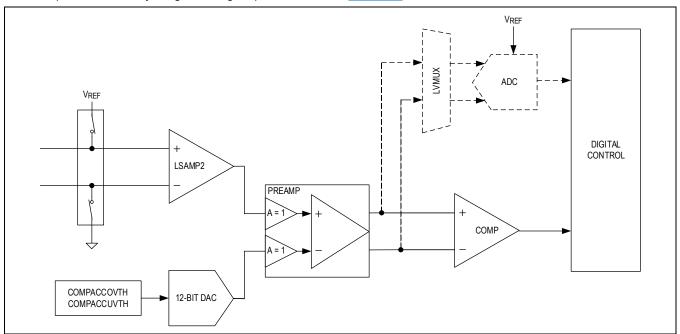

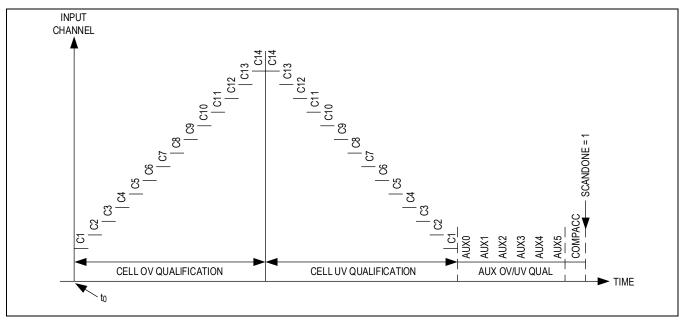

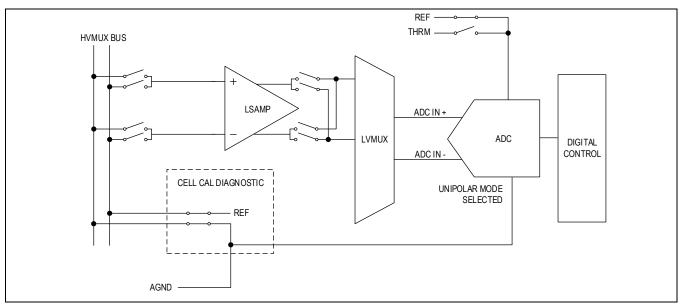

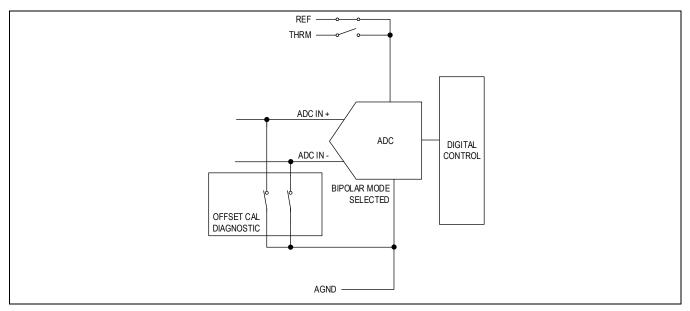

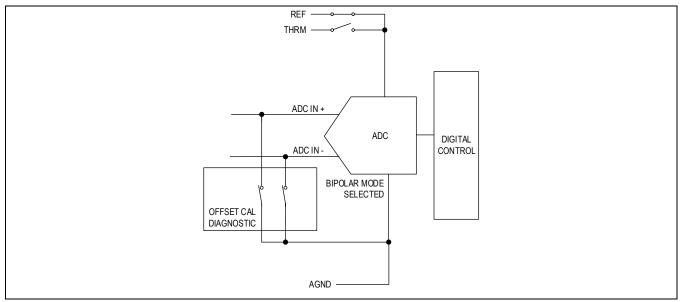

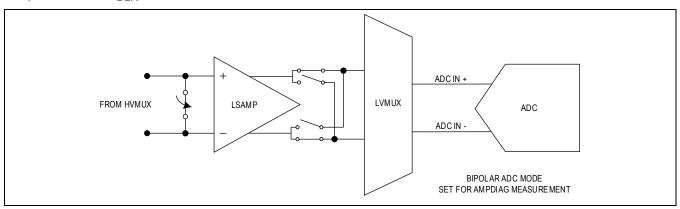

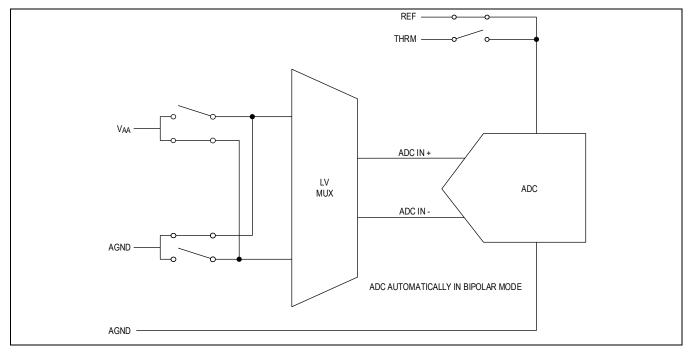

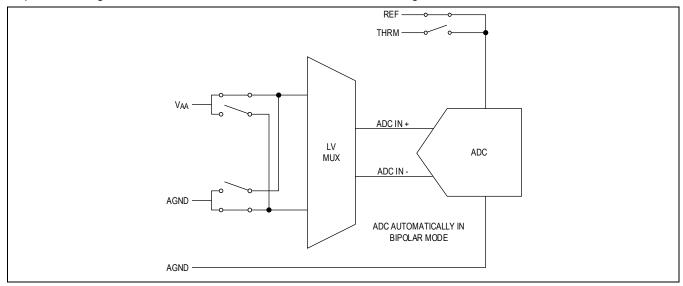

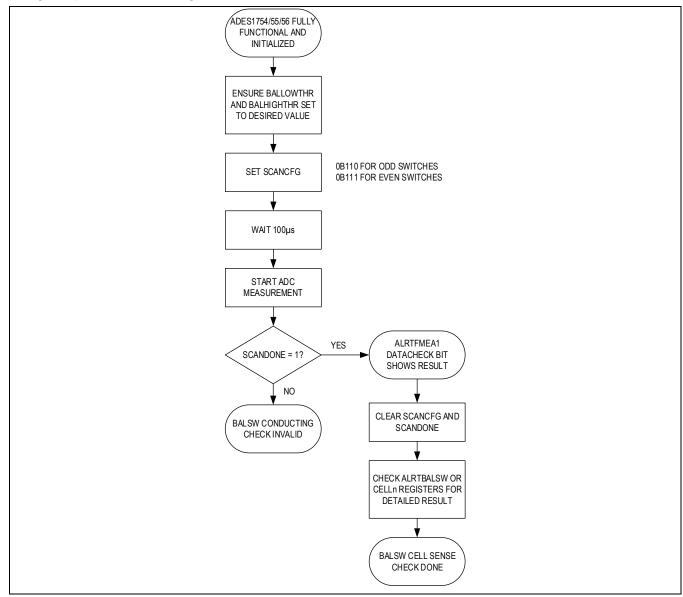

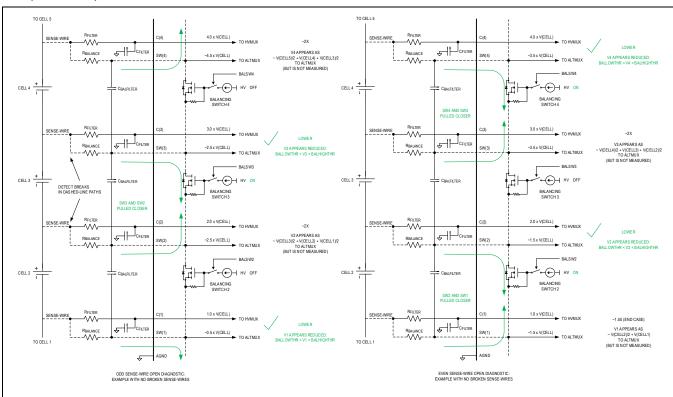

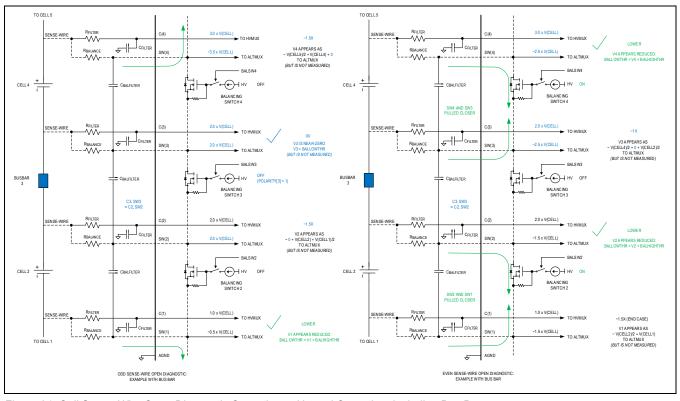

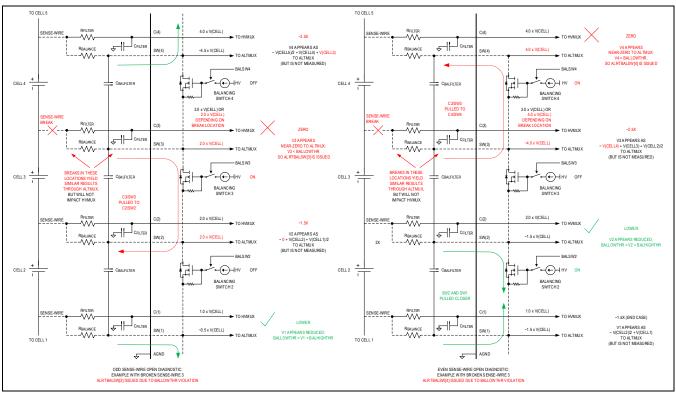

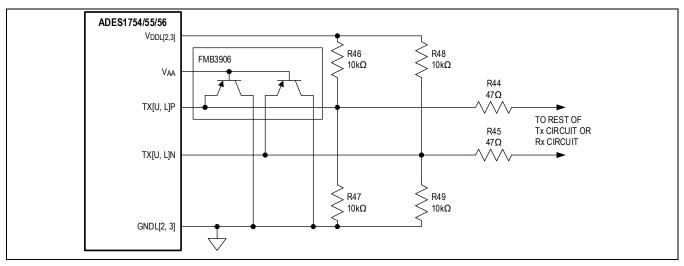

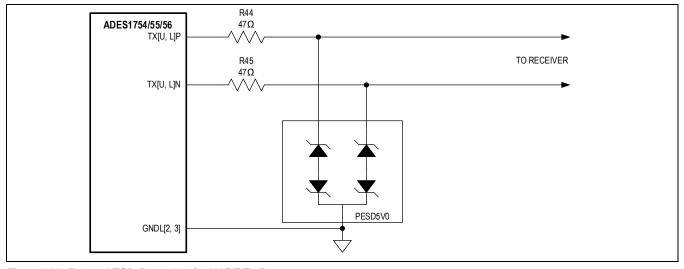

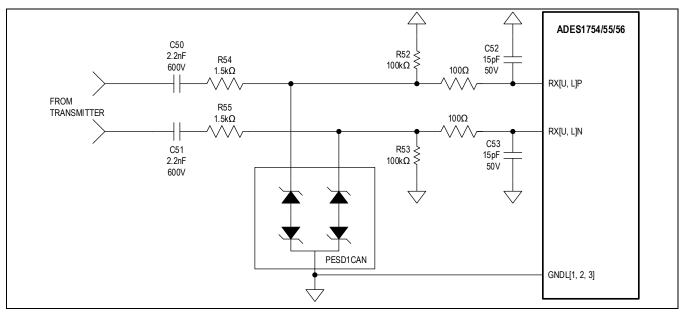

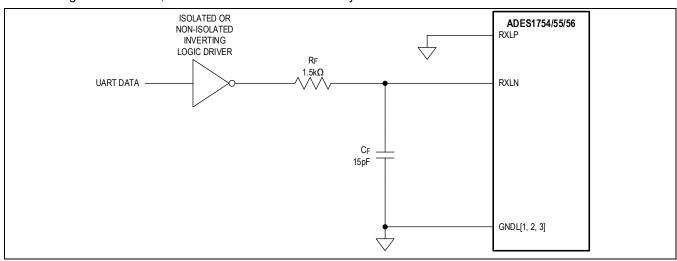

|------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------|--------------------------|------|--------------------------|----------------------------|